Elettronica applicata e misure

Lezione D5

Gruppo lezioni D5

!

Condizionamento del segnale

!

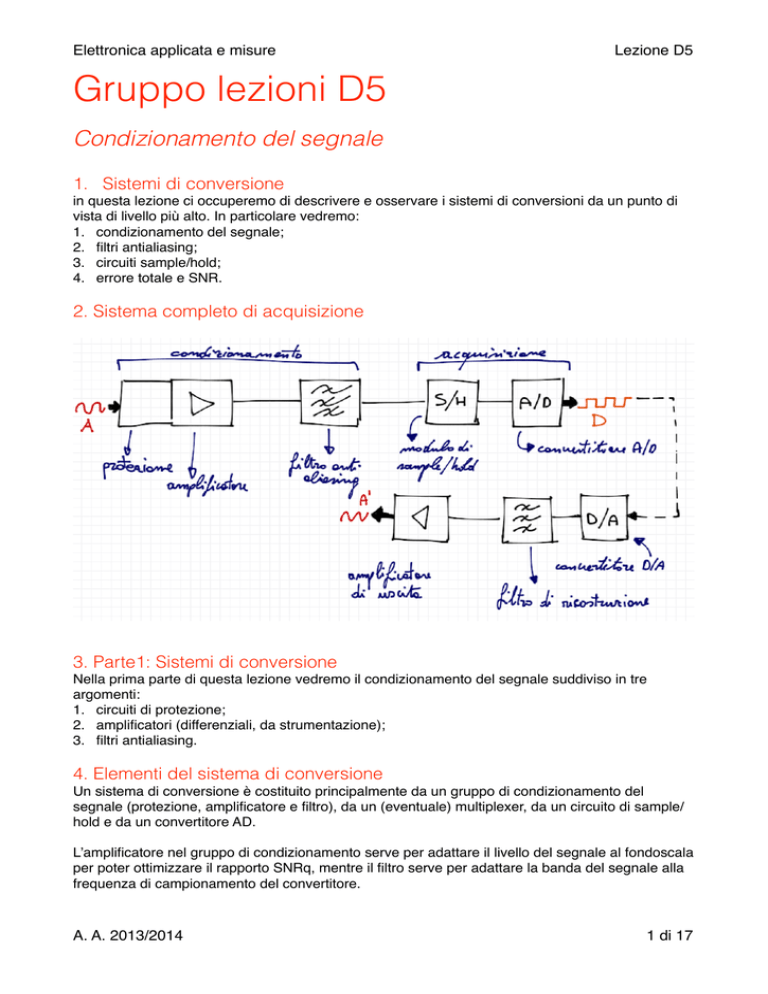

1. Sistemi di conversione

in questa lezione ci occuperemo di descrivere e osservare i sistemi di conversioni da un punto di

vista di livello più alto. In particolare vedremo:!

1. condizionamento del segnale;!

2. filtri antialiasing;!

3. circuiti sample/hold;!

4. errore totale e SNR.!

!

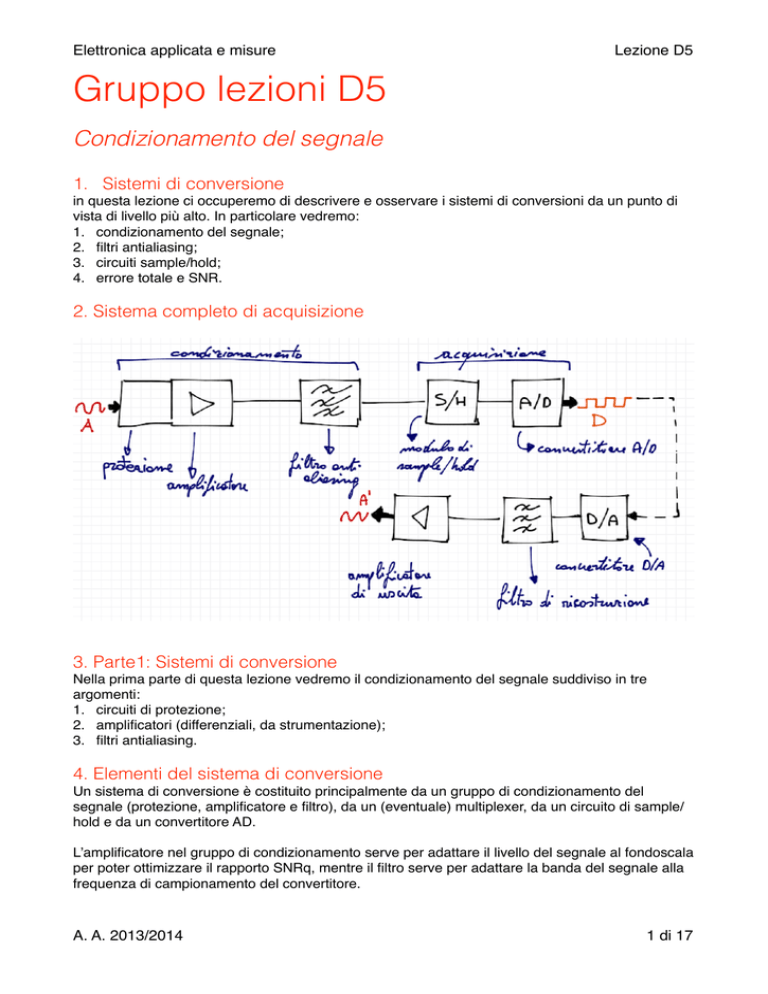

2. Sistema completo di acquisizione

!

3. Parte1: Sistemi di conversione

Nella prima parte di questa lezione vedremo il condizionamento del segnale suddiviso in tre

argomenti:!

1. circuiti di protezione;!

2. amplificatori (differenziali, da strumentazione);!

3. filtri antialiasing.!

!

4. Elementi del sistema di conversione

Un sistema di conversione è costituito principalmente da un gruppo di condizionamento del

segnale (protezione, amplificatore e filtro), da un (eventuale) multiplexer, da un circuito di sample/

hold e da un convertitore AD.!

!

L’amplificatore nel gruppo di condizionamento serve per adattare il livello del segnale al fondoscala

per poter ottimizzare il rapporto SNRq, mentre il filtro serve per adattare la banda del segnale alla

frequenza di campionamento del convertitore.!

!

!

A. A. 2013/2014

1 di 17

Elettronica applicata e misure

Lezione D5

5. Circuiti di protezione

Per quel che riguarda i circuiti di protezione, si può dire che sono le componenti che si trovano in

ingresso ad un sistema di conversione e sono quelli che per primi ricevono il segnale di ingresso.

Inoltre non bisogna dimenticare che il segnale estero (campo) è soggetto a cariche statiche,

disturbi elettromagnetici, rumori, contatti accidentali e molto altro ancora. Queste problematiche

influiscono negativamente sull’intero lavoro del convertitore quindi si ha la necessità di

“proteggere” tale sistema da queste problematiche: questa funzione di protezione è svolta dai

circuiti di protezione posti in ingresso. Tali circuiti di protezione pongono dei limiti usuali al segnale

di ingresso: un segnale troppo alto può danneggiare il sistema; solitamente tali limiti di protezioni

sono compresi tra gli intervalli di alimentazione.!

!

Le tipologie di circuiti di protezione sono varie, per esempio si hanno:!

1. clamp a diodi verso massa e alimentazione;!

2. diodi Zener;!

3. componenti speciali (varsistori, …).!

!

6. Circuiti limitatori di ampiezza

!

Questo è un esempio di circuito di protezione che usa la tecnica dei due

diodi di clamp. La VOUT è limitata tra Val+ e Val-.!

!

!

!

Questo è invece un circuito di protezione basato sui diodi Zener verso

massa. La VOUT è limitata alla VZ.!

!

!

Questo sciema mostra che nel modulo Z può trovarsi uno speciale

dispositivo di protezione, la VOUT è limitata dalla V(I) di Z.!

!

!

!

!

In tutti i circuiti la resistenza R limita la corrente di ingresso durante l’intervento della protezione.!

!

7. Condizionamento del segnale

Il convertitore AD può avere diversi tipi di ingresso:!

1. tensione o corrente;!

2. riferito a massa o differenziale.!

Per adattare il segnale di ingresso all’AD come dinamica e come dito di segnale, si inserisce un

amplificatore di condizionamento.!

!

Esistono diversi tipi di amplificatori, se ne citano qui tre:!

1. amplificatore V/V o I/I o convertitore V -> I o I -> V;!

2. ingresso single-ended o differenziale;!

3. uscita single-ended o differenziale.!

!

!

!

!

!

!

!

!

A. A. 2013/2014

2 di 17

Elettronica applicata e misure

Lezione D5

8. Amplificatore di tensione

!

La figura qui a fianco rappresenta

un amplificatore di tensione disposto

in configurazione single ended.

L’amplificatore operazionale è

reazionato. Ad alta impedenza la

tensione AV non dipende dalla

resistenza RS. Per una bassa

resistenza di uscita il termine AV

dipende sempre meno dalla

resistenza del carico RC.!

9. Segnali single-ended e differenziali

!

!

!

!

!

!

!

!

!

!

!

Qui vengono confrontate le due tecniche: in

alto è quella single endend in basso è

raffigurata la configurazione a segnale

differenziale.!

10. Segnali differenziali

!

!

!

!

!

!

!

!

!

!

!

!

!

!

!

!

!

!

I segnali differenziali sono molto più protetti dai disturbi rispetto ai segnali single ended. Alcuni

trasduttori forniscono segnali differenziali. I convertitori AD che sono molto veloci o molto precisi

(ovvero i convertitori AD ad elevate prestazioni) operano direttamente sui segnali differenziali. I

convertitori di tipo comune o standard trattano solo segnali di tipo single ended. I segnali

differenziali allora dovrebbero essere adeguatamente trattati. Si utilizzano convertitori single ended

o differenziali, amplificatori differenziali e amplificatori da strumentazione.!

!

A. A. 2013/2014

3 di 17

Elettronica applicata e misure

Lezione D5

11. Reiezione del modo comune (CMRR)

È quel rapporto tra AD e AC già visto nel corso di Sistemi e tecnologie elettroniche: AD/AC = CMRR

(Common Mode Reject Ratio); tale rapporto specifica quanto viene amplificato un segnale

differenziale rispetto a quelli di modo comune. È un parametro fondamentale in ambito di segnali

differenziali.!

!

Un amplificatore deve amplificare i segnali differenziali e attenuare i segnali di modo comune; in

altre parole, quando AD è alto, significa che l’amplificatore amplifica i segnali differenziali (buona

cosa) e quando AC è basso, significò che l’amplificatore non amplifica i segnali di modo comune

(buona cosa).!

!

12. Segnali differenziali e modo comune

!

!

!

!

!

!

!

!

!

!

!

!

!

!

!

!

!

Le relazioni che descrivono il circuito qui sopra rappresentato sono le seguenti:!

!

!

!

!

!

!

!

!

!

!

!

!

In un amplificatore differenziale (come già visto nel corso di Sistemi e tecnologie elettroniche) il

termine relativo al guadagno di modo comune AC è nullo, quindi A1 = A2.!

!

!

!

!

!

!

!

!

!

!

!

A. A. 2013/2014

4 di 17

Elettronica applicata e misure

13. Amplificatore differenziale

Lezione D5

!

Le resistenze del

circuito

rappresentato qui a

fianco sono correlate

secondo la seguente

equazione:!

!

R / R = R / R .!

!

3

1

4

2

Inoltre, come già

detto prima:!

!

A

!

C

= Vu / Vc = 0!

cioè il guadagna di

modo comune è

nullo. Inoltre il

guadagno

differenziale AD è definito da:!

!

A = V / V = -R / R !

!

(cioè il circuito amplifica solamente i segnali differenziali.!

!

D

u

D

3

1

14. Problemi nel differenziale classico

Nella struttura dell’amplificatore differenziale classico sono

presenti alcune problematiche. La asimmetria nella Zl1 trasforma

il segnale di modo comune VC in un segnale di tipo differenziale,

in questo modo viene a peggiorarsi la reiezione del modo comune

(CMRR). Inoltre:!

!

!

!

A. A. 2013/2014

5 di 17

Elettronica applicata e misure

Lezione D5

15. Simmetrizzazione con il Voltage Follower

Questa asimmetria è la causa del basso CMRR descritto prima. Il termine CMRR dovrebbe essere

il più elevato possibile. Si può compensare l’effetto dell’asimmetria semplicemente cercando di

rendere simmetrico quel che è asimmetrico utilizzando un voltage follower sugli ingressi.!

I voltage follower sono i due amplificatori reazionari posti all’ingresso. In tal caso si ha:!

1. A = 1;!

2. una resistenza di ingresso Ri molto alta;!

3. una resistenza di uscita Ru molto bassa.!

!

L’impedenza Z è alta e uguale (simmetrica) su entrambi gli ingressi.!

!

16. Distribuzione del guadagno

!

l

L’obiettivo è quello di avere un guadagno complessivo di

un fattore pari a 100. Si deve sapere che ciascun

amplificatore ha un errore (in uscita) di circa Eu = 10 mV.

Quindi, l’errore totale è dato dalla seguente relazione:!

!

E =E

!

!

!

!

t

Quindi, per esempio:!

1 · 100: Et = 10 mV + 10 mV · 101!

10 · 10: Et = 10 mV + 10 mV · 10!

100 · 1: Et = 10 mV + 10 mV · 1!

u2

+ ( Eu1 · A2 )!

= 1.01 V!

= 110 mV!

= 10 mV!

!

Dal precedente esempio ci si evince che conviene assegnare il guadagno allo stadio iniziale.!

!

!

!

!

!

A. A. 2013/2014

6 di 17

Elettronica applicata e misure

Lezione D5

!

!

!

!

!

17. Amplificatore da strumentazione

!

Queste sono le relazioni che descrivono il circuito disegnato qui sopra.!

!

!

!

!

!

!

!

!

!

!

Questa relazione esprima

la tensione di uscita.!

18. Filtro anti-aliasing

!

!

!

!

!

!

!

Ogni segnale ha una banda nominale, ma confine e anche componenti fuori banda. Questo

significa che, anche campionando con una frequenza più che doppia rispetto alla banda nominale,

i segnali che si trovano fuori dalla banda (nominale) vengono riportanti in banda a causa di un

fenomeno noto come aliasing. Questa problematica causa un errore gravissimo che si chiama

errore di aliasing. Tale errore dipende dal comportamento del segnale fuori dalla banda e può

essere controllato utilizzando dei filtri appositi che vengono chiamati filtri anti aliasing. La

A. A. 2013/2014

7 di 17

Elettronica applicata e misure

Lezione D5

cadenza di campionamento influisce direttamente sul comportamento del fenomeno dell’aliasing:

quanto più la frequenza di campionamento è elevata, tanto meglio è, poiché si allontanano in

questo modo gli alias.!

!

19. Ribaltamento in banda del segnale

!

20. Rumore di aliasing

Per esempio, se:!

1. fB è la banda del segnale, più precisamente: è la banda filtrata dal filtro di ricostruzione e tale

banda è di 12 kHz;!

2. fS è la cadenza di campionamento e vale 50 ks/s;!

!

Il segnale di ingresso viene ribaltato nella banda utile da f - f a f e cioè da 38 kHz a 50 kHz.!

!

Nota: il rumore di aliasing viene a sommarsi con il rumore di quantizzazione.!

!

S

B

S

Ritornando al discorso dell'errore si noti che se si ha un errore di quantizzazione di ¼K e un errore

di campionamento pari a 1/100 è ridondante utilizzare tanti bit per ottimizzare il segnale. Tutti

questi bit aumentano inutilmente il costo di produzione perché ad esempio anche se si trovasse un

componente estremamente preciso sarà sprecato, dato che non potrà essere utilizzato

completamente: a monte si ha un errore di campionamento che è superiore all’errore di

quantizzazione.!

!

Nota: l'errore di quantizzazione è dato da (½)2 dove n rappresenta il numero di bit.!

A. A. 2013/2014

8 di 17

Elettronica applicata e misure

Lezione D5

21. Effetto del filtro anti-aliasing

Il rapporto segnale/rumore di aliasing è pari al valore di SNRA: l’ampiezza del segnale fuori banda

è uguale al segnale S. Le specifiche per il filtro anti aliasing sono le seguenti: attenuare SNRA dB

da fs - fB e non attenuare a fB.!

!

Da f

!

B

a fS - fB si ottiene la dinamica di (fS - fB) / fB.!

22. Esercizio D5.1: Dimensionamento del filtro

Si utilizzino i dati dell’esempio precedente:!

• fB = banda utile del segnale 12 kHz;!

• fS = cadenza di campionamento: 50 ks/s;!

• fS - fB: 38 kHz; dinamica: log10(38/12) = 0,5 decadi;!

• Attenuazione di ogni polo: Ap = 20 * 0,5 = 10 dB.!

!

Ulteriori specifiche del problema:!

• Conversione su 12 Bit: SNRq = 6N + 1,76 = 73,7 dB;!

• SNRA = 73,7 dB (come rumore di quantizzazione).!

!

Il numero di poli richiesto è P = SNRAA / Ap = 7,37 quindi sono necessari 8 poli.!

!

!

23. Parte 2: Multiplexer

Nella seconda parte di questa lezione vedremo i parametri che descrivono il multiplexer e

osserveremo gli errori che interessano tale dispositivo.!

!

24. I multiplexer

Grazie al multiplexer è possibile utilizzare le varie componenti del sistema (moduli di sample/hold e

convertitori AD) per più canali. Si utilizzano i multiplexer quando si deve selezionare un canale tra

più canali (N). Il segnale che passa attraverso il multiplexer non deve essere modificato e gli altri

segnali (quelli che non sono selezionati) devono essere completamente bloccati.!

!

I moduli di sample hold sono costosi. Quindi per

incanalare in modo efficiente più ingressi su un unico

modulo di sample hold si preferisce utilizzare un

multiplexer, invece di utilizzare tanti moduli di sample

hold quanti sono gli ingressi. !

!

!

!

!

!

I parametri che descrivono un multiplexer sono:!

1. RON e IOFF (resistenza di ingresso e corrente di uscita);!

2. isolamento/feedthrought;!

3. tempo di assetto.!

!

A. A. 2013/2014

9 di 17

Elettronica applicata e misure

Lezione D5

25. Sistema per più canali

!

26. Struttura del multiplexer

!

La struttura di base dei multiplexer è rappresentata

qui a fianco. Si tratta di un banco di interruttori

realizzato tramite transistori MOS. Un buon

multiplexer dovrebbe avere una resistenza di

ingresso molto bassa. Una delle soluzioni per

abbassare la resistenza di ingresso può essere

quella di utilizzare una coppia MOSp-MOSn per

ciascun interruttore.!

!

!

!

!

!

!

!

!

!

!

27. Errore dalla resistenza di ingresso RON

!

È importante sapere che per

definizione nei mutiplexer viene

chiuso un solo interruttore per

selezionare il canale VS di ingresso

da collegare all’uscita VU.!

!

!

!

!

!

!

!

A. A. 2013/2014

10 di 17

Elettronica applicata e misure

!

Lezione D5

!

!

L’interruttore chiuso ha una resistenza complessiva

(resistenza equivalente) che viene denotata come

resistenza di ingresso (il primo parametro: RON). Tra la

tensione in ingresso (VS) e la tensione di uscita VU si

forma un partitore con la resistenza del carico RL. Qui

a fianco è mostrato un modello basilare di questo

sistema partitore del multiplexer.!

!

Ron è la resistenza che simula il transistor come visto

nel corso di Sistemi ed tecnologie elettroniche.!

Per le applicazioni di questo genere vanno bene delle

resistenze pari a 10 ohm.!

!

!

!

28. Errore dalla corrente di uscita IOFF

!

!

Nel multiplexer viene chiuso un

solo interruttore (un solo SW) per

selezionare il canale VS di

ingresso da collegare in uscita

(ogni piedino a sinistra

rappresenta un segnale differente

dagli altri: il compito del

mutiplexer è quello di selezionare

uno solo di questi segnali e porli

nell’uscita. Il mutiplexer sa quello

che deve fare grazie a un

comando esterno e codificato).!

!

!

!

Ciascun interruttore aperto comporta una

perdita di corrente (il secondo parametro IOFF).

Cioè, la IOFF è caratteristica di ogni interruttore,

cioè non è una IOFF complessiva. Le IOFF

percorrono RL // (RON + RS) e generano un

offset VUOFF in uscita.!

!

Le correnti Ioff sono piccole, se tuttavia si

mettessero tanti interruttori aperti allora si

potrebbe avere una grossa perdita che è

proprio dovuta alla somma di tante correnti

molto piccole.!

!

!

!

!

!

!

!

A. A. 2013/2014

11 di 17

Elettronica applicata e misure

Lezione D5

29. Valori di RON e di IOFF

!

I valori ideali e più comuni per la RON sono:!

– MOS di potenza: [0÷1 ... 10] Ω;!

– MOS di segnale: [10 ... 1000] Ω;!

– MUX integrati: [1 ... 100] Ω.!

!

Mentre per le correnti di uscita IOFF sono: !

– a 25° C di temperatura si hanno [10 nA … 10 μA];!

– si moltiplica per un fattore pari a 10 per ogni 40° C di temperatura.!

!

Entrambe R

!

ON

e IOFF vengono specificate come valore massimo.!

30. Limiti di banda

!

Le capacità parassite del multiplexer e del

carico limitano la banda del segnale trasferito.!

!

Le due resistenze RS, RON e la capacità CP

formano una cella passa basso.!

!

!

!

!

!

!

!

!

Le capacità parassite dell’interruttore e quelle

tra i segnali di comando e di uscita causano

errori di piedistallo e feedthrought analoghi a

quello di un modulo di sample/hold.!

31. Parte 3: Modulo di sample/hold

!

!

!

!

!

!

!

!

!

!

!

!

!

Nella terza e ultima parte di questa lezione si parlerà del modulo di sample/hold: verranno descritti

i parametri relativi e si faranno alcuni circuiti di esempio.!

!

A. A. 2013/2014

12 di 17

Elettronica applicata e misure

Lezione D5

32. Il sample/hold

!

Il modulo di sample/hold è

necessario per il processe di

campionamento di un segnale

analogico I(t). Dutante il

campionamento, all’istante t = Ts, il

modulo S/H moltiplica I(t) per d(ds).!

!

Tale modulo serve a mantenere il

segnale presentato al convertitore

AD costante per la durata di

conversione; si esegue appunto un

mantenimento U(f) = I(ts).!

!

33. Track/hold

!

!

Nei circuiti reali il funzionamento del

modulo di sample hold è osservabile in

due fasi, separate dal campionamento:!

1. inseguimento (o tracking): U(t) = I(t)!

!

campionamento (o sampling) a t = ts!

!

2. mantenimento (o hold): U(t) = I(ts),

per tH < tS.!

34. Circuito base

!

!

!

!

!

!

!

!

!

!

!

!

Il sample hold è sostanzialmente una memoria di tipo

analogico costituita da uno switch. !

Quando SW = ON si esegue il tracking, quando SW = OFF

si esegue l’holding.!

!

!

!

!

!

!

!

!

!

!

A. A. 2013/2014

13 di 17

Elettronica applicata e misure

Lezione D5

35. Fasi e transizioni

Le principali fasi e transizioni, riassumendo, sono:!

1. Inseguimento (track): uscita eguale all’ingresso!

2. Campionamento (sample): da inseguimento a mantenimento (Track -> Hold)!

3. Mantenimento (hold): uscita costante, corrispondente all’ingresso campionato!

4. Acquisizione: da mantenimento a inseguimento (Hold -> Track).!

!

36, 37. Fase di inseguimento

In fase di tracking la tensione di uscita VU è pari a quella di ingresso VI. Cosìil modulo di SH

diventa un amplificatore (a guadagno unitario) e vengono introdotti vari errori statici e dinamici:!

• Errori statici:!

1. guadagno;!

2. corrente di offset;!

3. non linearità.!

• Errori dinamici:!

1. tempo di assetto (setting time);!

2. banda.!

!

La precisione complessiva di un modulo di sample hold dipende anche da questi parametri.!

!

!

I limiti di banda introducono un transitorio:!

!

!

!

tale transitorio influisce sul tempo di acquisizione del segnale.!

!

!

!

!

!

38. Campionamento

Si introducono ora gli errori in fase di

campionamento.!

!

Errore in tempo:!

• ritardo di apertura dello SW (da Track a

Hold);!

• sposta il reale campionamento;!

• jitter di apertura.!

!

Errore in ampiezza:!

• piedestallo.!

!

Transitorio:!

• tempo di assetto.!

!

!

!

!

!

!

!

39. Mantenimento

A. A. 2013/2014

14 di 17

Elettronica applicata e misure

Lezione D5

La carica sul condensatore non è costante, ma varia, per cui si ha un errore di decadimento.

Inoltre l’isolamento del segnale di ingresso non è perfetto, per cui si ha un errore di feedthrought.!

!

Polarizzazzione del dielettrico [FXR: cosa intende dire qui?]!

!

40. Acquisizione

!

!

!

!

!

!

!

!

!

!

!

L’uscita riprende l’ingresso (entro la precisione voluta) dopo il tempo di acquisizione TACQ:!

1. banda (risposta al transitorio);!

2. slew rate.!

!

41. Circuito base

[FXR: cosa spiega in questa slide?]!

!

!

!

!

!

!

!

!

!

!

Il circuito di base del modulo di sample hold è il seguente:!

!

Ad interruttore chiuso la tensione di uscita all’istante t è uguale alla tensione di ingresso all’istante

t, mentre ad interruttore aperto la tensione di uscita all’istante t è pari alla tensione di ingresso

all’istante ts, ovvero:!

• closed SW: VO(t) = VI(t);!

• open SW: VO(t) = VI(ts).!

!

!

!

!

42. Errore di guadagno

Tale figura rappresenta la partizione della tensione di ingresso VI tra RG e tra RL. Si ha un errore di

guadagno.!

!

!

!

!

!

!

!

A. A. 2013/2014

15 di 17

Elettronica applicata e misure

Lezione D5

43. Errore di decadimento

In tale figura invece è rappresentato l’errore di

decadimento in fase di scarica del condensatore su RL.!

!

!

!

!

!

44. Ritardo di acquisizione

Qui è rappresentata la carica del condensatore

attraverso Rg. (tempo di acquisizione).!

!

!

!

!

45. Isolamento di generatore e carico

L’utilizzo di due voltage follower isolano il generatore e il carico. In figura è rappresentato

l’interruttore flottante, si tratta di un comando più complesso e si ha un maggiore feedthrought e un

effetto di piedistallo più grave. Inoltre si ha un accumulo degli errori di offset e di guadagno: ci sono

troppe problematiche, si deve cercare di trasformare il tutto in un unico voltage follower.!

!

!

!

!

!

!

!

46. Maglia software - Cm

La maglia di SW è un’ottima soluzione e viene realizzata

tramite transistori MOS- Le capacità parassite del MOS

formano partitori capacitivi con la capacità di memoria

(indicata con CM) pari a:!

1.VI-VO = feedthorught;!

2.VG-VO = piedistallo.!

!

!

!

!

!

!

!

!

!

47. Errori di piedistallo e feedthrought

L’errore di feedthorught è un errore che si genera dalla partizione della tensione di ingresso tra la

capacità parassita CDDS e CM.!

!

L’errore di piedistallo è un errore che si generare dalla partizione della tensione VG tra la capacità

parassita CGD e CM.!

!

L’errore di decadimento viene causato dalla scarica graduale della capacità CM sul carico e dalle

perdite dell’interruttore.!

!

A. A. 2013/2014

16 di 17

Elettronica applicata e misure

Lezione D5

Nota: aumentando il valore di CM diminuiscono gli errori, tuttavia viene ad allungarsi il tempo di

acquisizione TACQ.!

!

48. Jitter di campionamento

Il passaggio al modulo di SH avviene con un ritardo di apertura (TA) rispetto a TS. Il tempo di

apertura TA è affetto da un rumore chiamato jitter di campionamento (o TJ). Tale jitter produce

errore sul segnale (rumore), pari alla variazione del segnale in TJ. L’errore in ampiezza dovuto al

jitter di campionamento ΔV + uguale a ΔT · slewRate, ovvero ΔV = SR · TJ.!

!

Il rapporto SNRJ rappresenta il rapporto segnale/rumore dovuto al jitter di campionamento.!

!

49. SNR totale

SNRTOT dipende dalla somma di vari termini:!

1. rumore di quantizzazione (num bit);!

2. rumore di aliasing (Fs e filtro);!

3. errore di jitter (jitter di apertura S/H e SR segnale);!

4. errori della catena di condizionamento (offset,

guadagno);!

5. altri errori… .!

!

L’errore totale viene calcolato come somma di termini

statisticamente indipendenti (Ai).!

!

!

50. Numero effettivo di bit: ENOB

L’errore totale viene espresso dal parametro ENOB (Effective Number Of Bits). Tale parametro si

ricava a partire da SNRTOT calcolato o misurato sul sistema d’acquisizione con un segnale

sinusoidale di ampiezza pari al fondo scala (S) in ingresso. Con il parametro ENOB si tiene conto

del rumore totale SNRTOT (quantizzazione, aliasing, jitter di campionamento, …) ed è ricavabile

invertendo la relazione SNRq = (6 N + 1,76) dB -> ENOB = (SNRTOT -1,76)/6 = SNRTOT /6-0,3!

!

Si ricordi che ENOB rappresenta il numero effettivo di bit significativi per il convertitore in esame.!

!

51. Test finale

• Cosa occorre per adattare un segnale bipolare di 10 Vpp a un convertitore A/D con dinamica 0 5 V?!

• Come si può ridurre il rumore di aliasing?!

• Perchè sono preferibili segnali differenziali?!

• Quali errori introduce il multiplexer?!

• Come si può mettere in relazione l’errore dovuto al jitter di campionamento con la frequenza del

segnale?!

• Quali errori introduce il modulo S/H?!

• Quali parametri del S/H definiscono la banda del segnale che può essere campionato

correttamente?!

• Quali vantaggi e quali inconvenienti porta aumentare la capacità di mantenimento di un S/H?!

A. A. 2013/2014

17 di 17