Circuiti logici sequenziali

I circuiti logici possono essere classificati in circuiti combinatori, nei quali l’uscita in un determinato

istante dipende solo dal valore degli ingressi nello staesso istante, e circuiti sequenziali, nei quali

l’uscita in un certo istante dipende non solo dagli ingressi in quell’istante, ma anche dallo stato

precedente delle uscite. I circuiti sequenziali sono quindi caratterizzati dal fatto di possedere memoria.

Elementi fondamentali dei circuiti sequenziali sono i circuiti bistabili.

Circuiti bistabili

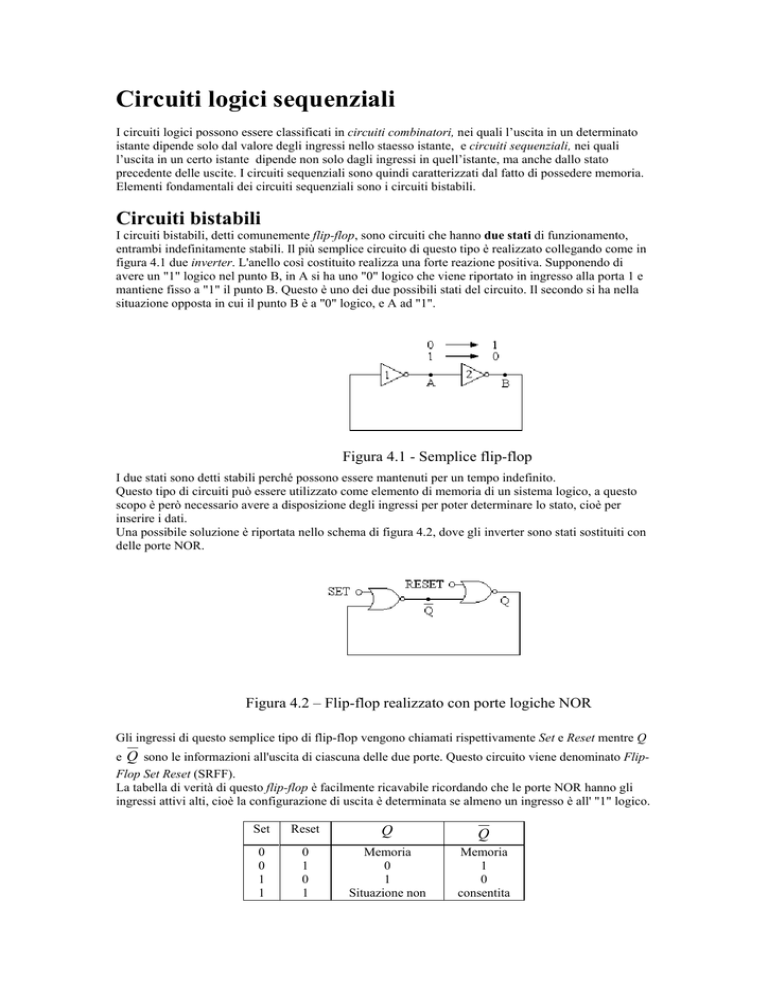

I circuiti bistabili, detti comunemente flip-flop, sono circuiti che hanno due stati di funzionamento,

entrambi indefinitamente stabili. Il più semplice circuito di questo tipo è realizzato collegando come in

figura 4.1 due inverter. L'anello così costituito realizza una forte reazione positiva. Supponendo di

avere un "1" logico nel punto B, in A si ha uno "0" logico che viene riportato in ingresso alla porta 1 e

mantiene fisso a "1" il punto B. Questo è uno dei due possibili stati del circuito. Il secondo si ha nella

situazione opposta in cui il punto B è a "0" logico, e A ad "1".

Figura 4.1 - Semplice flip-flop

I due stati sono detti stabili perché possono essere mantenuti per un tempo indefinito.

Questo tipo di circuiti può essere utilizzato come elemento di memoria di un sistema logico, a questo

scopo è però necessario avere a disposizione degli ingressi per poter determinare lo stato, cioè per

inserire i dati.

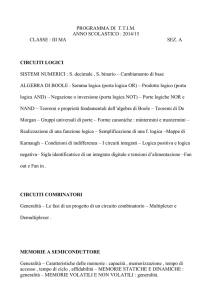

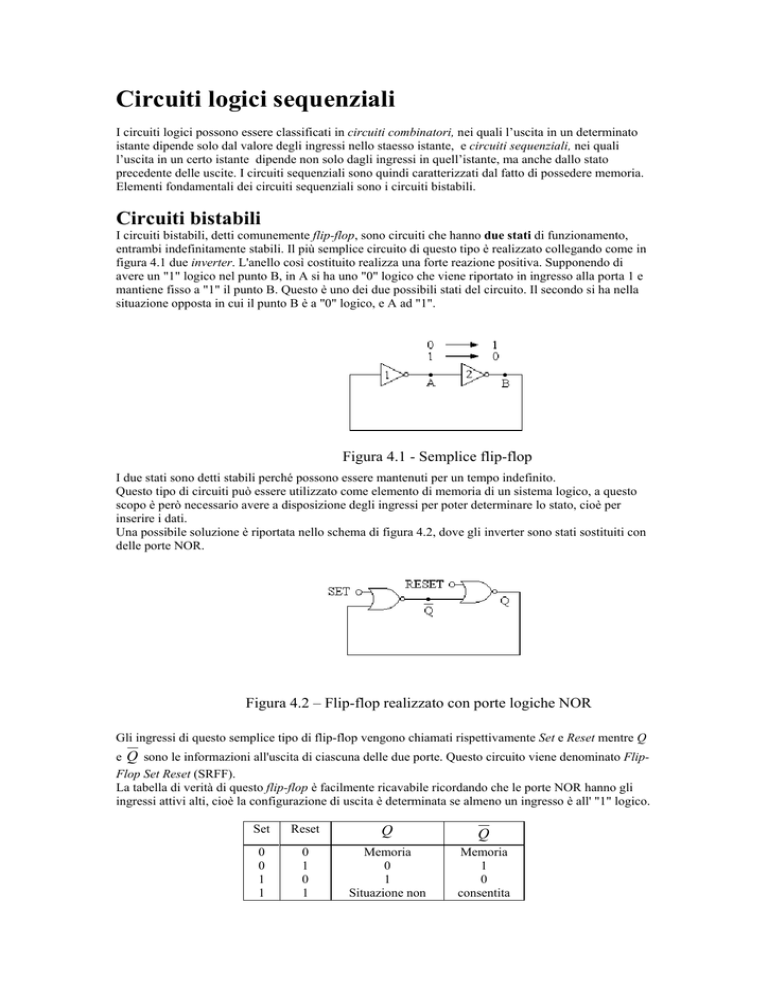

Una possibile soluzione è riportata nello schema di figura 4.2, dove gli inverter sono stati sostituiti con

delle porte NOR.

Figura 4.2 – Flip-flop realizzato con porte logiche NOR

Gli ingressi di questo semplice tipo di flip-flop vengono chiamati rispettivamente Set e Reset mentre Q

e Q sono le informazioni all'uscita di ciascuna delle due porte. Questo circuito viene denominato FlipFlop Set Reset (SRFF).

La tabella di verità di questo flip-flop è facilmente ricavabile ricordando che le porte NOR hanno gli

ingressi attivi alti, cioè la configurazione di uscita è determinata se almeno un ingresso è all' "1" logico.

Set

Reset

Q

Q

0

0

1

1

0

1

0

1

Memoria

0

1

Situazione non

Memoria

1

0

consentita

La seconda e la terza configurazione di ingresso consentono di determinare lo stato sulle uscite del FF,

e quindi di inserire l'informazione. La combinazione "0""0" su ingressi che sono “attivi alti”, non può

determinare lo stato delle uscite, e quindi lascia inalterata la situazione precedente: è quindi la

combinazione di memoria con la quale il circuito mantiene l'informazione precedentemente inserita. Se

gli ingressi sono entrambi a "1" le uscite vanno entrambe a "0" e questo in genere non è accettabile:

infatti se da questa combinazione si passa alla situazione di memoria le uscite possono portarsi alla

configurazione "0"/"1" oppure "1"/"0" in modo pressoché casuale (il verificarsi di una delle due

situazioni dipende da quale dei due ingressi passa per primo allo "0" logico e dalla rapidità relativa

delle due porte). Poiché in genere non è accettabile che nell'evolvere per stati di un sistema logico si

introduca un elemento stocastico, per cui non si sappia predire lo stato dell'uscita, si deve evitare di

fornire in ingresso la configurazione S = R = "1".

5.1.1 Comportamento di un flip-flop Set Reset

In figura 4.3 è riportato il circuito di un flip-flop a porte NOR. Cerchiamo di analizzarne il

comportamento.

Le forme d'onda di figura 4.4 riportano i segnali d'ingresso (S e R) ed una delle uscite (Q). La

configurazione S = "1", R = "0" forza l'uscita a "1" (fare riferimento alla tabella di verità prima

riportata); quando S torna a "0" il flip-flop si trova nello stato di memoria e Q non cambia, si noti come

commutazioni successive di S non hanno effetto sull'uscita. Per portare l'uscita a "0" occorre attivare il

segnale di reset (R = "1"). Anche in questo caso, mantenendo S a "0", le variazioni di R non influiscono

sul valore di Q.

Figura 4.3 – Flip-flop realizzato con porte logiche NOR

Figura 4.4 – Esempio di funzionamento di un flip-flop

I flip-flop possono essere realizzati anche utilizzando delle porte NAND al posto delle NOR (figura

4.5), la tavola di verità è:

Figura 4.5 – Flip-flop realizzato con porte logiche NAND

S

R

Q

Q

0

0

1

1

0

1

0

1

Situazione non

1

0

Memoria

consentita

0

1

Memoria

Dall'esame comparativo delle tavole della verità si può notare come il funzionamento del FF di NAND

sia ricavabile da quello del FF di NOR complementando gli ingressi. Questo spiega la figura 4.6 dove

Figura 4.6 – Simboli utilizzati per i flip-flop con porte logiche NOR (a) e porte logiche NAND (b)

sono riportati i simboli utilizzati per rappresentare i due tipi di flip-flop sopra descritti, il simbolo(a) si

riferisce a quelli realizzati con porte NOR, mentre quello (b) si riferisce ai flip-flop a porte NAND.

Questi semplici flip-flop Set Reset sono impiegati come circuiti antirimbalzo per collegare degli

interruttori meccanici a dei circuiti logici. Infatti, un interruttore meccanico quando chiude un circuito,

a causa dell'elasticità del materiale con cui sono realizzati i contatti, soffre di rimbalzi meccanici che

fanno chiudere ed aprire il contatto più volte prima di raggiungere la situazione di regime. Questo

potrebbe essere letto dal circuito logico comandato dal contatto come una ripetizione voluta di

comandi, e non come un unico dato in ingresso. Interponendo tra interruttore e sistema logico un RSFF,

come abbiamo visto in precedenza, le commutazioni multiple sugli ingressi non si ripercuotono sulle

uscite e i rimbalzi meccanici non danno origine a comandi non voluti al sistema logico che segue.

4.1.1 Altri tipi di flip-flop

Esistono diversi tipi di flip-flop: spesso si vuole che le commutazioni vengano comandate dai segnali S

e R, ma anche che possano avvenire solo in corrispondenza con un segnale di temporizzazione. In

figura 4.8 è riportato un flip-flop che può commutare solo se il segnale di clock (CP) è a livello alto

(esistono anche flip-flop abilitati da segnali a livello basso). Per CP allo "0", le uscite delle porte AND

si portano entrambi all'"0" e il FF rimane nello stato di memoria.

Figura 4.8 – Flip –Flop abilitato da un segnale di temporizzazione.

Nel circuito di figura 4.9 è stata introdotta una modifica che elimina la possibilità di dare in ingresso la

configurazione “proibita” S = R = "1". Questo circuito, detto flip-flop latch, quando CP è a livello alto

copia sull'uscita il dato posto in ingresso (D); quando il clock torna a livello basso il circuito si trova

nello stato di memoria, eventuali variazioni dell'ingresso in questa condizione non hanno effetto.

Figura 4.9 – Latch D

Questo tipo di flip-flop viene impiegato come elemento di memoria. Un insieme di questi circuiti

integrati nello stesso package forma quello che viene chiamato registro e può essere usato per

memorizzare una parola composta da diversi bit (ad es. 8,16).

Il latch appena descritto può commutare per tutto il tempo in cui il segnale CP si mantiene a livello

alto.

Nei sistemi regolati da un segnale di temporizzazione si vuole che le commutazioni avvengano solo in

corrispondenza di una transizione (fronte) specifica del clock e non durante tutto il tempo in cui il clock

rimane ad un dato livello. I flip-flop con queste caratteristiche vengono detti flip-flop cadenzati e

vengono rappresentati con il simbolo di figura 4.10.

In seguito è riportata la tavola di verità di un flip-flop cadenzato attivo sul fronte di salita del clock

D

CP

Q

Q

0

0

1

1

↑

↑

1

0

X

0,1

Memoria

Memoria

Figura 4.10 – Simbolo del flip-flop cadenzato

e nella figura 4.11 è riportato a titolo di esempio un diagramma di temporizzazione.

Fig. 4.11 – Esempio di funzionamento di un latch

Un flip flop cadenzato puo’ memorizzare l’informazione di un bit, per memorizzare un’intera parola

costituita da n bit occorrono n flip flop. Un insieme di n flip flop per memorizzare parole di n bit viene

detto Registro di n bit .

Memorie a semiconduttore

Le memorie a semiconduttori sono dispositivi elettronici in grado di conservare nel tempo dati sotto

forma binaria. Rispetto alle memorie di massa su supporto magnetico le memorie a semiconduttore

presentano tempi di accesso alle informazioni immagazzinate estremamente più brevi

Una prima classificazione delle memorie può essere effettuata sulla base del tipo di accesso, cioè della

modalità con la quale si può raggiungere la posizione di memoria desiderata. Si può distinguere tra:

• MEMORIE AD ACCESSO IMPLICITO: L'indirizzo del dato è determinato da quello del dato

precedente. E' il tipo di accesso proprio delle memorie seriali, per le quali si può accedere ad una

determinata cella di memoria solo se sono già state visitate in sequenza le celle precedenti (es.

nastro magnetico). Quelle a semiconduttore sono costituite da una serie di flip-flop collegati in

cascata (registri a scorrimento).

• MEMORIE ASSOCIATIVE: la memoria è organizzata in funzione del proprio contenuto, la

realizzazione è molto complessa, e la loro descrizione esula dagli scopi del presente corso.

• MEMORIE AD ACCESSO CASUALE: si accede direttamente alla cella di memoria di interesse

specificandone l'indirizzo.

Un ulteriore modo di classificazione delle memorie è rappresentato dalla modalità d'impiego; in tal

senso le memorie a semiconduttore vengono suddivise in due categorie:

• Memorie a sola lettura (ROM Read Only Memory,): in esse il contenuto può essere scritto una

sola volta e nel seguito viene soltanto letto. Si dividono in varie famiglie:

A. ROM vere e proprie: i dati sono immagazzinati dal costruttore una volta per tutte all'atto della

fabbricazione del componente e non possono più essere modificati.

B. PROM (Programmable ROM): la memorizzazione dei dati viene effettuata dall’acquirente una

volta per sempre, dopo l'acquisto del chip, facendo ricorso ad apposite apparecchiature.

C. EPROM (Erasable PROM), sono memorie PROM che possono essere cancellate e riprogrammate

un numero limitato di volte in quanto ad ogni cancellazione si ha un piccolo danneggiamento. La

cancellazione avviene esponendo il chip a raggi ultravioletti. Stanno scomparendo sostituite dalle

EEPROM :

D. EEPROM (Electrical EPROM), memorie in cui la fase di scrittura e di cancellazione avviene per

via elettrica. Non possono però essere considerate memorie di lettura e scrittura in quanto la

cancellazione e la scrittura richiedono tempi lunghi e tensioni apposite. Tra queste sono

identificabili le memorie FLASH, in cui la cancellazione può avvenire non bit per bit ma solo a

blocchi di dimensioni prefissate (sono le memorie usate nelle macchine fotografiche, penne USB

ecc.). Possono essere cancellate e riscritte da 10000 volte a 1 milione di volte.

• Memorie di lettura e scrittura RW (Read-Write), in genere ad accesso casuale, e quindi RWRAM (Random Access Memory). Possono essere divise in:

A. RAM volatili, perdono il proprio contenuto in assenza di alimentazione

B. RAM permanenti, in assenza di tensione di alimentazione sono in grado di conservare le

informazioni per un tempo sufficientemente lungo.

Le RW RAM possono essere anche suddivise in:

A. SRAM (RAM Statiche), in cui l'elemento di memoria è costituito da un flip-flop, sono in grado di

mantenere inalterato il contenuto di ogni cella di memoria per un tempo indefinito (a patto di non

togliere l'alimentazione, sono comunque memorie volatili);

B. DRAM (RAM Dinamiche), l'elemento di memoria è una capacità, il dato immagazzinato in una

cella si deteriora nel tempo in quanto la capacità si scarica, e si rendono necessarie delle periodiche

operazioni di ripristino del contenuto delle singole celle (operazione di rinfresco "refresh").

Organizzazione di una memoria RAM

Le memorie ad accesso casuale sono caratterizzate dall'avere una organizzazione a matrice, che può

essere schematizzata come in figura 5.1. Le celle di memoria contenenti il singolo bit sono individuate

nella struttura dalla riga e dalla colonna di appartenenza. Normalmente le informazioni sono

organizzate a parole di 4 bit, 8 bit (1 byte), 16 bit, ecc. Le linee orizzontali (word line) permettono di

individuare la parola, mentre quelle verticali (bit line) individuano il bit all'interno della parola.

Specificando l'indirizzo della parola che si intende leggere (o scrivere), il circuito di decodifica attiva la

relativa word line e i bit della parola selezionata (e solo loro) diventano accessibili (in parallelo) sui

piedini del chip mediante le bit lines.

Figura 5.1 – Organizzazione di una memoria RAM

Nella figura 5.2 è riportato lo schema della piedinatura tipica di una SRAM, dove sono indicate:

• linee di INDIRIZZO, permettono di selezionare una determinata parola della memoria, il numero

N

•

di queste linee dipende dall'estensione della memoria, con N linee si possono indirizzare 2

locazioni.

linee di DATI, vengono utilizzare per leggere e scrivere i dati in memoria.

•

linea R / W (Read/Write), è un ingresso per selezionare la lettura o la scrittura dei dati. Il simbolo

•

•

R / W indica che quando la linea è a livello alto i dati vengono letti, in caso contrario vengono

scritti.

linea CS (Chip Select), è un comando utilizzato per selezionare il singolo chip all'interno del

banco di memoria. Tipicamente un banco di memoria è formato da diversi circuiti integrati:

volendo accedere ad una locazione di memoria occorre specificare, oltre all'indirizzo, il chip sul

quale

si trova la locazione desiderata.

OutputEnable

linea,

consente di leggere o scrivere dati solo quando è attiva, quando è

disabilitata le linee dati sono sconnesse dal resto del circuito

(questa linea è necessaria perché il passaggio da un indirizzo di memoria ad un altro non avviene

istantaneamente e contemporaneamente su tutti i piedini).

Figura 5.2 – Piedinatura essenziale di una SRAM

Oltre a questa piedinatura essenziale occorrono anche altri piedini per i segnali di controllo e per il

segnale di clock.

5.2 PLD (Programmable Logic Devices)

Possono essere considerati dei particolari casi di memorie PROM. Si tratta di dispositivi integrati che

possono essere programmati per realizzare funzioni logiche anche molto complesse. Dai teoremi

dell'algebra binaria si ricava che qualunque funzione logica combinatoria tra più variabili è esprimibile

in forma canonica come somma di prodotti o come prodotto di somme

Es.:

f1 ( A, B, C , D ) = ABCD + ABC D

Ciascuno dei prodotti è implementabile con un circuito di tipo AND, la somma è realizzata con un

circuito OR. Entrambi questi circuiti possono essere realizzati con dei diodi, anche se nelle

realizzazioni moderne sono realizzati con transistori MOS. Per semplicità si descrive la realizzazione a

diodi.

Circuito AND

Nel circuito di figura 5.14 (a) è sufficiente che la tensione di uno degli ingressi sia bassa ("0" logico)

perché il relativo diodo conduca e si abbia in uscita una tensione bassa. Per avere un livello alto ("1"

logico) in uscita è necessario che tutti gli ingressi siano a tensione alta (tutti i diodi sono in

interdizione): la reistenza in questo caso ha la funzione di “tirare su” all’”1” logico la tensione d’uscita

quando i diodi sono interdetti, per questo si chiama “Pull up resistor”.

Circuito OR

Il circuito in figura 5.14 (b) è duale rispetto al caso precedente, si può notare l'uso di una resistenza di

pull-down per mantenere l'uscita a livello basso. La tensione in uscita è alta se uno degli ingressi è a

livello alto (il diodo corrispondente viene portato in conduzione), se invece tutti gli ingressi sono a

tensione bassa l'uscita rimane a livello basso (tutti i diodi sono interdetti).

I PLD sono dispositivi creati per realizzare qualunque funzione logica a partire da un circuito integrato

Figura 5.14 – Circuito AND (a) e circuito OR (b)

programmabile, realizzato con tecnologia PROM, in cui si scrivono le funzioni logiche da realizzare.

Lo

schema

in

figura

5.15

relativo

all'implementazione

su

PLD

della

f 1 ( A, B, C , D ) = ABCD + ABC D aiuta a comprendere il principio di funzionamento di questi

dispositivi le cui dimensioni variano a seconda del numero di ingressi trattati.

Ogni variabile d'ingresso viene, nel chip, resa disponibile sia negata sia non negata. A ciascuna

variabile corrisponde una colonna: su ogni riga orizzontale è possibile realizzare l'AND delle variabili a

disposizione, creando uno dei prodotti che devono essere sommati. Infatti ogni riga ha una resistenza di

pull-up verso Val, e i diodi realizzano la funzione AND connettendo ogni variabile che deve

partecipare alla costruzione del prodotto con la riga su cui questo è realizzato. nella figura MEM14 la

prima riga costruisce il termine ABCD e la seconda ABC D .

La sezione OR del PLD permette di sommare i prodotti così costruiti per ottenere le funzioni richieste

d'uscita. Questo si ottiene mediante delle linee verticali, con resistenze di pull-down, che tramite diodi

posti verso i termini da sommare costituiscono i circuiti OR.

Questi dispositivi hanno nomi diversi a seconda del livello di programmabilità e del costruttore che li

ha brevettati:

• PLA (Programmable Logic Array): sono programmabili sia i livelli AND sia quelli OR

• PAL: è programmabile solo uno dei livelli (AND o OR)

Con questa tecnica non si realizzano solo funzioni combinatorie, ma utilizzando anche dei flip-flop si

possono realizzare circuiti sequenziali anche complessi.

Fig. 5.16 realizzazione di funzioni sequenziali tramite PLD

In figura 5.16 si descrive come si possa realizzare una funzione sequenziale mettendo in ogni istante

(scandito dal clock) in ingresso al PLD non solo i segnali IN attuali, ma anche segnali d’uscita ottenuti

nell’istante precedente e memorizzati da un opportuno registro. All’arrivo di un nuovo impulso di clock

si presentano per l’elaborazione combinatoria da parte del PLD sia i segnali d’ingresso sia le uscite

ottenute in precedenza, e si realizza cosi’ una funzione sequenziale.