FAMIGLIA NMOS E CMOS

FUNZIONAMENTO DELLA FAM. NMOS

Una delle famiglie più utilizzate insieme alla TTL è la MOS che si suddivide in due tecnologie

fondamentali la NMOS e la CMOS, quest'ultima in diretta competizione con la TTL.

In realtà la prima tecnologia utilizzata è stata la PMOS, soppiantata dalla NMOS perché più veloce

(si spostano infatti gli elettroni invece delle lacune), perché produce minore dissipazione di

potenza ed è possibile il suo interfacciamento con la TTL.

La NMOS è stata introdotta però solo quando si è perfezionata la tecnologia costruttiva per il

controllo delle impurità nello strato di ossido di silicio che si trova sotto al gate del MOS.

In conclusione oggi la maggior parte delle memorie che hanno accesso al microprocessore

utilizzano NMOS.

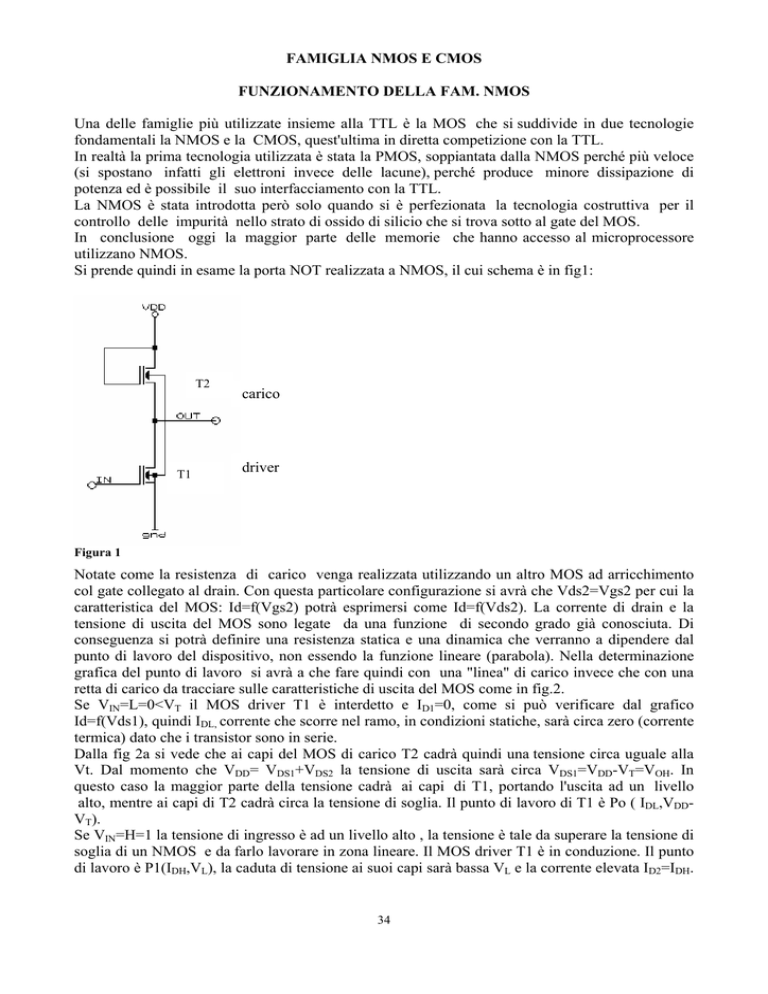

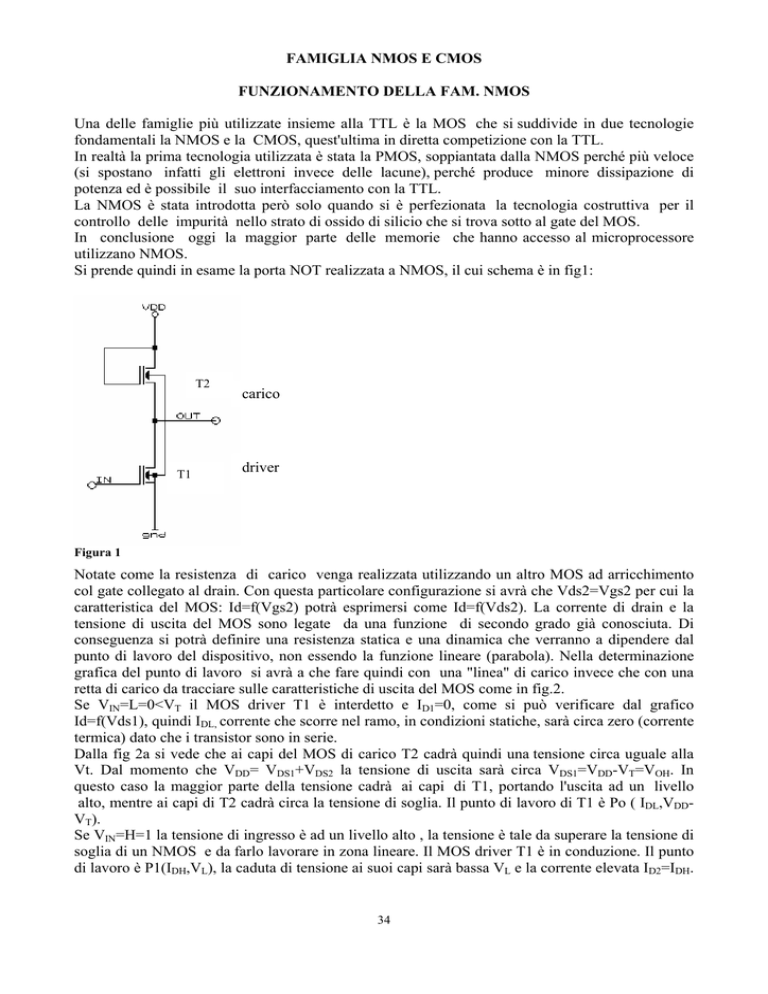

Si prende quindi in esame la porta NOT realizzata a NMOS, il cui schema è in fig1:

T2

T1

carico

driver

Figura 1

Notate come la resistenza di carico venga realizzata utilizzando un altro MOS ad arricchimento

col gate collegato al drain. Con questa particolare configurazione si avrà che Vds2=Vgs2 per cui la

caratteristica del MOS: Id=f(Vgs2) potrà esprimersi come Id=f(Vds2). La corrente di drain e la

tensione di uscita del MOS sono legate da una funzione di secondo grado già conosciuta. Di

conseguenza si potrà definire una resistenza statica e una dinamica che verranno a dipendere dal

punto di lavoro del dispositivo, non essendo la funzione lineare (parabola). Nella determinazione

grafica del punto di lavoro si avrà a che fare quindi con una "linea" di carico invece che con una

retta di carico da tracciare sulle caratteristiche di uscita del MOS come in fig.2.

Se VIN=L=0<VT il MOS driver T1 è interdetto e ID1=0, come si può verificare dal grafico

Id=f(Vds1), quindi IDL, corrente che scorre nel ramo, in condizioni statiche, sarà circa zero (corrente

termica) dato che i transistor sono in serie.

Dalla fig 2a si vede che ai capi del MOS di carico T2 cadrà quindi una tensione circa uguale alla

Vt. Dal momento che VDD= VDS1+VDS2 la tensione di uscita sarà circa VDS1=VDD-VT=VOH. In

questo caso la maggior parte della tensione cadrà ai capi di T1, portando l'uscita ad un livello

alto, mentre ai capi di T2 cadrà circa la tensione di soglia. Il punto di lavoro di T1 è Po ( IDL,VDDVT).

Se VIN=H=1 la tensione di ingresso è ad un livello alto , la tensione è tale da superare la tensione di

soglia di un NMOS e da farlo lavorare in zona lineare. Il MOS driver T1 è in conduzione. Il punto

di lavoro è P1(IDH,VL), la caduta di tensione ai suoi capi sarà bassa VL e la corrente elevata ID2=IDH.

34

Anche nel MOS di carico T2 scorrerà una corrente elevata che provocherà un'alta caduta di

tensione ai suoi capi Vh2: essendo infatti T2 un MOS utilizzato come resistore controllato in

tensione, esso offre una resistenza dipendente dalla tensione, in particolare la resistenza aumenta

all'aumentare della tensione. Concludendo quindi, la maggior parte della tensione cadrà ai capi di

T2 mentre ai capi di T1 vi sarà un livello basso di tensione VDS1=VDD-VDS2=VOL.

CARICO

DRIVER

Figura 2a

Figura 2b

In questo caso si è realizzata una porta NOT utilizzando esclusivamente transistor MOS ad

arricchimento, questo offre notevoli vantaggi:

- rende più compatto il circuito; infatti il MOS di carico occupa meno spazio di un resistore

integrato in tecnologia bipolare, è quindi possibile la realizzazione di porte sfruttando aree più

piccole sul chip;

- la realizzazione tecnologica è più veloce e meno costosa, si tratta infatti di costruire solo MOS,

uno dei dispositivi di più facile e veloce realizzazione;

- la resistenza così ottenuta ha stabilità e tolleranze superiori alle resistenze realizzate in tecnologia

bipolare.

Vi è però anche uno svantaggio notevole: l'aumento del tempo di commutazione dovuto sia al

tempo che impiegano le capacità parassite a caricarsi e a scaricarsi sia al tempo che impiega il

canale a formarsi e a distruggersi. Le capacità sono di tre tipi: gate-canale, gate-source e gate-drain

di cui le ultime due possono essere eliminate, come si sa dalla tecnica del gate al silicio

policristallino, mentre rimane ineliminabile la prima che sta alla base del funzionamento del

componente stesso.

I tempi di carica e scarica delle capacità parassite non sono uguali; questo perché il transistor di

carico, in quanto tale, avrà ovviamente una resistenza più alta di quello di comando (driver).

Pertanto queste capacità si caricheranno e si scaricheranno su resistenze di valori diversi, con

costanti di tempo non identiche.

Per quanto riguarda il tempo di formazione e di distruzione del canale si può pensare di adottare

come soluzione quella che vede un MOS a svuotamento come MOS di carico. Tale MOS infatti ha

già il canale precostituito. In questo modo vengono diminuiti i tempi di commutazione, ma aumenta

la dissipazione di potenza.

35

STUDIO DELLE PORTE NAND E NOR NMOS

Sfruttando la loro analogia col funzionamento del NOT e della logica DCTL si può facilmente

comprende il funzionamento di tali porte (FIG.3).

Per la porta NAND:

Se A=B=1=Vih, la tensione di ingresso è superiore alla tensione di soglia dei MOS, T1 e T2 sono

in conduzione e l'uscita è ad un livello basso. Come nel caso della NOT la maggior parte della

tensione cade su T3 che funziona da resistore di carico. Se invece uno almeno degli ingressi è a

zero, cioè ad una tensione inferiore alla tensione di soglia del MOS, almeno uno dei transistor

T1 o T2 viene interdetto, per cui l'uscita è ad un livello alto e diminuisce quindi la caduta su T3.

Per la porta NOR:

Se A=B=0=Vil, la tensione di ingresso è minore della tensione di soglia di un MOS, entrambi i

transistor sono interdetti per cui l'uscita è ad un livello alto. Sul MOS di carico cade come sempre

la tensione di soglia. Se almeno un ingresso è invece a 1 allora il transistor corrispondente è in

conduzione e cortocircuitando l'altro, porta l'uscita ad un livello basso.

Figura 3

In questa famiglia la porta fondamentale è la NOR, per i seguenti motivi:

- I transistor di comando sono in parallelo per cui quando l'uscita è bassa sarà y=VDSON.

Nella porta NAND invece sarà y= VDSON1 + VDSON2 : se la porta ha molti ingressi la tensione in

uscita può aumentare a tal punto da cadere in zona di indeterminazione.

Dallo studio del MOS si sa che la tensione di soglia di questi dispositivi va dai 3 ai 6 volt per cui

se non si vuole avere in uscita un livello indefinito occorrerebbe alimentare la porta con una

tensione superiore ai 12 volt. Ora per poter abbassare l'alimentazione in modo da rendere

compatibile la famiglia NMOS con la TTL occorre diminuire la tensione di soglia del MOS. Questo

viene ottenuto utilizzando tecnologie particolari quali l'impiantazione ionica.

36

CARATTERISTICHE DELLA FAM.NMOS

Vantaggi della Fam. NMOS:

-

Alta densità di integrazione

Alte frequenze di lavoro ( F= 1MHz )

Fan-Out = 20

W = 1mW per porta

tp mediamente di 100nsec ( piuttosto elevato)

FUNZIONAMENTO DELLA FAMIGLIA CMOS

Per migliorare alcune caratteristiche della porta NMOS è stata realizzata la logica CMOS che

presenta una diminuzione dei tempi di propagazione del segnale e un minor consumo di potenza.

Vediamo il perché:

D

D

C

Figura 4a

L

Figura 4b

Si analizza la porta NOT, vedi fig4a.:

Come si può vedere la porta è realizzata con due MOS ad arricchimento uno a canale N e l'altro a

canale P, posti in serie con il gate in comune.

L'ingresso è inserito nel gate mentre l'uscita è prelevata sul drain comune ai due MOS, infatti i

due MOS hanno i drain collegati insieme, mentre i rispettivi substrati sono connessi al source.

Il suo funzionamento è il seguente:

Se viene inviato un livello alto di tensione in ingresso Vin=Vih=Vdd il transistor NMOS entra in

conduzione mentre rimane interdetto il PMOS. Si avrà pertanto in uscita un livello logico

basso e la maggior parte della tensione cadrà ai capi del PMOS.

Se invece in ingresso viene inviato un livello basso, il transistor NMOS rimane interdetto, mentre

va in conduzione il PMOS. Di conseguenza in uscita si avrà un livello logico alto.

37

Il PMOS è in conduzione a livello basso perché il gate è collegato a massa, ad una tensione più

bassa di quella presente sul source e sul substrato (Vdd), per cui le lacune si addenseranno sotto al

gate dando luogo al canale (Vgs<0).

E' facile intuire che in condizioni statiche non circolerà mai corrente nel circuito dato che uno dei

due MOS è sempre in interdizione, per cui la porta presenta una bassa dissipazione di potenza,

praticamente nulla.

In condizioni dinamiche invece si avrà un passaggio di corrente: quando uno dei due

transistor commuta dall'interdizione alla conduzione, l'altro passa

dalla conduzione

all'interdizione, per cui vi sarà un momento molto breve in cui condurranno entrambi e passerà

corrente.

E' facile quindi concludere che la dissipazione di potenza per questa famiglia

dipende dalla frequenza di commutazione del segnale di ingresso (vedi FIG.5).

Se in ingresso il segnale viene commutato da 1 a 0, l'uscita passa da 0 a 1.

La capacità parassita, vista in uscita alla porta pilota, dovuta ad un eventuale carico (ad es. un'altra

porta), si carica attraverso il PMOS. In questo caso viene quindi dissipata una certa potenza non

considerata in condizioni statiche.

Se in ingresso il segnale viene commutato da 0 a 1, l'uscita passa da 1 a 0.

Ora la capacità parassita di uscita si scarica attraverso il transistor NMOS. Anche in tal caso viene

dissipata una certa potenza non considerata in condizioni statiche.

Calcolo della potenza dissipata:

PTOT = Po + P1

Dove:

Po = potenza dissipata statica o stanby power ≅ 1nW per porta logica

P1 = potenza dissipata durante la commutazione = C * VDD2 * f

Dove: C =10pF

Inoltre si pone :VDD = 10v, f = 1MHz,

PTOT = 10-9 + 10 * 10-12*10 2 *106 = 10-3W = 1mW

Figura 5

38

Le capacità si scaricano e si caricano sulla piccola resistenza del transistor che conduce in quel

momento, che è la stessa per entrambi i MOS.

Pertanto i due tempi di carica e scarica saranno simmetrici.

In condizioni statiche tutte le famiglie MOS hanno un fan-out molto alto: ciò dipende dal fatto che

la corrente di gate di un MOS è dell'ordine del nA, infatti la porta non assorbe corrente di ingresso.

Come visto precedentemente, in condizioni dinamiche, essendoci le capacità parassite che hanno

valori elevati, accade che durante la loro carica e scarica assorbono corrente e il fan-out verrà

notevolmente ridotto, soprattutto alle alte frequenze.

Si inserisce ora lo schema di una NOT a CMOS comprendente i diodi di protezione, utili per

proteggere il gate dalle cariche elettrostatiche che si possono depositare su di esso (FIG.6).

Figura 6

Il funzionamento del circuito di protezione a diodi è il seguente: qualsiasi sia il segnale di ingresso,

H o L, manderà sempre in interdizione i diodi dato che il suo valore sarà sempre minore di Vdd e

superiore al potenziale di massa.

Se si ha invece una sovratensione (Vin> Vdd+Vth) o una sottotensione (Vin<-Vth) i diodi

entreranno in conduzione proteggendo il gate e cortocircuitando le sovratensioni stesse.

STUDIO DELLE PORTE NAND E NOR CMOS

Il comportamento di queste due porte è molto simile a quello del NOT e del

NAND e NOR in logica NMOS, per il funzionamento vedere FIG.7.

FIG.7

39

Porta NAND:

Se entrambi gli ingressi sono ad un livello alto, T3 e T4 conducono portando l'uscita a zero.

Se invece almeno un ingresso è a zero uno dei due PMOS va in conduzione e cortocircuitando

l'altro, manda l'uscita ad un livello alto.

Porta NOR:

Se entrambi gli ingressi sono a zero, T1 e T2 conducono, mentre T3 e T4 sono interdetti, per cui

l'uscita viene ad essere ad un livello alto.

Se invece almeno un ingresso è ad un livello alto, almeno un NMOS è in conduzione e

cortocircuitando l'altro porterà l'uscita a zero.

Si è visto che nella logica TTL con uscita totem-pole non è possibile realizzare il collegamento

wired-and a meno che non si adotti la soluzione open-collector. Anche nel caso della logica CMOS

vi è lo stesso tipo di problema che si risolve con l'introduzione di porte del tipo open-drain.

Inoltre anche per la logica CMOS esiste una soluzione di tipo three-state utile per esempio per il

trasferimento dei dati su BUS DATI in un sistema a µP.

VANTAGGI DELLA FAM. CMOS

•

•

•

•

•

Minore possibilità di innesco di fuga termica (comportamento metallico in quanto vi sono solo

cariche di tipo maggioritario)

Tensione di alimentazione compresa fra 3 e 18v

Fan-out infinito in condizioni statitche, in condizioni dinamiche è invece 50

Dissipazione di potenza praticamente nulla in condizioni statiche, comunque molto bassa anche

un condizioni dinamiche e dipendente dalla frequenza di lavoro.

Alte frequenze di lavoro (10MHz)

SVANTAGGI DELLA FAM. CMOS

•

•

•

Tempi di propagazione più elevati della Fam. TTL (100nsec) per quanto riguarda le prime

generazioni di CMOS; il problema è stato risolto con l'avvento delle nuove tecnologie.

Minor ingombro rispetto alla TTL ma maggior ingombro rispetto alla NMOS

Aumento dei costi rispetto alla Fam. NMOS

40

PARAMETRI DELLE SOTTOFAMIGLIE CMOS:

4000B

HC

HCT

AC

3,5V

3,15V

2V

3,15V

VIH(MIN)

1,5V

0,9V

0,8V

1,35V

VIL(MAX)

4,95V

4,4V

4,4V

4,4V

VOH(MIN)

0,05V

0,1V

0,1V

0,1V

VOL(MAX)

1,45/1,45V 1,25/0,8 2,4/0,7V 1,25/1,25

NMH/L

V

V

I(MAX)

± 0,1µA ± 0,1µA ± 0,1µA ± 0,1µA

IO(MAX)

µ 0,44mA µ 4mA µ 4mA µ 24mA

0,001

0,00000

P(mW)Static

25

a

0,1

0,17

P(mW)100K

Hz

5

40

Fmax(MHz)

11

1,4

pJ(100KHz)

105

8

tp(nsec)

3-15

2-6

Vcc(V)

4*

10*

F.O.H/L

•

IL FAN-OUT DIPENDE DALLA FREQUENZA

41

ACT

2V

0,8V

4,4V

0,1V

2,4/0,7V

± 0,1µA

µ 24mA