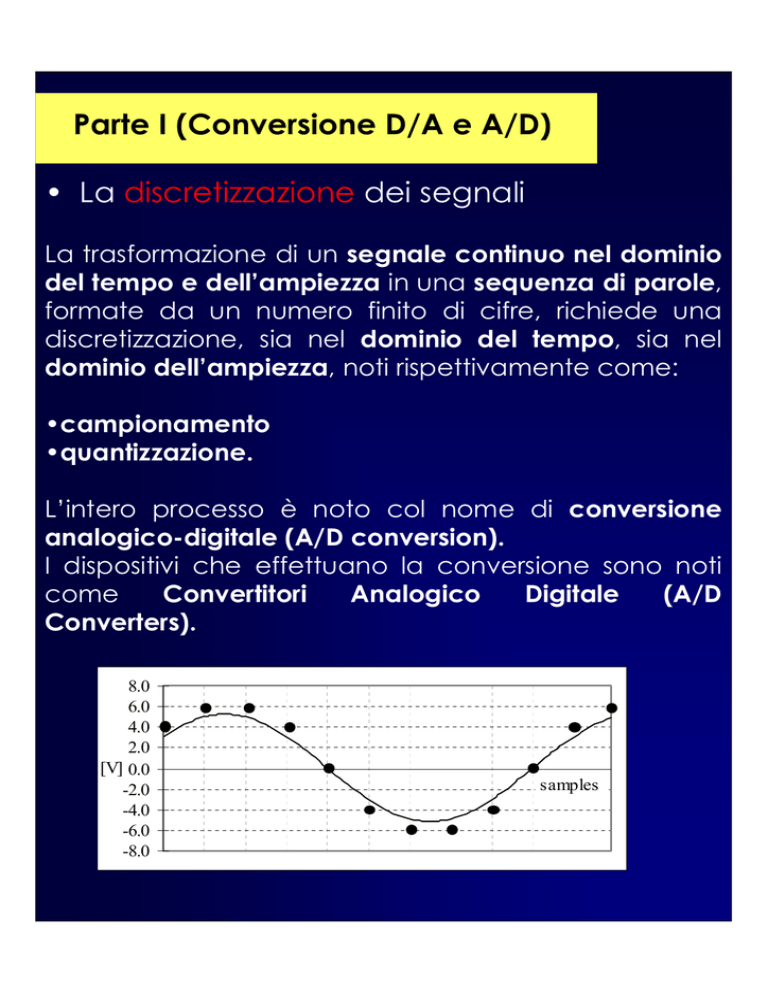

Parte I (Conversione D/A e A/D)

• La discretizzazione dei segnali

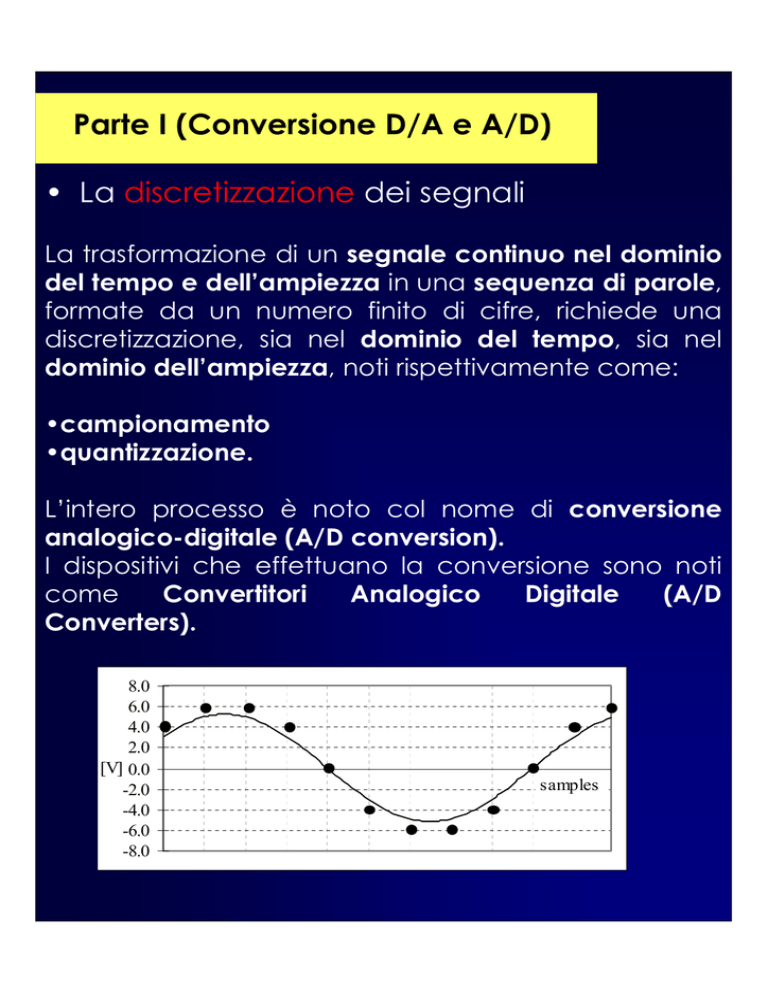

La trasformazione di un segnale continuo nel dominio

del tempo e dell’ampiezza in una sequenza di parole,

formate da un numero finito di cifre, richiede una

discretizzazione, sia nel dominio del tempo, sia nel

dominio dell’ampiezza, noti rispettivamente come:

•campionamento

•quantizzazione.

L’intero processo è noto col nome di conversione

analogico-digitale (A/D conversion).

I dispositivi che effettuano la conversione sono noti

come

Convertitori

Analogico

Digitale

(A/D

Converters).

8.0

6.0

4.0

2.0

[V] 0.0

-2.0

-4.0

-6.0

-8.0

samples

Parte I (Conversione D/A e A/D)

• La discretizzazione dei segnali

Il teorema del campionamento ci assicura che se

sono soddisfatte alcune ipotesi, il processo di

discretizzazione nel dominio del tempo, non produce

alcuna perdita d’informazione:

Sia f(t) un segnale con trasformata di Fourier F(), tale

che F()=0 per | c. Si ha, allora:

f t

f nT

s 2 c ;

infatti…..

sin c t nT

c t nT

T 2 / s

Parte I (Conversione D/A e A/D)

• La discretizzazione dei segnali

L’uscita

di

un

campionatore

può

essere

rappresentata come una serie numerica, i cui

elementi coincidono con i valori assunti dal segnale

tempo-continuo in istanti multipli del tempo di

campionamento

f(t)

T

{f(nT)}

Un segnale campionato può essere pensato come il

risultato del prodotto tra il segnale analogico e un

treno di impulsi di durata finita.

T

Parte I (Conversione D/A e A/D)

• La discretizzazione dei segnali

Si ottiene un campionamento ideale quando s(t) è un

treno di impulsi di Dirac.

0

t0

s (t ) t

singolare t 0

La singolarità è tale che:

t dt 1

0

•Intuitivamente, la funzione impulso di Dirac può

essere immaginata come il limite per che tende a

zero dell’impulso di durata finita p(t).

•L’impulso di Dirac code della proprietà di selezione:

sia g(•) una funzione continua, si ha:

g t t dt g 0

0

4

Parte I (Conversione D/A e A/D)

• La discretizzazione dei segnali

Il processo di campionamento equivale ad

un’operazione di modulazione ad ampiezza di impulsi

(PAM).

•il treno di impulsi costituisce la portante;

•il segnale da campionare rappresenta

modulante.

la

Il segnale campionato vale quindi:

f s t f t st

•il segnale s(t) è un segnale periodico di periodo T;

•ogni segnale x(t), ad energia finita può essere

espresso come:

xt n n t

t a, b

n

se sono soddisfatte le seguenti condizioni:

a)

b)

c)

i segnali n(t) formano un sistema ortonormale;

il sistema di segnali ortonormali è completo per il segnale x(t);

i coefficienti n si ottengono dalla relazione:

b

n xt n* t dt

a

5

Parte I (Conversione D/A e A/D)

• La discretizzazione dei segnali

In particolare il sistema di segnali:

T T

t ,

2 2

n

1 jn 2T t

n t e

T

è completo per tutti i segnali

x(t)

nell’intervallo (-T/2, T/2) e si può scrivere:

xt

e

jn

2

t

T

n

n

definiti

t T / 2, T / 2

2

jn t

1

n

xt e T dt

T T / 2

T /2

noto come sviluppo in serie esponenziale di Fourier.

NB: poiché i segnali utilizzati per lo sviluppo in serie

esponenziale di Fourier

sono ortonormali con

periodo T, quanto detto vale anche per un generico

segnale periodico.

xt

e

n

jn

2

t

T

n

2

jn t

1

T

n

x

t

e

dt

T T / 2

t ,

T /2

6

Parte I (Conversione D/A e A/D)

• La discretizzazione dei segnali

Per il treno di impulsi si avrà:

s t

e

n

jn

2

t

T

n

e

n

2

, t ,

s

T

jn s t

n

T /2

1

jn s t

n

s

t

e

dt

T T / 2

Quindi, il segnale campionato assume la forma:

f s t f t

e

n

n

jn s t

2

s

, t ,

T

jn t

f

t

e

n

s

n

Si noti che tale segnale è un transiente ed è quindi

possibile calcolarne la trasformata di Fourier:

jn s t

F F n f t e

n

#

jn t

F

f

t

e

n

s

n

7

Parte I (Conversione D/A e A/D)

• La discretizzazione dei segnali

Poiché la trasformata di Fourier di un segnale f(t) vale

per definizione:

F

f t e jt dt

Per il segnale campionato si ottiene:

F #

n

n

f t e

n

n

f t e jn s t e jt dt

j n s t

dt n F n s

n

Essendo F()=F(f(t)) la trasformata di Fourier del

segnale modulante.

8

Parte I (Conversione D/A e A/D)

• La discretizzazione dei segnali

L’operazione di campionamento introduce nuove

componenti spettrali che corrispondono alla

traslazione dello spettro in banda base F() del

segnale.

Se f(t) è un segnale con spettro limitato F()=0 per

| c e s c, allora le varie ripetizioni non si

sovrappongono ed il segnale originario può essere

ricostruito a meno di un fattore di scala elaborando il

segnale campionato f#(t), utilizzando un filtro che

abbia come funzione di trasferimento:

1

H

0

per c

per c

9

Parte I (Conversione D/A e A/D)

• La discretizzazione dei segnali

Se la condizione s c non viene rispettata le

ripetizioni dello spettro del segnale originario si

sovrappongono e si incappa nel fenomeno

dell’alias. In tali condizioni non è più possibile

ricostruire

il

segnale

originario

attraverso

un’operazione di filtraggio.

10

Parte I (Conversione D/A e A/D)

• La discretizzazione dei segnali

Nel caso di un campionatore ideale (si utilizza un

treno di impulsi di Dirac) si ha:

s t

t nT

n

f t f t t nT

*

n

f t t nT

n

f nT t nT

n

Il segnale campionato viene rappresentato da un

treno di funzioni impulsive e l’area di ogni impulso

corrisponde al valore del generico campione.

Nel dominio della frequenza si ha:

1

n

T

T /2

jn t

t

e

dt

s

T / 2

1

s t

T

1

F

T

*

e

jn s t

1

T

.

n

F n .

s

n

11

Parte I (Conversione D/A e A/D)

• La discretizzazione dei segnali

Poiché f(t) è un segnale con spettro limitato è

possibile calcolare lo sviluppo in serie esponenziale

dello spettro. Si ha, quindi:

T

c ;

2

t ;

F f n e

jn

c

;

fn

1

2c

c

F e

c

jn

c

2 1

d

2 2c

F e

jn

c

d

Per la definizione di antitrasformata di Fourier di un

segnale vale la relazione:

1

X t

2

X e jt d ,

Il generico coefficiente del nostro sviluppo in serie di

potenze può essere, allora, riscritto come:

fn

c

n

f

c

,

12

Parte I (Conversione D/A e A/D)

• La discretizzazione dei segnali

quindi lo spettro del segnale assume la forma

jn

c

F

f n e

c

c

0

per c

per c .

e antitrasformando

1

f t

2

F e

n

n

f

c

j t

1

d

2

1

2

c

c

e

c

F e jt d

c

n

j t

c

d

c

c

n

j t n

n 1 e

f

n

c 2 c j t

c

c

c

n

n

j t n

j t

n 1 e

e

f

n

j t

c 2 c

c

c

c

c

c

13

Parte I (Conversione D/A e A/D)

• La discretizzazione dei segnali

n

n

j t n

j t

n

e

1

e

f

2j

c n

c t

c

c

c

c

c

n

c

sin t

n c

f

n

n

c

c

t

c

s 2 c

sin t nT c

essendo 2 2T .

,

f nT

t nT c

n

c s

2

14

Parte I (Conversione D/A e A/D)

• La discretizzazione dei segnali

La

formula

introdotta

nel

teorema

del

campionamento è nota come serie cardinale e la

funzione:

sin c t

g t

ct

è detta mantenitore cardinale e la pulsazione c=s/2

è nota in letteratura come frequenza di Nyquist..

Un mantenitore cardinale è un filtro non fisicamente

realizzabile. Esso può essere soltanto approssimato.

Per questo motivo:

•Si utilizza una frequenza di campionamento

superiore a quella prevista dal teorema di Shannon

(tipicamente 10 volte);

•Si utilizzano dei filtri ricostruttori o mantenitori.

I filtri più comunemente utilizzati sono:

•Il ricostruttore di ordine zero;

•Il ricostruttore del primo ordine;

•Il connettore ideale di punti.

Parte I (Conversione D/A e A/D)

• La discretizzazione dei segnali

Il ricostruttore di ordine zero

E’ il filtro ricostruttore più comune ed è noto anche

come sample-and-hold o mantenitore di ordine zero.

Esso è caratterizzato dalla risposta all’impulso:

1

ht

0

0t T

altrove

16

Parte I (Conversione D/A e A/D)

• La discretizzazione dei segnali

Il ricostruttore di ordine zero

Quindi la qualità (visiva) dell’approssimazione di un

segnale aumenta al diminuire dell’intervallo T.

La risposta in frequenza del S&H vale:

1 e sT

H ( s)

s

H ( j )

jT

1 e

j

2 e

2e

j

T

2

e

j

j

T

2

T

2

jT

1 e

2j

2e

j

T

2

e

j

T

2

e

2j

j

T

2

j sinT / 2

T

sin Te 2

.

2

/

2

T

T

NB: il S&H ha una fdt

che si annulla a s e

non a c, come

previsto

per

il

ricostruttore ideale!

17

Parte I (Conversione D/A e A/D)

• La discretizzazione dei segnali

Il ricostruttore del primo ordine

Il filtro ricostruttore del primo ordine predice il

campione f((n+1)T) utilizzando la retta che passa per i

punti f((n-1)T) e f(nT).

f (nT ) f ((n 1)T )

(t nT )

T

per nT t (n 1)T ;

y (t ) f (nT )

e la risposta all’impulso è (per T=1):

u(t)+rect(t)-2u(t-1)-2rect(t-1)+u(t-2)+rect(t-2)

y(t)

f((n-1)T)

f(nT)

T

18

Parte I (Conversione D/A e A/D)

• La discretizzazione dei segnali

Il ricostruttore del primo ordine

Le corrispondenti fdt e risposta armonica valgono:

s 11 2e s e 2 s

H ( s)

s2

j 1 1 2e j e 2 j

.

H ( j )

2

( j )

NB:

la

risposta

in

frequenza di un FOH ha

una

minore

attenuazione alle basse

frequenze ma amplifica

le componenti ad alta

frequenza.

19

Parte I (Conversione D/A e A/D)

• La discretizzazione dei segnali

Il ricostruttore del primo ordine

Le prestazioni di un FOH possono essere migliorate

utilizzando un filtro con correzione parziale della

velocità:

f (nT ) f ((n 1)T )

y (t ) f (nT )

(t nT )

T

per nT t (n 1)T ;

0 1

20

Parte I (Conversione D/A e A/D)

• La discretizzazione dei segnali

Il connettore ideale di punti

Se è possibile accettare un ritardo di un campione, un

buon ricostruttore è il connettore ideale di punti.

t nT

(n 1)T t

y (t ) f (nT )

f n 1T

T

T

per nT t (n 1)T ;

e la risposta all’impulso è (per T=1):

h(t)=rect(t)-2rect(t-1)+rect(t-2)

21

Parte I (Conversione D/A e A/D)

• La discretizzazione dei segnali

Il connettore ideale di punti

Le corrispondenti fdt e risposta armonica valgono:

1 2e

H ( s)

1 2e

H ( j )

s

s2

j

e 2 s

e 2 j

.

2

( j )

NB:

un

connettore

ideale ha caratteristiche

migliori in termini di

filtraggio

delle

componenti ad alta

frequenza

e

di

ampiezza

dei

lobi

secondari.

22

Parte I (Conversione D/A e A/D)

• La discretizzazione dei segnali

Più in generale gli algoritmi di ricostruzione utilizzano

un numero ragionevolmente piccolo di campioni

vicini all’istante considerato.

In genere gli oscilloscopi digitali operanti in real-time

utilizzano 8 campioni in totale, 4 precedenti e 4

successivi l’istante considerato.

Ciascun campione viene pesato per un coefficiente,

conservato in una opportuna look-up table e sono

scelti in modo da ottimizzare le prestazioni del filtro

ricostruttore.

23

Parte I (Conversione D/A e A/D)

• La discretizzazione dei segnali

Per applicazioni particolari è possibile ricorrere a

filtri ricostruttori che utilizzano decine di campioni

del segnale originario, con un corrispondente

incremento di occupazione di memoria e di

carico computazionale.

24

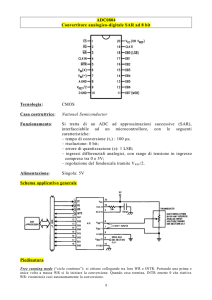

Parte I (Conversione D/A e A/D)

• La conversione D/A

I convertitori D/A (Digital to Analog Converters)

rappresentano un’interfaccia tra i segnali digitali del

mondo dei computer e il mondo analogico.

Un D/A accatta come ingresso un segnale digitale e

fornisce un’uscita (in tensione o in corrente a seconda

della tecnologia utilizzata e dell’applicazione

prevista) dipendente dall’ingresso fornito, secondo la

relazione:

Vo K VFS a1 2 1 a2 2 2 ... an 2 n VOS

a1,…an

VREF

DAC

Vo

Essendo:

•Vo la tensione d’uscita;

•K il guadagno (tipicamente è K=1);

•a1,…,an la parola digitale da convertire;

•Vos la tensione di offset (tipicamente è Vos=0)

•VFS la tensione di fondo-scala (legata a VREF, valori tipici

sono 2.500, 5.000, 10.00, 5.120, 10.24 V o i corrispondenti

valori bipolari e 2.0mA).

Parte I (Conversione D/A e A/D)

• La conversione D/A

I convertitori D/A sono caratterizzati mediante

caratteristiche statiche e caratteristiche dinamiche.

Le caratteristiche statiche più importanti sono:

•La risoluzione ;

•La curva caratteristica ;

•L’errore di linerità;

•L’errore di monotonicità;

•L’accuratezza;

•La stabilità.

Le caratteristiche dinamiche più importanti sono:

•Il settling time;

•Il fenomeno del glitching.

Parte I (Conversione D/A e A/D)

• La conversione D/A

La risoluzione

La risoluzione di un convertitore è pari alla minima

variazione del segnale d’uscita che il dispositivo può

generare. Essa è pari a 1 LSB (Least Significant Bit) ed

è legata alla tensione di fondo scala e al numero di

bit (parallelismo del convertitore) dalla relazione:

VLSB=VFS/2n

1 LSB= 1/2n

se si tratta di un dispositivo unipolare

VLSB=VFS/2n-1

1 LSB= 1/2n-1

Nel caso di un dispositivo bipolare

Valori tipici di risoluzione vanno da 8 a 16 bit.

27

Parte I (Conversione D/A e A/D)

• La conversione D/A

La risoluzione

ESEMPIO: Un convertitore AD ad 8 bit ha una tensione di

riferimento pari a 5V.

•La tensione corrispondente alla parola 10110100 è:

Vref*(2-1+2-3+2-4+2-6)=Vref*(1/2+1/8+1/32+1/64)=3.5156V

•Il LSB vale:

1LSB=1/2-8=1/256

VLSB=5/256=19.5 mV

NB: espressioni equivalenti

risoluzione sono:

•8 bit di risoluzione,

•0.4% del fondo scala,

•1 parte su 256.

per

l’espressione

della

28

Parte I (Conversione D/A e A/D)

• La conversione D/A

La curva caratteristica

La curva caratteristica di un DA rappresenta il legame

esistente tra i codici in ingresso e i valori forniti in

uscita (tensione o corrente in accordo con la

tecnologia utilizzata)

VOS 0;

K 1.

Parte I (Conversione D/A e A/D)

• La conversione D/A

La curva caratteristica

Vengono definiti gli errori (in LSB) di:

•Offset

•Guadagno

EOS

VOUT

VLSB

;

0...0

con errore di offset annullato

VOUT

EK

VLSB

V

OUT

VLSB

1...1

2 N 1

0...0

NB: Le case costruttrici suggeriscono i circuiti da

utilizzare per eliminare tali cause di errore!

30

Parte I (Conversione D/A e A/D)

• La conversione D/A

La curva caratteristica

Finora si è fatta l’ipotesi che nel passaggio da una

parola alla successiva la variazione della tensione in

uscita sia sempre costante e pari a 1 LSB e che quindi

la curva caratteristica sia una retta. Nei dispositivi

reali, a causa di imperfezioni circuitali, i valori di

tensione in uscita non si trovano su una retta.

31

Parte I (Conversione D/A e A/D)

• La conversione D/A

La curva caratteristica

Dopo aver corretto l’errore di guadagno e di offset la

curva (retta) caratteristica viene determinata

attraverso un processo di approssimazione.

•Least-square fit

Utilizza il metodo dei minimi quadrati per determinare

la retta che approssima le uscite del DAC;

•Zero-base method

Determina la curva caratteristica imponendo il

passaggio per il primo punto e determinando il

guadagno minimizzando il valore assoluto dell’errore

massimo.

•Terminal-point method

Approssima la curva caratteristica con la retta che

passa per il primo e l’ultimo valore in uscita dal DAC.

32

Parte I (Conversione D/A e A/D)

• La conversione D/A

La linearità

L’errore di linearità indica lo scarto tra l’uscita reale di

un DAC e il corrispondete valore stimato utilizzando la

curva caratteristica. Vengono definite:

•L’integral nonlinearity error (INL)

è dato dal massimo scostamento dalla curva

interpolante (ottenuta con uno qualsiasi dei metodi

precedentemente introdotti);

•Il’differential nonlinearity error (DNL)

è dato, per ogni codice, dalla differenza tra la

variazione effettiva del segnale e la variazione

prevista di 1LSB;

33

Parte I (Conversione D/A e A/D)

• La conversione D/A

La linearità

L’errore di linearità viene espresso in frazioni del LSB o

in percentuale del valore di fondo scala.

•La monotonicità

Quando si incrementa di uno l’ingresso di un DAC ci si

aspetta che anche l’uscita cresca. Se ciò non accade si ha

un errore di monotonicità. Un DAC non monotono ha un

errore DNL superiore a 1LSB.

NB: Un buon DAC dovrebbe avere un errore di linearità

inferiore a 0.5 LSB e non presentare errore di monotonicità.

34

Parte I (Conversione D/A e A/D)

• La conversione D/A

L’accuratezza

Vengono spesso indicate:

•L’absolute accuracy

E’ lo scarto massimo tra l’uscita ideale prevista e l’uscita

reale del DAC (incluso l’errore di guadagno e di offset)

•Relative accuracy

E’ lo scarto massimo tra l’uscita ideale prevista e l’uscita

reale del DAC (dopo la correzione dell’errore di guadagno

e di offset e quindi coincide con l’INL).

NB: L’accuratezza non va confusa con la risoluzione.

Un DAC può avere, ad esempio, una risoluzione di 12

bit e un’accuratezza di soli 10 bit. Un buon DAC

dovrebbe garantire un’accuratezza migliore della

risoluzione.

35

Parte I (Conversione D/A e A/D)

• La conversione D/A

La Stabilità

Misura la dipendenza dei parametri caratteristici del

dispositivo dalla temperatura, dal tempo etc.

36

Parte I (Conversione D/A e A/D)

• La conversione D/A

Il Settling time

E’ il tempo impiegato dall’uscita di un DAC a portarsi in

prossimità del valore finale (in genere 0.5 LSB), dopo un

cambiamento di codice.

Il glitching

Quando il DAC riceve un nuovo codice, è necessario che

alcuni interruttori si chiudano e altri si aprano. Se i tempi

richiesti da queste operazioni sono diversi si generano in

uscita dei transitori di entità molto elevata.

37

Parte I (Conversione D/A e A/D)

• La conversione D/A

Esistono due principali famiglie di convertitori DA:

•Convertitori in tecnologia MOS

Sfruttano le eccellenti proprietà dei MOS come

interruttori di tensione;

•Convertitori in tecnologia bipolare

Utilizzano transistor BJT per la realizzazione di specchi

di corrente.

38

Parte I (Conversione D/A e A/D)

• La conversione D/A

Il convertitore a resistenze pesate utilizza una rete di

resistenze, i cui valori crescono come potenze

successive di due, per realizzare i diversi bit della

parola da convertire.

2nR

4R 2R

R

+

-Vr

Il convertitore a resistenze pesate è un dispositivo

molto semplice. Esso tuttavia non è adatto alla

realizzazione di sistemi in tecnologia IC per il consumo

eccessivo di area di silicio dovuto alla realizzazione

della rete di resistenze.

Questo schema viene utilizzato soltanto per realizzare

convertitori discreti e a bassa risoluzione.

Parte I (Conversione D/A e A/D)

• La conversione D/A

Il convertitore a rete R/2R utilizza, per realizzare i diversi

bit della parola da convertire, una rete di resistenze

caratterizzati soltanto da due diversi valori.

+

-Vr

Tipicamente il valore di R varia nell’intervallo 2.5k10k

Con questa tecnologia vengono spesso realizzati

dispositivi monolitici a a levata risoluzione.

Parte I (Conversione D/A e A/D)

• La conversione D/A

Entrambi i convertitori descritti producono un errore

dovuto alla corrente che attraversa la resistenza

equivalente del generatore di riferimento.

Ad esempio nella figura riportata il riferimento di

tensione presenta una resistenza interna pari a 200

Ciò causa un errore del DAC che dipende dal codice

in ingresso.

41

Parte I (Conversione D/A e A/D)

• La conversione D/A

Il problema dell’errore indotto dai fenomeni di

riscaldamento e di variazione della tensione di

riferimento viene risolto utilizzando la struttura a rete

R-2R invertita:

In questo caso:

•La corrente che attraversa la rete di resistenze è

costante;

•I dati in ingresso deviano la corrente a massa, o

all’ingresso del convertitore corrente tensione

(anch’esso al potenziale di massa grazie al principio

della massa virtuale).

NB: ai due terminali dell’op-amp sono disponibili valori

complementari di corrente.

42

Questa è la struttura più comunemente utilizzata per la

realizzazione di DAC in IC, specialmente in tecnologia CMOS

Parte I (Conversione D/A e A/D)

• La conversione D/A

I convertitori DA in tecnologia bipolare sfruttano la

possibilità di realizzare i BJT per realizzare pozzi di

corrente opportunamente commutati.

La pesatura delle correnti può essere ottenuta, in

linea di principio utilizzando transistor matched.

43

Parte I (Conversione D/A e A/D)

• La conversione D/A

L’intero DAC assume allora la forma:

…ed esistono strutture per limitare il range di

variazione delle aree dei transistor e/o dei valori di

resistenza richiesti.

44

Parte I (Conversione D/A e A/D)

• La conversione D/A

Sono stati realizzati anche DAC che utilizzando dei

capacitori, sia secondo la struttura a capacità

pesate, sia a rete C-2C:

Realizzando strutture con consumi estremamente

ridotti.

45

Parte I (Conversione D/A e A/D)

• La conversione D/A

Una rete di resistenze tutte uguali e una rete di

decodifica

permette

di

realizzare

un

DAC

rigorosamente monotono:

46