istockphoto

Transistor,

è ora dei 45 nm

Penryn, il futuro prossimo dei processori Intel,

integrerà transitor realizzati con un processo

produttivo a 45 nm e

nuova metallizzazione.

A cura di Davide Piumetti

egli ultimi anni l’evoluzione

dei processori Intel ha seguito una strada ben definita, caratterizzata dall’introduzione

di una nuova architettura con cadenza ogni due anni. A ogni generazione successiva, grazie al miglioramento nelle tecnologie di

produzione, i progettisti cercano di

migliorare le caratteristiche dei

processori precedenti aumentandone la potenza elaborativa e implementando nuove capacità.

L’aumento delle prestazioni tra

due differenti generazioni architetturali è dovuto in particolar modo al miglioramento della tecnolo-

N

68

PC Professionale - luglio/agosto 2007

gia produttiva, in grado di costruire

transistor sempre più piccoli e più

veloci. A ogni passaggio generazionale Intel è riuscita a rispettare

una delle più famose leggi in ambito elettronico, quella che Gordon

Moore predisse nel 1965. Più di

quarant’anni fa Moore pronosticò

un raddoppio del numero di transistor che costituiscono un processore ogni 18/24 mesi; e questo, dati

alla mano, è esattamente quanto

successo negli ultimi decenni.

La produzione di un processore costituito da un numero doppio di

transistor rispetto al precedente pone però seri problemi tecnici nella

IN PROFONDITÀ

CPU

Le moderne Cpu sono composte da milioni di transistor, con una crescita esponenziale del loro numero al passare degli anni.

Ad esempio, restando nell’ultima decade, il processore Pentium III del 1999 (a sinistra nelle foto) integra “appena” 9,5 milioni

di transistor, mentre il primo Pentium 4, datato 2000, arrivava a 42 milioni (al centro). L’odierno prodotto di punta di Intel, il

QX6800 Core 2 Extreme, è costituito da 580 milioni di transistor, mentre il futuro quad core con die Penryn (a sinistra nelle

foto) avrà 820 milioni di transistor, più o meno quanti ne sono presenti in novanta Pentium III.

realizzazione pratica: l’energia necessaria al suo funzionamento, così

come l’area occupata e il calore

prodotto, raddoppieranno di conseguenza, rendendo spesso impossibile ottenere chip più evoluti senza

modificarne anche il processo fisico

di produzione.

Solo una nuova tecnologia che utilizzi transistor più piccoli permette

infatti di aumentare il numero degli

stessi in un processore (e di conseguenza le prestazioni) mantenendo

invariate le richieste energetiche.

Ne consegue che la progettazione

di una nuova microarchitettura è

strettamente legata all’introduzione

di un nuovo processo produttivo, in

grado di gestire un maggior numero di transistor. La massima espressione della tecnologia produttiva

attuale è in grado di costruire transistor dalle dimensioni di circa 65

nanometri (un capello umano ha un

diametro di circa 90.000 nanometri), mentre il prossimo stadio evolutivo è stato fissato nei processori

Intel a 45 nm.

Il raggiungimento di dimensioni

talmente ridotte pone però dei

grossi problemi alla tecnologia attuale, che non riesce a essere utilizzata quando le dimensioni di alcune parti dei transistor sono di appena qualche centinaio di atomi. Intel

ha però già la soluzione al problema, dopo più di quarant’anni si appresta infatti a un cambio radicale

nella tecnologia di produzione, rimasta praticamente immutata per

tutto questo tempo.

Evoluzione Cpu

Come detto l’evoluzione dell’architettura dei microprocessori è

strettamente legata all’introduzione di un nuovo processo di produzione degli stessi, in grado di costruire transistor più piccoli e veloci che possano essere stipati in numero molto maggiore nella stessa

porzione di silicio.

Ingegnere Intel mostra un wafer

da 300 mm con circuiti a 45 nm.

69

PC Professionale - luglio/agosto 2007

Difficilmente però un’azienda come Intel rischierebbe di introdurre

nello stesso momento un’architettura e un processo di produzione

completamente nuovi; le variabili

e i possibili problemi in gioco sarebbero davvero troppi.

La strada intrapresa da Intel è leg g e r m e n t e d i f f e r e n t e , un nuovo

processo produttivo viene infatti

adottato solo su di una architettura già conosciuta e perfettamente

funzionante e nello stesso modo

una nuova architettura è implementata attraverso un processo

produttivo già collaudato. Gli ultimi anni di evoluzione Intel ne sono un perfetto esempio, nel 2005

venne introdotto il processo a 65

nm con i processori Pentium D basati sull’architettura NetBurst già

utilizzata dai Pentium 4; l’anno

successivo, con la tecnologia di

produzione giunta alla piena maturazione fu la volta del cambio di

architettura, con l’introduzione di

Core. Nei prossimi mesi, secondo i

piani di Intel, ci si dovrebbe quindi

aspettare il passaggio alla nuova

tecnologia di produzione, fissata a

45 nm.

In contemporanea Intel non presenterà però una nuova architettura completa, ma un’evoluzione di

quella Core con i processori chiamati Penryn. Solo il prossimo anno, con la tecnologia a 45 nm perfettamente funzionante, Intel pro-

Shrink / affinamento

Presler • Yonah • Dempsey

Nuova microarchitettura

Intel Core

Shrink / affinamento

Penryn

Nuova microarchitettura

Nehalem

Avanzamenti architetturali

2 ANNI

2 ANNI

IN PROFONDITÀ

CPU

65

nm

45

nm

Gesher

22 nm

Nehalem-c

Nehalem

32 nm

Penryn

Core

45 nm

2 ANNI

65 nm

Shrink / affinamento

Westmere

Nuova microarchitettura

Gesher

90 nm

32

nm

2004

2005

2006

Nuova architettura

Nuovo processore

2007

2008

2009

2010

2011

2012

Anni

Evoluzione architetturale

Evoluzione tecnologia costruttiva

Per la sua politica di update Intel ha coniato il termine tick-tock (equivalente del tic-tac italiano). Nelle roadmap

della casa di Santa Clara lo stadio tick è rappresentato dalla fase di miglioramento dell’architettura pre-esistente,

miglioramento che passa per l’ottimizzazione e la riduzione del processo produttivo. Lo stadio tock prevede invece

il lancio di un’architettura completamente nuova, però realizzata con il processo produttivo della fase precedente.

porrà la nuova architettura, vera

rivoluzione rispetto all’attuale.

Transistor,

come funzionano

I transistor utilizzati nei microprocessori moderni sono prodotti attraverso una tecnica litografica,

analizzata in un box a parte.

La loro forma e composizione è rimasta immutata negli ultimi quarant’anni, con qualche piccolo accorgimento tecnico di minore importanza implementato negli anni

ottanta e novanta.

La vera evoluzione nella loro fab bricazione è stata la drastica riduzione delle dimensioni, che tridimensionalmente si dimezza ogni

Fab 32, in Arizona, una delle 3 fabbriche Intel attive nella produzione a 45 nm.

due anni circa. Un singolo transistor funziona praticamente come

un interruttore a tre contatti: lascia

fluire una corrente elettrica tra

due di essi solo se è stato “acceso”

attraverso il terzo contatto. Nei

L’evoluzione dei processi produttivi

Nome produttivo

Processo litografico

Anno di introduzione

Diametro wafer (mm)

P860

P1262

P1264

P1266

P1268

130 nm

2001

200/300

90 nm

2003

300

65 nm

2005

300

45 nm

2007

300

32 nm

2009

300

70

PC Professionale - luglio/agosto 2007

processori moderni si utilizza la

tecnologia Cmos (Complementary

Metal Oxide Semiconductor) che

si basa sull’utilizzo contemporaneo di due tipi distinti di transistor,

chiamati Nmos (Negative Mos) e

Pmos (Positive Mos). Questi ultimi

si differenziano per il segnale di

accensione: nel primo si ha passaggio di corrente quando la tensione sul terzo contatto supera una

certa soglia, nel secondo quando

la tensione è al di sotto di essa.

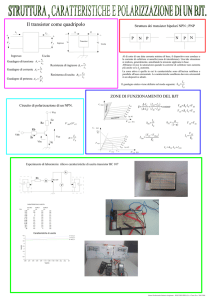

Fisicamente sono costituiti da un

IN PROFONDITÀ

CPU

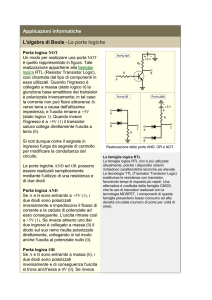

Strato a bassa

resistenza

Strato a bassa

resistenza

Elettrodo del Gate

(polisilicio)

Elettrodo del Gate

(Metal Gate)

Dielettrico

del Gate (SiO2)

Dielettrico del

Gate (High-K)

Source

Drain

Substrato di silicio

Transistor tradizionale

substrato di silicio, un semiconduttore che in base alle esigenze può

funzionare sia come un normale

conduttore elettrico sia come un

isolante.

Ai lati del transistor sono poste

d u e r e g i o n i p a r t i c o l a r i , che rappresentano i due contatti attraverso i quali fluisce la corrente, chiamati source e drain, rispettivamente la sorgente della corrente e la

sua destinazione. Queste regioni

sono costituite da silicio opportunamente drogato con altri elementi chimici per garantire una migliore conducibilità elettrica.

Nella zona centrale, detto canale,

fluisce la corrente elettrica quando

il transistor viene attivato ed è il

solo punto interno del transistor

Source

Drain

Substrato di silicio

Transistor Metal Gate e High-K.

che è stato leggermente modificato negli ultimi anni.

Il silicio, una volta puro, viene oggi depositato su una base di un altro semiconduttore caratterizzato

da un reticolo cristallino con maglie più larghe o più strette rispetto al silicio in base al tipo di transistor che si vuole ottenere, Nmos o

Pmos. Con questo deposito si ottiene uno stiramento o una compressione del reticolo cristallino

del silicio, che va a uniformarsi a

quello sottostante garantendo una

maggiore (o minore) mobilità degli elettroni e una migliore conducibilità elettrica, mantenendo però

inalterate tutte le altre caratteristiche fisiche del silicio.

Questa tecnica, utilizzata per la

prima volta da Intel nel 2002,

prende il nome di Strained Silicon.

Sopra al canale di conduzione viene depositato un piccolissimo strato di diossido di silicio, con proprietà isolanti atte a impedire che

la tensione applicata al contatto

superiore (chiamato gate) generi

una corrente che possa impedire il

corretto funzionamento del transistor. Sopra a esso si trova l’elettrodo del gate, costituito in polisilicio

cristallino e drogato in maniera

differente in base al tipo di transistor desiderato, Nmos o Pmos.

L’ultima parte superiore, un piccolo strato di tungsteno con una bassissima resistenza elettrica, serve a

migliorare le interconnessioni con

l’esterno, ed è stata introdotta verso la fine degli anni ottanta.

Transistor,

perché cambiano

Da più di quarant’anni la costruzione di questi microscopici interruttori elettronici non ha subito

modifiche sostanziali, la ricerca associata era volta quasi esclusivamente alla riduzione delle dimensioni, attraverso tecniche di produzione sempre più complesse. Negli

Da sinistra a destra: nel processo a 130 nm del 2001 la distanza tra source e drain, detta larghezza di canale, era di 70 nm,

mentre lo spessore del dielettrico isolante del gate di 1,5 nm. Nel 2003, con il passaggio a 90 nm la larghezza di canale si è ridotta

a 50 nm, e lo spessore a 1,2 nm. Due anni dopo, con i 65 nm le misure del transistor si sono ridotte a 35 nm e 1,2 nm. Nel 2007,

con il passaggio ai 45 nm si rivoluzionano ancora le misure: adesso la larghezza di canale è di 20 nm e lo spessore sale a 3 nm.

72

PC Professionale - luglio/agosto 2007

IN PROFONDITÀ

CPU

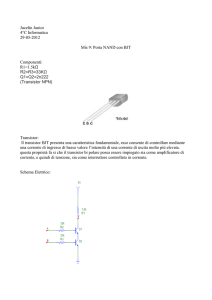

Il processo fotolitografico

L

a produzione dei microprocessori avviene in strutture molto

particolari solitamente chiamate

Fabs (Fabrication Facilities) , che

possono essere immaginate come

una via di mezzo tra una fabbrica

e un laboratorio scientifico. Tutto il

processo di produzione avviene

internamente e consiste in più di

300 singoli passi, in ognuno dei

quali possono venire utilizzate varie sostanze chimiche, vari tipi di

gas e anche la luce.

Nonostante l’enorme complessità

della produzione il componente

base utilizzato dai transistor è il

comune silicio, l’elemento chimico

più abbondante sulla terra fatta

eccezione per l’ossigeno.

Il silicio viene innanzitutto trattato

c hi micament e per renderlo il più

puro possibile (fino al 99,9999%) e

poi aggregato in cilindri dal diametro di circa 40 centimetri. All’inizio della produzione questi cilindri vengono “affettati” e rifiniti, fino alle dimensioni corrette per l’inizio del procedimento. Nascono

quindi i wafer, dallo spessore di

poco meno di un millimetro e diametro di 30 centimetri. In seguito

essi vengono rifiniti e levigati a

specchio, portando le due facce

opposte a una planarità e un parallelismo che non ha eguali nell’industria civile.

Il lungo e complesso processo di

produzione può essere comunque

suddiviso in tappe fondamentali,

sulle quali andiamo a soffermarci.

La prima fase, non presente in figura, è quella di isolamento e di

coating; sul wafer di silicio purissimo viene fatto crescere uno strato

di diossido di silicio mediante una

cottura ad altissima temperatura

in presenza di ossigeno molecolare libero. Nel passo successivo il

tutto viene ricoperto da un sottile

strato di un materiale detto photoresist che, esattamente come una

pellicola fotografica, cambia il

proprio stato molecolare quando

esposto a una fonte di luce, in

questo caso ultravioletta. Successivamente sull’intera superficie

del wafer viene posizionata una

maschera che definisce le forme

del circuito, allineata su di esso in

modo perfetto da una macchina ad

altissima precisione. La presenza

della maschera fa si che, dopo

un’esposizione a raggi ultravioletti, solo la parte del photoresist non

coperta cambi chimicamente,

mantenendo inalterata la porzione

nascosta.

L’effetto della modifica chimica

del photoresist è di legarsi indissolubilmente al materiale sottostante, creando un composto parzialmente solubile che viene poi rimosso attraverso l’immersione in

un fluido apposito con un processo

chiamato etching.

La rimanente parte del photoresist

non esposta ai raggi ultravioletti

può essere tolta in maniera molto

semplice lasciando inalterata la

porzione sottostante.

Dopo l’intero processo sul wafer di

silicio rimane impressa la sagoma

della maschera formata dal primo

materiale depositato sullo stesso,

in maniera simile a quanto accade

sulla pellicola di una macchina fotografica.

Raggi ultravioletti

Maschera

Photoresist

Diossido di silicio

Wafer

Maschera

Photoresist

Diossido di silicio

Wafer

Dopo l’incisione

Diossido di silicio

Wafer

Dopo la rimozione del photoresis

Polisilicio

Questo è però solamente il primo

livello, molti altri vengono aggiunti in seguito attraverso la stessa

tecnica ma con materiali di partenza differenti, creando un disegno tridimensionale sulla superficie del wafer di silicio. Semplificando in procedimento come mostrato in figura il passo successivo

è quello di aggiungere il dielettrico del gate, basato sul diossido di

silicio o sulla tecnologia High-K,

in base al processo produttivo utilizzato. La porzione di silicio puro

rimasta allo scoperto viene a questo punto drogata con elementi

chimici capaci di alterare il modo

in cui il silicio conduce la corrente

elettrica, attraverso un bombardamento di ioni nelle zone desidera-

74

PC Professionale - luglio/agosto 2007

Diossido di silicio

Ossido del gate

Wafer

Aggiunta dei livelli

te. Dopo che la struttura base è

completa essa viene rivestita da un

materiale isolante, attraverso una

opportuna maschera che lascia libere solo le zone che diverranno i contatti fisici del transistor.

I contatti vengono poi rivestiti da un

m e t a l l o a bassa resistenza come il

tungsteno e sopra di essi vengono

finalmente creati i contatti e le in-

Polisilicio

Diossido di silicio

Silicio drogato

Wafer

Drogaggio

Gate

Strato isolante

aggiuntivo

Wafer

Diossido di silicio

Silicio drogato

Polisilicio

Creazione dei contatti

Tungsteno

Strato isolante

aggiuntivo

Wafer

Diossido di silicio

Silicio drogato

Polisilicio

Aggiunta del metallo

Rame

Source

Drain

Canale

Flusso di elettroni

Completamento del transistor

ultimi anni questa drastica riduzione dei formati ha portato alla

costruzione di transistor dalle dimensioni di qualche centinaio di

atomi, con la conseguente comparsa di effetti che non era possibile immaginare anche solo qualche decennio fa.

Gli ultimi processi produttivi di Intel possono dare un’idea di questa

riduzione delle dimensioni, e aiutano a capire contro quale muro

tecnologico ci si trovi attualmente.

Nel processo a 130 nm del 2001 la

distanza tra il source e il srain, anche detta larghezza di canale, era

di 70 nanometri, mentre lo spessore del dielettrico isolante del gate

di 1,5 nm. Nel 2003, con il passaggio a 90 nm la larghezza di canale

si è ridotta a 50 nm, ed il dielettrico a 1,2 nm. Due anni dopo, con i

65 nm le misure del transistor si

sono ridotte a 35 nm e 1,2 nm.

Da notare come la distanza tra il

source e il drain riesca ancora a

scalare insieme al processo produttivo, mentre le dimensioni del

dielettrico non riescono a diminuire oltre una certa soglia. Per la prima volta infatti insieme a una

nuova tecnologia di produzione

non è stata diminuita l’ampiezza

del dielettrico sul gate, uno dei valori più importanti nel determinare le prestazioni di un transistor.

Per spiegare i motivi che hanno

portato a questo occorre però una

breve descrizione introduttiva del

funzionamento di un normale

transistor. Alla base di tutto c’è il

segnale di accensione applicato al

gate, differente in base alla tecnologia P o Nmos come descritto prima; quando la condizione di accensione viene applicata, nel canale si viene a creare un piccolo

terconnessioni attraverso delle micro piste in rame, un ottimo conduttore elettrico.

Le prime celle memoria Sram a 45 nm:

oltre 1 miliardo di transistor su 119 mm2.

campo elettrico che ne modifica le

proprietà di conduzione permettendo il passaggio della corrente

elettrica tra il source e il drain. Più

è sottile lo strato isolante sul gate

e meno intensa dovrà essere la

tensione applicata per formare (o

inibire) un campo elettrico adeguato, con ovvi risparmi dal punto

di vista energetico.

Una minore tensione di soglia permette anche un notevole aumento

prestazionale, riducendo il tempo

richiesto dal transistor per la commutazione tra i due stati possibili.

La dimensione di questo isolante

dielettrico non potrà però essere

ridotta troppo, oltre un certo limite

inizierà a scorrere una corrente tra

il gate e i due contatti inferiori, ge-

Prima di applicare

alle Cpu il processo

produttivo

a 45 nm, Intel

lo ha affinato con

la realizzazione

di celle di memoria

Sram su wafer

da 300 mm.

Tutto il procedimento avviene in

p a r a l l e l o su un wafer di 30 cm di

diametro, utilizzando maschere

estremamente complesse che riproducono sullo stesso varie centinaia

di processori e di conseguenza svariati miliardi di transistor.

75

PC Professionale - luglio/agosto 2007

IN PROFONDITÀ

CPU

nerata dalla tensione applicata all’elettrodo superiore.

Questo fenomeno prende il nome

di current leakage ed è presente

da molti anni in tutti i circuiti basati sui transistor di tipo Cmos.

Verso la fine degli anni novanta

questa corrente parassita non veniva considerata un problema, la

sua intensità era infatti di molte

volte inferiore a quella delle altre

correnti presenti nel circuito.

Negli anni, con la progressiva ri duzione dello strato dielettrico, tale corrente ha iniziato a pesare

sempre di più sul precario bilancio

energetico dei processori, sempre

più bisognosi di energia elettrica a

causa del numero sempre maggiore di transistor utilizzati. Il punto di

svolta si ebbe nel 2003, con il passaggio da parte di Intel dalla tecnologia di produzione a 130 nm a

quella a 90 nm; lo spessore dello

strato dielettrico venne portato da

1,5 nm a 1,2 nm causando un incremento tangibile delle perdite

dovute alla corrente parassita. La

generazione di processori basati

su quel processo produttivo viene

infatti ricordata come una tra le

più esigenti in termini di richieste

energetiche, in parte consumate

da questa corrente parassita con la

dielettrico, rimasto fermo a 1,2 nm.

Una riduzione delle dimensioni

del canale ha permesso di utilizzare un campo minore per attivare la

conduzione della corrente elettrica, limitando anche la poco desiderata corrente parassita. Il passaggio tecnologico al processo di

produzione a 45 nm imporrebbe

ora una riduzione ulteriore anche

dello spessore del dielettrico, soluzione non praticabile con i materiali utilizzati oggi.

Metal Gate

e dielettrico High-K

Ecco come appare al microscopio

uno dei nuovi transistor a 45 nm.

spiacevole conseguenza di una

temperatura di esercizio nettamente sopra alla media.

Con il successivo passaggio alla

tecnologia a 65 nm le cose sono

notevolmente migliorate, la riduzione delle dimensioni ha infatti

interessato solo la larghezza del

canale, ma non lo spessore del

Ridurre ulteriormente lo spessore

del dielettrico isolante ma senza

incrementare la corrente parassita:

la soluzione che Intel ha architettato per risolvere questo problema

si presenta come la più grande rivoluzione nella costruzione dei

transistor avvenuta negli ultimi

quarant’anni. Il processo produttivo a 45 nanometri che Intel si

appresta a introdurre nei prossimi mesi è infatti frutto di due innovazioni, senza di cui non sarebbe stato possibile produrre

transistor così piccoli in grado di

funzionare.

Le due innovative tecniche utilizzate prendono il nome di Metal

Euv (Extreme Uv Litography)

L

a fotolitografia attuale utilizza una luce ultravioletta

con lunghezza d’onda di 193 nm, evolvendosi in maniera parallela con la diminuzione della dimensione dei

transistor. Alla fine degli anni novanta la lunghezza d’onda era inferiore alle dimensioni minime presenti in un

transistor e il processo fotolitografico poteva avvenire senza particolari problemi.

Negli ultimi anni però la riduzione di questa lunghezza

d’onda non ha potuto mantenere il passo con quella delle

dimensioni dei transistor, dovendo ricorrere ad altre tecniche per impressionare componenti così piccole. Oggi si

riesce a costruire transistor a 45 nm con una luce a 193 nm

solamente utilizzando accorgimenti particolari, come l’aggiunta di lenti molto sofisticate in grado di concentrare la

lunghezza d’onda o l’immersione del wafer in un fluido

capace di concentrare a sua volta la luce ultravioletta.

Questa tecnica dovrebbe essere sufficiente fino al processo di produzione a 32 nm, previsto per il 2009, ma non si

76

crede possibile un suo utilizzo oltre questa nuova barriera

tecnologica. Per continuare a rispettare la legge di Moore

serve però ben altro, la riduzione delle dimensioni dei

transistor è troppo rapida per la tecnologia fotolitografica

attuale.La nuova frontiera prende il nome di Extreme UltraViolet Litography (Euv) e si basa sulla produzione di

luce a frequenze al limite della zona ultravioletta, a ridosso dei raggi X. Lo sviluppo della nuova tecnologia è affidato al consorzio Euv LLC che, guidato da Intel, annovera

tra i suoi membri anche AMD, IBM, Infineon, Micron Tecnology e Motorola.

La luce utilizzata in questo processo viene prodotta direttamente dal gas xeno, che riscaldato ad alte temperature

è in grado di emettere costantemente e con una coerenza

molto elevata (la coerenza è la proprietà della luce emessa da una sorgente di rimanere uguale alla precedente

per un certo tempo). La luce così prodotto viene riflessa da

PC Professionale - luglio/agosto 2007

Il Metal Gate consiste nella mo d i f i c a s o s t a n z i a l e del materiale

con il quale viene costruito il gate

del transistor; fino a oggi interamente costituito da silicio policristallino altamente drogato, dotato di una buona conducibilità

elettrica. L’utilizzo del solo silicio

drogato era dovuto al processo di

produzione, che per semplicità

impiegava solamente questo elemento senza aggiungerne di nuovi, cercando di mantenere un costo di produzione il più ridotto

possibile. Grazie a nuove fabbriche progettate appositamente

per impiegare un processo di

produzione differente sarà possibile utilizzare anche altri elementi e materiali nella produzione

microscopica, attraverso i processi litografici.

L’utilizzo di un gate basato su di

un metallo (differente per transistor N o Pmos) permette di ottenere un significativo aumento

dell’effetto di campo a parità di

tensione utilizzata, necessario ad

attivare il transistor. Questo permetterà di utilizzare tensioni inferiori e contemporaneamente di

ottenere effetti maggiori, con

“

“

Gate e High-K Dielectric.

Sul punto che trovate

alla fine di questa frase

potreste allineare 10.000

transistor realizzati con

processo a 45 nm.

grandi vantaggi sia nella velocità

di commutazione sia nel consumo energetico.

La seconda grande innovazione

consiste nell’eliminare anche

dalla parte isolante del gate il silicio, sostituendolo con un altro

materiale chiamato High-K. La

lettera K solitamente indica in ingegneria la capacità di un materiale di trattenere la carica elettrica al proprio interno, come farebbe una spugna con dell’acqua, e viene chiamata capacitanza. Il materiale utilizzato è basato

sull’elemento chimico Afnio, ed è

caratterizzato da ottime doti isolanti e da una elevatissima costante K, da cui prende il nome la

tecnologia High-K. La buona capacità isolante riduce i problemi

dovuti alle correnti parassite, e

grazie all’ottima capacità di trat-

tenere la carica elettrica permette un notevole aumento dell’effetto di campo a parità di tensione utilizzata.

I problemi riscontrati nei transi s t o r t r a d i z i o n a l i sono quindi di

molto ridimensionati con l’utilizzo di queste due tecnologie; e

permetteranno a Intel di iniziare

a breve la produzione di transistor con il nuovo processo a 45

nm, con enormi benefici sia in

termini prestazionali sia di dissipazione energetica. A confronto

con il già ottimo processo a 65 nm

i dati sono notevoli, le dimensioni

effettive tridimensionali sono dimezzate; quindi processori delle

stesse dimensioni possono contenere fino al doppio dei transistor.

A parità di consumi e spazio occupato la nuova generazione of-

Gas xeno eccitato

Specchio

numerosi piccoli specchi e può raggiungere la lunghezza d’onda di soli 13 nm, solo di poco superiore al

limite definito tra i raggi ultravioletti e i raggi X, posto

a 10 nm.

Una luce caratterizzata da una lunghezza d’onda così

piccola permetterà dunque di continuare a utilizzare

il processo fotolitografico anche nelle prossime generazioni di transistor, e dovrebbe venire impiegata per

la prima volta dopo il 2010 con il passaggio dai 32 nm

allo step successivo, i 22 nm. •

Luce con lunghezza

d’onda a 13 nanometri

Substrato di silicio

Circuiti a 22 nanometri

TECNOLOGIA OTTICA

Fascio di luce laser

Lente

Nel processo Euv il gas xeno eccitato si riflette

su una serie di specchi per generare un fascio di luce

con lunghezza d’onda molto più piccola di quella che

può essere ottenuta con le attuali tecnologie ottiche che

operano con un fascio laser e lenti.

luce con lunghezza d’onda a 193 nm

Substrato di silicio

Circuiti a 65 nanometri

77

PC Professionale - luglio/agosto 2007

IN PROFONDITÀ

CPU

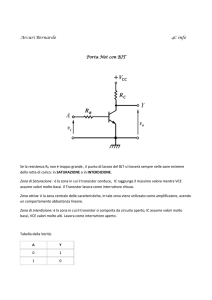

Roadmap delle future Cpu e microarchitetture Intel

2006

2007

2008+

Server / Workstation

Intel Itanium

Montecito

Montvale

Tukwila

Intel Xeon - MP

Intel Xeon 7300

Dunnington

Penryn

Intel Xeon - UP / DP

Intel Xeon (QC)

45nm QC

Intel Xeon (DC)

45nm DC

Client

Intel Core 2 - Desktop

Intel Core 2 Quad

45nm QC

Intel Core 2 Duo

Intel Core 2 - Mobile

45nm DC

Intel Core 2 Duo

45nm DC

65 nm Intel Core Arch.

45 nm Enhanced Intel Core Arch.

frirà prestazioni probabilmente

superiori integrando inoltre nuove caratteristiche tecniche, più

cache e il supporto a un set di

istruzioni più complesso, grazie

proprio al maggior numero di

transistor.

La potenza necessaria alla com mutazione di un transistor a 45 nm

è inferiore del 30% rispetto alle

versioni attuali a 65 nm e il passaggio on/off ha una velocità superiore del 20%. Il risultato più importante ottenuto da Intel è però la

drastica riduzione delle correnti

parassite grazie all’introduzione

del Metal Gate e del dielettrico

High-K. Il migliorato effetto di

campo permette una riduzione di

cinque volte della corrente parassita che può fluire costantemente

tra source e drain anche a dispositivo spento, contribuendo al risparmio energetico complessivo in

maniera considerevole. La corrente parassita che attraversa il gate

viene ridotta grazie alla minore

tensione operativa e al miglioramento del materiale dielettrico, risultando di ben dieci volte inferiore rispetto ai transistor attuali.

Nehalem

45 nm Nehalem Arch.

Conclusioni

Nei prossimi mesi saranno dunque molte le novità nel settore

dei microprocessori, sia da parte

Intel sia AMD. Alle porte è il lancio della nuova architettura AMD

basata su tecnologia a 65 nm, che

promette di raggiungere e superare le prestazioni dei processori

Core 2 Duo.

Intel d’altronde vuole cercare di

mantenere la superiorità prestazionale attuale con il lancio del

nuovo processo produttivo a 45

nm in abbinamento ai processori

con core Penryn.

È inevitabile chiedersi se e quando AMD avrà la possibilità di utilizzare un processo produttivo

avanzato quanto il nuovo 45 nm

di Intel. In realtà anche la casa di

Sunnyvale sta pianificando il

passaggio a questo nuovo processo, ma è sicuramente in ritardo di qualche mese rispetto al

concorrente diretto.

Intel continua invece con la pro p r i a e v o l u z i o n e rispettando alla

perfezione la scaletta pianificata,

anticipando anche in qualche ca-

78

PC Professionale - luglio/agosto 2007

so il lancio dei propri prodotti,

cercando di guadagnare quanto

più terreno possibile sul diretto

concorrente.

Dopo la presentazione di Penryn

nella seconda metà dell’anno tutti gli sforzi si concentreranno sulla prossima generazione di processori Intel e basati su di una architettura completamente nuova

(nome in codice Nehalem). La filosofia di Intel è dunque profondamente cambiata negli ultimi

anni, se all’inizio del millennio le

mosse dell’azienda di Santa Clara erano lente e prevedibili, con

la costante ricerca dell’aumento

della sola frequenza operativa;

oggi, con la promessa di una nuova architettura completa ogni

due anni, le cose sono nettamente diverse.

È quindi possibile che nei prossimi due o tre anni ci attendano più

novità ed evoluzioni tecnologiche

che nei sette trascorsi dall’inizio

del secolo, grazie all’introduzione

di nuovi processori dotati di caratteristiche e funzionalità completamente nuove. Non resta che

attendere.

•