Caso di studio 1: Progetto di un sistema su un chip

1

Caso di studio 1: Progetto di un sistema su un chip

In questo caso di studio

•

•

•

•

Progettazione di un sistema per la realizzazione su un chip FPGA

Come usare strumenti CAD

Come usare moduli parametrici

Cosa considerare tipicamente nella progettazione

Nel Capitolo 10 si è discusso l’uso di microcontrollori nei sistemi embedded. In un’applicazione embedded, è desiderabile usare quanti meno chip sia

possibile. Idealmente, un singolo chip potrebbe realizzare l’intero sistema.

Il termine sistema su un singolo chip (SOC) è in uso per designare questa

tecnologia. In applicazioni semplici, alcuni dei microcontrollori disponibili in commercio possono realizzare tutte le funzioni necessarie. Questo è

improbabile per applicazioni più complesse.

La progettazione di un microcontrollore per un’applicazione embedded

complessa e la sua realizzazione sotto forma di un singolo chip specifico è

un obiettivo ambizioso e costoso. È anche molto dispendioso in termini di

tempo. Eppure, il tempo di sviluppo per la maggior parte dei prodotti di consumo deve essere breve. Un chip che realizzi un intero sistema per una certa

applicazione si può sviluppare in un tempo molto più breve se il progettista

ha accesso a moduli con circuiti predefiniti che siano disponibili in una forma

facile da usare. Il circuito di un processore è uno dei moduli necessari. Tali

circuiti sono detti nuclei-processore (processor core) nella letteratura tecnica. Si può ottenere una varietà di nuclei-processore, mediante accordi per

le licenze, da un certo numero di aziende. Si possono ottenere altri moduli

per realizzare memoria, interfacce di ingresso/uscita, circuiti di conversione

A/D e D/A, o circuiti di elaborazione digitale di segnale, DSP (Digital Signal

Processing). Lo sviluppatore di un sistema completa quindi il progetto utilizzando i moduli disponibili e progettando il resto dei circuiti specifici per

l’applicazione.

I fornitori di nuclei-processore e di altri moduli vendono i progetti piuttosto che i chip. Essi forniscono la proprietà intellettuale, IP (Intellectual

Property) che altri possono usare per progettare i loro chip. Per facilitare lo

sviluppo di prodotti basati su IP, sono disponibili una varietà di strumenti di

assistenza alla progettazione, CAD (Computer-Aided Design).

Il costo di realizzazione di un chip progettato in modo personalizzato è un

fattore importante. La fabbricazione di tali chip è costosa e, sebbene offrano

prestazioni migliori e consumi ridotti, il loro costo può essere giustificato solo

Hamacher, Vranesic, Zaky, Manjikian, Introduzione all’architettura dei calcolatori 3e

© 2013 McGraw-Hill Education Italy S.r.l.

Caso di studio 1: Progetto di un sistema su un chip

2

se sono necessari un gran numero di chip per applicazioni specifiche. Una

possibilità alternativa è l’uso di tecnologia FPGA (Field Programmable Gate

Array), ovvero di matrici di porte logiche programmabili sul campo.

C1.1

Realizzazione FPGA

Le FPGA forniscono una piattaforma attraente per la realizzazione di sistemi

su singolo chip. A differenza dei chip microcontrollori disponibili in commercio, che forniscono al progettista una serie di unità funzionali predefinite,

i dispositivi FPGA permettono una completa libertà nel processo di progettazione. Essi permettono l’inclusione di moduli IP adatti e quindi la generazione del resto del sistema come desiderato. Questo si può realizzare con

relativa facilità. Una volta che il progetto è completato e collaudato, lo si può

realizzare in un dispositivo FPGA immediatamente.

La capacità delle FPGA è drammaticamente cresciuta. Un singolo chip

FPGA può realizzare un sistema che comprende centinaia di migliaia di porte

logiche. Tali chip sono sufficientemente grandi da poter realizzare le funzionalità tipiche di un microcontrollore e altri circuiti necessari per un’applicazione embedded complessa.

In questo caso di studio si esaminano le questioni relative all’impiego di

FPGA in un ambiente embedded. Per rendere la discussione quanto più pratica possibile, si considera la tecnologia fornita da Altera Corporation, che è

uno dei principali fornitori di dispositivi FPGA e software CAD di supporto.

C1.1.1

Dispositivi FPGA

La struttura di base delle FPGA è spiegata in Appendice A. I dispositivi FPGA

contengono un gran numero di elementi logici e risorse di cablaggio versatili

che si possono usare per interconnetterli. Di solito contengono anche una

notevole quantità di memoria che si può usare per realizzare le parti di RAM

e ROM di un sistema embedded se i requisiti di dimensione della memoria

non sono troppo grandi. Molte FPGA includono anche circuiti moltiplicatori,

che sono particolarmente utili nelle applicazioni DSP.

Un dispositivo FPGA va programmato per realizzare un particolare progetto. Gli elementi logici includono interruttori programmabili da impostare

per realizzare le funzioni logiche desiderate. Tipicamente, si può programmare un elemento logico per realizzare funzioni logiche di quattro, cinque

o sei variabili. L’elemento logico comprende inoltre un flip-flop per rende-

Hamacher, Vranesic, Zaky, Manjikian, Introduzione all’architettura dei calcolatori 3e

© 2013 McGraw-Hill Education Italy S.r.l.

Caso di studio 1: Progetto di un sistema su un chip

3

re possibile la realizzazione di registri e macchine a stati finiti. Le linee di

interconnessione contengono anche interruttori programmabili, che si usano

per interconnettere gli elementi logici per realizzare il circuito desiderato. Il

processo di programmazione per l’impostazione degli interruttori viene detto

configurazione del dispositivo FPGA.

Nella maggior parte dei dispositivi FPGA, lo stato di ogni interruttore programmabile si trova in una cella SRAM del tipo discusso nel Paragrafo 8.2.2.

Poiché le celle SRAM mantengono il loro stato solo finché l’FPGA ha l’alimentazione, tali FPGA sono volatili. Se si toglie l’alimentazione si deve

riconfigurare il dispositivo quando la si fornisce nuovamente. Per configurare

l’FPGA, si devono caricare le informazioni di configurazione nel dispositivo. Questo viene fatto tipicamente utilizzando un altro chip, detto dispositivo di configurazione, che mantiene le informazioni richieste in una memoria

di tipo Flash. Ogni volta che si fornisce l’alimentazione, il dispositivo di

configurazione programma automaticamente l’FPGA.

Di solito la memoria Flash del dispositivo di configurazione è abbastanza

grande da contenere non solo i dati di configurazione per i circuiti da realizzare nell’FPGA, ma anche informazioni aggiuntive che possono includere dati o

codice. Se nell’FPGA si realizza un nucleo-processore, allora nel dispositivo

di configurazione si può memorizzare del codice che il processore eseguirà.

C1.1.2

La scelta del processore

La componente significativa di qualsiasi sistema su chip è il nucleo-processore.

Esistono due alternative distinte per i sistemi basati su FPGA. Una riguarda

un processore che è definito in software e realizzato in una FPGA allo stesso

modo di qualsiasi altro circuito. L’altra comporta un chip FPGA specializzato

che ha un nucleo realizzato sul chip al momento della fabbricazione.

Nucleo-processore software

La soluzione più flessibile è quella di realizzare un modulo software scritto in

un linguaggio di descrizione dell’hardware, come Verilog o VHDL, che specifica un processore parametrico. Il progettista di un sistema embedded può impostare i parametri per ottenere un processore con le caratteristiche adatte per

l’applicazione prevista. Per esempio, un parametro riguarda la configurazione

della cache, dove le scelte possono essere:

• nessuna cache;

• cache per le istruzioni, ma non per i dati;

• cache per le istruzioni e per i dati.

Hamacher, Vranesic, Zaky, Manjikian, Introduzione all’architettura dei calcolatori 3e

© 2013 McGraw-Hill Education Italy S.r.l.

Caso di studio 1: Progetto di un sistema su un chip

4

Un altro parametro può riguardare l’inserimento di circuiti moltiplicatori e divisori nel processore. Le operazioni di moltiplicazione e divisione si possono

realizzare in hardware, tuttavia si possono anche realizzare in software. Realizzarle in hardware fa uso di più risorse FPGA, ma migliora notevolmente le

prestazioni.

Nucleo-processore hardware

Un’alternativa all’approccio software al nucleo-processore è di realizzare il

processore direttamente come un modulo hardware sul chip, creando cosı̀ una

FPGA specializzata. Questo produce un sistema con prestazioni più elevate.

Il costo di tali FPGA è superiore al costo dei dispositivi FPGA regolari.

C1.2

Strumenti per la progettazione assistita dal

calcolatore

I produttori di dispositivi FPGA forniscono potenti strumenti CAD che rendono il compito di progettare sistemi embedded relativamente facile. Una

varietà di moduli predefiniti sono forniti in forma parametrica. Il progettista crea un sistema inserendo questi moduli e specificando i parametri per

soddisfare i requisiti dell’applicazione. Esempi di tali moduli sono:

• nuclei-processore,

• moduli di memoria e interfacce,

• interfacce di I/O parallele,

• interfacce di I/O seriali,

• circuiti temporizzatori/contatori.

Tali moduli possono essere sufficienti per realizzare tutte le funzioni necessarie in un sistema embedded desiderato. Se non lo sono, allora si devono

progettare e includere nel sistema ulteriori circuiti specializzati.

Tipicamente, prima si specifica un sottosistema che comprende un nucleoprocessore e altri moduli parametrici. Si usa uno strumento CAD per generare

un modulo che realizza il sottosistema. Questo modulo è definito in un linguaggio di descrizione dell’hardware. Se ne crea quindi un’istanza nel progetto complessivo, insieme ad altri eventuali circuiti specifici per l’applicazione

che siano stati creati. Infine, si usa un altro strumento CAD per sintetizzare e

realizzare il progetto complessivo in una forma utilizzabile per configurare il

dispositivo FPGA.

Oltre al dispositivo FPGA, è necessario includere i componenti esterni necessari per completare il sistema, come interruttori, schermi e chip di memoria

Hamacher, Vranesic, Zaky, Manjikian, Introduzione all’architettura dei calcolatori 3e

© 2013 McGraw-Hill Education Italy S.r.l.

Caso di studio 1: Progetto di un sistema su un chip

5

aggiuntiva. Tali componenti vanno collegati ai piedini appropriati sulla FPGA. Si discuteranno questi aspetti nel contesto di un esempio di progettazione

nel Paragrafo C.3.

Per dare al lettore un esempio specifico di strumenti CAD e moduli per

dispositivi FPGA, si considerano brevemente gli strumenti forniti da Altera

Corporation. Tutte le informazioni sulla sua tecnologia e sugli strumenti sono

disponibili sul sito web di Altera: www.altera.com.

C1.2.1

Strumenti CAD Altera

I principali strumenti CAD Altera sono noti come software Quartus II. Essi

comprendono una gamma completa di strumenti necessari per progettare e

realizzare un sistema digitale in un dispositivo FPGA. Si può usare uno di

questi strumenti, il SOPC Builder (generatore SOPC), per progettare sistemi

che comprendono un nucleo-processore. Questo strumento fornisce un certo

numero di moduli parametrici che si possono usare nel sistema progettato.

Per illustrare la loro natura, si considereranno quattro di questi moduli.

Processore Nios II

Il processore Nios II è descritto negli approfondimenti applicativi dei capitoli

2 e 3. Per la realizzazione su FPGA, è fornito in tre versioni: economica,

standard e veloce. La versione economica è la più semplice e meno costosa

da realizzare (in termini di risorse FPGA). Essa ha anche le prestazioni più

basse. Non incorpora alcuna cache, non è in pipeline e non usa predizioni

di salto. Si ottengono prestazioni migliori con la versione standard, che è

dotata di una cache per le istruzioni, è in pipeline e usa la predizione statica di

salto. Si ottengono le migliori prestazioni con la versione veloce, che include

entrambe le cache per istruzioni e dati e usa la predizione dinamica di salto.

Vi sono diversi parametri che un progettista può specificare, comprese

le dimensioni delle cache per istruzioni e dati. I nuclei-processore Nios II

sono sufficientemente piccoli da occupare solo una piccola parte di un dispositivo FPGA. È possibile realizzare fino a dieci nuclei Nios II su una FPGA

relativamente piccola.

Memoria

Si possono usare blocchi di memoria in un dispositivo FPGA per realizzare

le cache e una porzione della memoria principale. La porzione della memoria

principale realizzata in questo modo viene detta memoria su chip. Si può

configurare questa memoria in vari modi: la si può realizzare come memoria

Hamacher, Vranesic, Zaky, Manjikian, Introduzione all’architettura dei calcolatori 3e

© 2013 McGraw-Hill Education Italy S.r.l.

6

Caso di studio 1: Progetto di un sistema su un chip

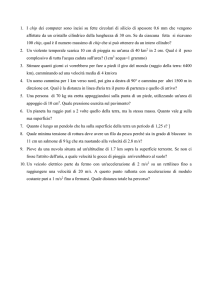

Spiazzamento

dell’indirizzo

(n – 1)

(in byte)

0

0

Dati di ingresso/uscita

4

Controllo della direzione di ciascuna linea di ingresso

8

Abilitazione delle interruzioni di ciascuna linea di ingresso

12

Direzione del fronte in ciascuna linea di ingresso

Dati

Direzione

Maschera-interruzioni

Cattura-fronte

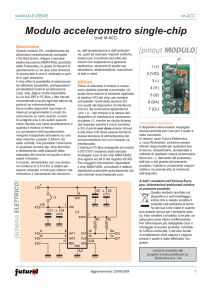

Figura C1.1: Registri nell’interfaccia PIO.

di tipo RAM o ROM e se ne possono specificare le dimensioni e la lunghezza

di parola in fase di progettazione.

Se la memoria su chip non è abbastanza grande da contenere il software

necessario in un’applicazione embedded, allora occorre fornire memoria aggiuntiva utilizzando chip di memoria esterni. Il SOPC Builder facilita la generazione di controllori e interfacce necessarie per collegare un sistema realizzato nella FPGA a una varietà di componenti di memoria esterni, quali SRAM,

SDRAM e dispositivi Flash.

Interfaccia di I/O parallela

Un’interfaccia parallela, detta PIO, è un modulo parametrico che si può usare

sia per funzioni di ingresso che di uscita. In fase di progettazione si può

selezionare la porta dati per servire come:

• porta di ingresso,

• porta di uscita,

• porta bidirezionale.

Se si sceglie l’opzione bidirezionale, allora le linee di dati PIO si devono

collegare a piedini di tipo tristate della FPGA.

Il processore accede a una PIO come a un’interfaccia con unificazione

degli spazi di indirizzamento di memoria e I/O e comunica con essa nel modo

descritto nel Capitolo 3. I registri della PIO sono mostrati in Figura C1.1. La

dimensione n del registro è un parametro specificato in fase di progettazione

nell’intervallo da 1 a 32. I registri vengono utilizzati come segue.

• Il registro Dati contiene n bit di dati che sono trasferiti fra il processore e

l’interfaccia PIO.

Hamacher, Vranesic, Zaky, Manjikian, Introduzione all’architettura dei calcolatori 3e

© 2013 McGraw-Hill Education Italy S.r.l.

Caso di studio 1: Progetto di un sistema su un chip

7

• Il registro Direzione determina la direzione di trasferimento (ingresso o

uscita) per ciascuna delle n linee di dati quando si realizza una porta bidirezionale.

• Il registro Maschera-interruzioni è utilizzato per abilitare le interruzioni

dalle linee di ingresso collegate alla PIO. Si possono sollevare richieste di

interruzioni individuali su ciascuna delle n linee di ingresso possibili.

• Il registro Cattura-fronte indica variazioni di valori logici rilevate nei segnali sulle linee di ingresso collegate alla PIO. Il tipo di fronte (ascendente

o discendente) che viene rilevato è specificato in fase di progettazione.

Le linee che collegano la PIO a un dispositivo I/O si possono configurare

individualmente. Se la PIO serve solo come porta di ingresso, tutte le n linee

sono configurate come ingressi in fase di progettazione. Analogamente, per

una porta di uscita, tutte le linee sono configurate come uscite. In questi casi,

il registro Direzione non è necessario, e non è realizzato nel circuito generato.

Per una porta bidirezionale il registro Direzione è incluso; quando il valore

del suo bit k è uguale a 1 (0), la linea k della porta funziona come uscita al

(ingresso dal) dispositivo di I/O collegato.

Quando la PIO è usata come porta di ingresso, il registro Dati contiene i

valori logici attualmente presenti sulle linee di ingresso. Si possono rilevare

variazioni nei valori logici sulle linee di ingresso mediante il registro Catturafronte. In fase di progettazione, è possibile specificare che i bit di questo

registro siano impostati a 1 quando si ha un fronte nel segnale di ingresso. Il

fronte si può specificare come: ascendente, discendente, o qualsiasi dei due.

I bit del registro Cattura-fronte sono azzerati da un’istruzione di programma

che scrive uno zero nel registro.

Il registro Maschera-interruzioni consente di abilitare e disabilitare le interruzioni. Scrivendo 1 nella posizione del bit k del registro si abilitano le

interruzioni causate dall’attività sulla linea di ingresso k. Le interruzioni

possono essere:

• sensibili al livello, nel qual caso viene sollevata una richiesta di interruzione

quando il segnale su una qualsiasi linea di ingresso abilitata ha valore 1;

• sensibili al fronte, nel qual caso viene sollevata una richiesta di interruzione

quando un qualsiasi bit abilitato nel registro Cattura-fronte è uguale a 1.

Si noti che gli indirizzi dei registri PIO in Figura C1.1 sono distanziati di

quattro, indipendentemente dalla lunghezza n. Cosı̀, gli indirizzi dei registri

sono allineati alla parola.

Hamacher, Vranesic, Zaky, Manjikian, Introduzione all’architettura dei calcolatori 3e

© 2013 McGraw-Hill Education Italy S.r.l.

8

Caso di studio 1: Progetto di un sistema su un chip

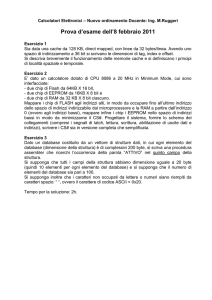

Temporizzatore di intervallo

Il modulo temporizzatore fornisce una funzionalità simile a quella del cronometro descritto nel Problema risolto 3.2 dell’Eserciziario. Il suo componente

principale è un contatore il cui contenuto è decrementato di uno a ogni ciclo

del clock. Si può specificare che il contatore sia a 32 o 64 bit. In questa

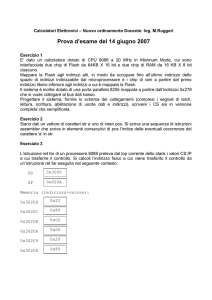

discussione si assumerà che il contatore abbia 32 bit. L’interfaccia del temporizzatore di intervallo ha i registri rappresentati in Figura C1.2. Ogni registro

ha 16 bit. Nel registro di stato si usano solo due bit:

• ESEGUI è uguale a 1 quando il contatore è in esecuzione, altrimenti è

uguale a 0; questo bit non è interessato se il processore scrive nel registro

di stato;

• TO è il bit di timeout; è impostato a 1 quando il contatore raggiunge lo 0 e

resta impostato a 1 fino a quando il processore lo annulla scrivendo uno 0

in esso.

Nel registro di controllo, si usano quattro bit:

Spiazzamento

dell’indirizzo

15

(in byte)

0

4

4

3

2

1

0

RUN

TO

STOP START CONT ITO

8

Valore iniziale del contatore (16 bit inferiori)

12

Valore iniziale del contatore (16 bit superiori)

16

Valore istantaneo del contatore (16 bit inferiori)

20

Valore istantaneo del contatore (16 bit superiori)

Registro di stato

Registro di controllo

Figura C1.2: Registri nell’interfaccia del temporizzatore di intervallo.

• ARRESTO è impostato a 1 per fermare il contatore;

• AVVIO è impostato a 1 per far sı̀ che il contatore si avvii;

• CONT determina il comportamento del contatore quando raggiunge 0: se

CONT=0, il contatore si ferma quando raggiunge 0; se CONT=1, il contatore ricarica il valore di conteggio iniziale e continua a contare;

Hamacher, Vranesic, Zaky, Manjikian, Introduzione all’architettura dei calcolatori 3e

© 2013 McGraw-Hill Education Italy S.r.l.

Caso di studio 1: Progetto di un sistema su un chip

9

• ITO abilita le interruzioni quando è impostato a 1.

Si deve caricare il valore di conteggio iniziale in due operazioni di scrittura a

16 bit. Si usano i registri di valore istantaneo del contatore per ottenere un’istantanea del contenuto del contatore mentre è in esecuzione. Un’operazione

di scrittura su uno qualsiasi dei due registri fa scattare l’istantanea, il che significa che il contenuto corrente del contatore è caricato nei registri di valore

istantaneo. Questi registri si possono poi leggere in modo usuale.

Oltre alla possibilità di utilizzare il valore iniziale di conteggio per definire

un periodo di timeout, si può specificare un periodo di timeout predefinito in

fase di progettazione. Il periodo di tempo predefinito è usato se il valore di

conteggio iniziale è zero.

Si genera una richiesta di interruzione quando TO=1 e ITO è impostato a

1. Per cancellare questa richiesta, il processore deve scrivere uno 0 in TO.

Nel prossimo paragrafo, si utilizzeranno i moduli di cui sopra in un esempio di progettazione completo.

C1.3

Esempio di orologio sveglia

In questo paragrafo si presenta un esempio dettagliato di sistema embedded.

Si mostra come si può realizzare una sveglia utilizzando la tecnologia FPGA.

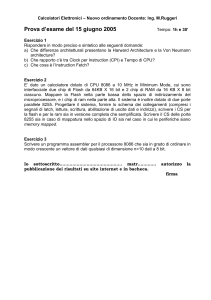

La sveglia, mostrata in Figura C1.3, ha le seguenti caratteristiche:

• vi sono quattro schermi a 7 segmenti che indicano l’orario in ore e minuti,

• si usa un interruttore scorrevole on/off per attivare la funzione di allarme,

• si usano due interruttori scorrevoli per abilitare l’impostazione dell’orario

attuale e dell’ora di sveglia,

• si usano due interruttori a pulsante per impostare le ore e i minuti,

• un LED indica che l’allarme è attivato,

• due LED, disposti verticalmente, creano i due punti che separano ore e

minuti,

• si emette un ronzio quando l’interruttore scorrevole dell’allarme è attivato

e si raggiunge l’ora di sveglia.

C1.3.1

Vista di utente del sistema

La Figura C1.3 mostra la sveglia come è vista dall’utente. Gli schermi a

sette segmenti, del tipo illustrato in Figura P3.3a dell’Eserciziario, indicano l’orario, mostrato nell’intervallo da 00:00 fino a 23:59. Il funzionamento

dell’orologio è il seguente:

Hamacher, Vranesic, Zaky, Manjikian, Introduzione all’architettura dei calcolatori 3e

© 2013 McGraw-Hill Education Italy S.r.l.

Caso di studio 1: Progetto di un sistema su un chip

Ora

Minuto

10

Imposta Imposta

orario orario Allarme

attuale allarme on/off

Allarme

ON

Figura C1.3: Vista di utente della sveglia.

• quando si fornisce l’alimentazione, l’orario del giorno e l’orario di allarme

sono azzerati;

• si imposta l’orario del giorno attivando l’interruttore scorrevole Imposta

orario attuale e quindi impostando il tempo mediante i pulsanti Ora e

Minuto: ogni volta che si preme un pulsante, l’orario visualizzato viene

incrementato di uno;

• l’orario di sveglia è impostato allo stesso modo quando si attiva l’interruttore Imposta orario allarme;

• si attiva l’allarme mediante l’interruttore Allarme on/off ; ciò fa sı̀ che il

corrispondente LED si accenda;

• l’altoparlante emette un ronzio quando si raggiunge l’orario di sveglia con

l’interruttore di allarme attivato.

C1.3.2

Definizione del sistema e generazione

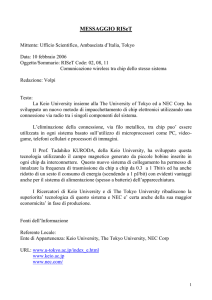

L’obiettivo qui è di realizzare la sveglia con un chip FPGA e componenti

esterni che comprendono: interruttori scorrevoli, pulsanti, schermi a 7 segmenti, LED e un altoparlante. La Figura C1.4 illustra il sistema desiderato. Il

processore è il Nios II. La memoria su chip è sufficientemente grande per soddisfare le esigenze della presente applicazione, persino in chip FPGA molto

piccoli. I componenti esterni sono collegati tramite interfacce PIO. Vi sono due cronometri. Uno è progettato per fornire intervalli di un minuto, da

utilizzare per aggiornare l’orario attuale. L’altro serve a generare un’onda

quadra che produce un ronzio. Si realizzano i cronometri usando il modulo

Temporizzatore di intervallo descritto nel Paragrafo C1.2.1. Si assume che gli

interruttori scorrevoli generino un segnale logico 1 quando attivati. Gli interruttori a pulsante sono antirimbalzo e generano un segnale logico 0 quando

vengono pigiati.

Hamacher, Vranesic, Zaky, Manjikian, Introduzione all’architettura dei calcolatori 3e

© 2013 McGraw-Hill Education Italy S.r.l.

11

Caso di studio 1: Progetto di un sistema su un chip

Memoria

sul chip

Processore

Temporizzatore

dei minuti

Temporizzatore

del segnale

acustico

Chip

FPGA

Rete di interconnessione

PIO1

PIO2

PIO3

PIO4

PIO5

Interruttori

scorrevoli

Interruttori

a pulsante

Schermi

a 7 segmenti

LED

Altoparlante

Figura C1.4: Diagramma a blocchi della sveglia.

Il sistema è realizzato nel dispositivo FPGA usando il software Quartus

II. Si usa il Generatore SOPC per realizzare i blocchi nella zona ombreggiata

della Figura C1.4. I blocchi PIO sono configurati come segue:

• PIO1 è una porta di ingresso a tre bit; i suoi ingressi sono sensibili al livello;

• PIO2 è una porta di ingresso a due bit; i suoi ingressi sono sensibili al fronte

di discesa, in modo che un bit nel registro Cattura-fronte sia impostato a 1

quando il pulsante corrispondente viene premuto;

• PIO3 è un porta di uscita a 32 bit; ogni byte sarà collegato a uno schermo a

7 segmenti, sı̀ che ciascuno dei bit da 0 a 6 di un byte azioni un segmento,

mentre non si usa il bit 7; il byte di ordine inferiore sarà collegato alla cifra

più bassa dei minuti, quello di ordine superiore alla cifra più alta delle ore;

• PIO4 è una porta di uscita a tre bit;

• PIO5 è una porta di uscita a un bit.

Usando il Generatore SOPC, questo sistema viene specificato come mostrato in Figura C1.5. Si noti che le PIO hanno nomi che indicano le loro

funzioni. Il Generatore SOPC assegna gli indirizzi ai vari componenti nel

sistema. La memoria su chip occupa l’intervallo da 0 a 0x3FFF, mentre le

interfacce di cronometri e PIO hanno indirizzi a partire da 0x5000. Il progettista, se lo desidera, può specificare indirizzi diversi. Si noti inoltre che

Hamacher, Vranesic, Zaky, Manjikian, Introduzione all’architettura dei calcolatori 3e

© 2013 McGraw-Hill Education Italy S.r.l.

Caso di studio 1: Progetto di un sistema su un chip

12

Figura C1.5: Sistema su chip FPGA progettato con SOPC Builder.

i cronometri e gli interruttori a pulsante possono sollevare richieste di interruzioni (IRQ). L’ultima colonna nella figura indica le posizioni dei bit dei

registri di controllo Nios II ctl3 e ctl4 che sono associati con le interruzioni

provenienti da queste sorgenti. Il Generatore SOPC crea il sistema specificato producendo un modulo che descrive il sistema in uno dei linguaggi di

descrizione dell’hardware Verilog o VHDL.

C1.3.3

Realizzazione del circuito

Il sistema software Quartus II include un compilatore che accetta una specifica di un sistema digitale in un linguaggio di descrizione dell’hardware. Il

compilatore sintetizza un circuito che realizza il sistema, e determina come

questo circuito deve essere realizzato sul chip FPGA.

Poiché i dispositivi esterni devono essere collegati ai piedini della FPGA,

il progettista deve specificare le connessioni desiderate. Questa operazione è

detta assegnazione dei piedini. Il compilatore genera la realizzazione finale

sotto forma di un file di configurazione usato per scaricare le informazioni di

configurazione nel dispositivo FPGA.

La Figura C1.4 non mostra tutti i componenti necessari per realizzare l’orologio sveglia completo. Mancano l’alimentazione, il generatore di segnale

di clock e il dispositivo di configurazione necessario a programmare la FPGA.

Hamacher, Vranesic, Zaky, Manjikian, Introduzione all’architettura dei calcolatori 3e

© 2013 McGraw-Hill Education Italy S.r.l.

Caso di studio 1: Progetto di un sistema su un chip

13

Si assume che sia fornito un segnale di clock esterno a 100 MHz. I piedini della FPGA in genere non si possono collegare direttamente a dispositivi esterni

quali interruttori, schermi a sette segmenti e LED. Ciascun dispositivo ha le

proprie caratteristiche elettriche, il che significa che solitamente si devono

usare componenti quali resistori, come in Figura 10.13.

Nel nostro progetto, i pulsanti per l’impostazione di ore e minuti sono connessi ai corrispondenti bit b1 e b0 della PIO, rispettivamente. Gli interruttori

scorrevoli imposta orario attuale, imposta orario allarme, e allarme on/off

sono rispettivamente collegati ai corrispondenti bit b2 , b1 , e b0 . Il cronometro

dei minuti ha un periodo di timeout di 60 secondi. Il cronometro del segnale

acustico ha un periodo di timeout di 1 ms.

C1.3.4

Software applicativo

Occorre realizzare un programma da eseguire sull’hardware progettato per

realizzare le funzioni dell’orologio sveglia. Realizzeremo due programmi,

uno in linguaggio C e un altro nel linguaggio assemblativo Nios II, per illustrare come si possono scrivere questi programmi. Il programma sviluppato deve essere compilato in codice macchina Nios II. All’avvio, tale codice

sarebbe caricato nella memoria sul chip dal dispositivo di configurazione.

Qui si adotta il seguente approccio per realizzare i programmi. L’orario

attuale e l’orario di sveglia sono mantenuti sotto forma di interi binari a 32 bit

che rappresentano il tempo in minuti. L’orario attuale è incrementato di uno

ogni volta che il cronometro dei minuti raggiunge lo zero, il che è indicato dal

valore 1 del bit TO nel suo registro di stato. Quando l’orario attuale viene incrementato, occorre verificare se ha raggiunto 1440, che è il numero di minuti

in un giorno. In tal caso, si deve azzerare l’orario in modo da corrispondere

alla transizione da 23:59 a 00:00. Un controllo analogo è necessario quando

si imposta l’orario premendo i pulsanti.

Per visualizzare l’ora, le quattro cifre decimali che rappresentano ore e

minuti sono calcolate dividendo il tempo per 600 per ottenere la cifra di ordine

alto delle ore, quindi dividendo il resto per 60 per ottenere la cifra di ordine

basso delle ore, e cosı̀ via. Si usa una tabella per ottenere le corrispondenti

sequenze binarie che sono inviate agli schermi a 7 segmenti.

Si usa il cronometro del segnale acustico per creare un segnale a onda quadra di 500 Hz, che produce un ronzio quando è collegato a un altoparlante.

Questo cronometro è eseguito in modalità continua. Dal momento che ha un

periodo predefinito di timeout di 1 ms, si potrebbe generare direttamente il segnale a 500 Hz invertendo il valore logico del segnale alla fine di ogni periodo

Hamacher, Vranesic, Zaky, Manjikian, Introduzione all’architettura dei calcolatori 3e

© 2013 McGraw-Hill Education Italy S.r.l.

Caso di studio 1: Progetto di un sistema su un chip

14

del cronometro. Tuttavia, per illustrare come si può definire un periodo diverso in un programma, si userà il registro del valore iniziale del contatore per

specificare il periodo desiderato. In questo caso, occorre il valore 0x30D40

per il segnale a 500 Hz se il contatore è pilotato da un clock a 100 MHz.

Quando si usa la scansione per il segnale di timeout di un cronometro, è

necessario controllare il bit TO nel suo registro di stato. Poiché il bit RUN

è sempre uguale a 1 quando il contatore gira, si può effettuare la scansione

controllando se il contenuto del registro di stato è uguale a 3. Il bit TO si può

portare a 0 semplicemente scrivendo uno zero nel registro di stato, perché lo

stato del bit RUN non è influenzato da un’operazione di scrittura.

Programma C

La Figura C1.6 mostra un possibile programma in linguaggio C. La presente

applicazione non è impegnativa in termini di prestazioni, quindi si usa il metodo della scansione per accedere a tutte le PIO e ai cronometri. I commenti

nel programma spiegano il significato delle varie istruzioni. Si osservi che la

macro AGGIUSTA definisce un’espressione che incrementa l’orario in modo

opportuno in diverse situazioni.

Programma in linguaggio assemblativo

La Figura C1.7 presenta un programma Nios II. Per illustrare l’uso delle interruzioni, il programma usa le interruzioni per gestire il cronometro dei minuti.

Si usa la scansione per il cronometro del segnale acustico.

In fase di progettazione, il Generatore SOPC ha assegnato 0x20 quale

indirizzo dove inizia il gestore delle interruzioni quando il processore accetta

una richiesta di interruzione. Il gestore di interruzioni verifica che vi sia un’interruzione causata da un dispositivo esterno al processore Nios II e aggiusta

di conseguenza l’indirizzo di rientro (si veda l’Approfondimento applicativo

3.2 per una spiegazione dettagliata del meccanismo delle interruzioni del Nios

II); quindi azzera il bit TO nel cronometro dei minuti e chiama la routine di

servizio delle interruzioni. Si noti che il gestore delle interruzioni salva, e poi

ripristina, il contenuto dei registri r2 e ra. Salva il contenuto di ra, che è il registro di collegamento che contiene l’indirizzo di rientro da sottoprogramma,

poiché un’interruzione da cronometro può aversi durante l’esecuzione di un

sottoprogramma; anche il gestore delle interruzioni usa il registro ra per una

chiamata alla routine di servizio delle interruzioni, AGGIORNA ORA, che

incrementa l’orario attuale (e a mezzanotte lo azzera).

Il programma principale inizia impostando la pila del processore e azzerando le locazioni di memoria che contengono l’orario. Come parte del

Hamacher, Vranesic, Zaky, Manjikian, Introduzione all’architettura dei calcolatori 3e

© 2013 McGraw-Hill Education Italy S.r.l.

Caso di studio 1: Progetto di un sistema su un chip

15

processo di inizializzazione, imposta il periodo di timeout per il cronometro del segnale acustico; quindi fa partire entrambi i cronometri e abilita le

interruzioni dal cronometro dei minuti.

Il ciclo principale, CICLO, controlla lo stato degli interruttori scorrevoli e

prende i provvedimenti necessari. Il sottoprogramma DISP visualizza l’orario attuale o l’orario di sveglia, mantenuti alle locazioni di memoria 0x1000

o 0x1010, sugli schermi a sette segmenti. Si usa il sottoprogramma SETSUB per impostare i valori di minuti e ore quando si pigiano i corrispondenti

pulsanti. Ogni volta che si pigia un pulsante si incrementa il valore di uno.

Si usa la tabella alla fine del programma per convertire una cifra decimale

nella corrispondente sequenza di sette bit per visualizzarla.

I commenti nel programma spiegano il significato delle varie istruzioni. I registri di controllo e ctl3 ctl4 si possono anche indicare mediante

i nomi ienable e ipending, rispettivamente. Questi sono i nomi usati nel

programma.

# define

# define

# define

# define

# define

# define

# define

# define

int ora

t e m p m i n u t i ( v o l a t i l e i n t * ) 0 x5000

t e m p t o n o ( v o l a t i l e i n t * ) 0 x5020

c u r s o r i ( v o l a t i l e i n t * ) 0 x5040

p u l s a n t i ( v o l a t i l e i n t * ) 0 x5050

d i s p l a y ( i n t * ) 0 x5060

LED ( i n t * ) 0 x5070

a l t o p a r l a n t e ( i n t * ) 0 x5080

AGGIUSTA( t , x ) ( ( t +x ) >=1440)?( t +x − 1 4 4 0 ) : ( t +x )

attuale , ora sveglia , sveglia attiva , orario ;

/ * T a b e l l a d i c o n v e r s i o n e da e s a d e c i m a l e a 7 s e g m e n t i * /

u n s i g n e d c h a r t a b e l l a [ 1 6 ] = {0 x40 , 0 x79 , 0 x24 , 0 x30 , 0 x19 , 0 x12 , 0 x02 , 0 x78 ,

0 x00 , 0 x18 , 0x3F , 0x3F , 0x3F , 0x3F , 0x3F , 0 x3F } ;

void impostaTemporizzatoreTono ( )

{

* ( t e m p t o n o + 2 ) = 0x0D40 ; / * I m p o s t a i l p e r i o d o d i t i m e o u t * /

/* per funzionamento continuo . */

* ( t e m p t o n o + 3 ) = 0 x03 ;

/ * Avvia i n m o d a l i t a ' c o n t i n u a . * /

* ( t e m p t o n o + 1 ) = 0 x6 ;

}

v o i d DISP ( o r a r i o )

/* O t t i e n i la sequenza dei 7 segmenti . */

{

* d i s p l a y = t a b e l l a [ o r a r i o / 6 0 0 ] << 24 |

t a b e l l a [ ( o r a r i o % 6 0 0 ) / 6 0 ] << 16 |

t a b e l l a [ ( o r a r i o % 6 0 ) / 1 0 ] << 8 |

tabella [( orario % 10)];

}

. . . continua nella Parte b

Figura C1.6: Programma C per la sveglia (Parte a).

Hamacher, Vranesic, Zaky, Manjikian, Introduzione all’architettura dei calcolatori 3e

© 2013 McGraw-Hill Education Italy S.r.l.

16

Caso di studio 1: Progetto di un sistema su un chip

main ( )

{

o r a a t t u a l e = ora sveglia = s v e g l i a a t t i v a = 0;

impostaTemporizzatoreTono ( ) ;

/* Esegui in modalita ' continua . */

* ( t e m p m i n u t i + 1 ) = 0 x6 ;

while (1)

{

/ * Un m i n u t o e ' t r a s c o r s o . * /

i f ( * t e m p m i n u t i == 3 )

{

/ * A z z e r a i l b i t TO . * /

* temp minuti = 0;

o r a a t t u a l e = AGGIUSTA( o r a a t t u a l e , 1 ) ;

}

i f ( ( * c u r s o r i & 1) != 0) / * C o n t r o l l a se l ' i n t e r r u t t o r e * /

{

/*

sveglia e ' a t t i v o . */

/ * A c c e n d i i l LED s v e g l i a . * /

*LED = 7 ;

i f ( o r a a t t u a l e == o r a s v e g l i a )

s v e g l i a a t t i v a = 1 ; / * Avvia i l s u o n o d e l l a s v e g l i a . * /

else

s v e g l i a a t t i v a = s v e g l i a a t t i v a & (* c u r s o r i & 1 ) ;

i f ( * t e m p t o n o == 3 ) / * G e n e r a l ' onda q u a d r a . * /

{

* a l t o p a r l a n t e = (* a l t o p a r l a n t e ˆ 1) & s v e g l i a a t t i v a ;

/ * A z z e r a i l b i t TO . * /

* temp tono = 0;

}

}

else

{

/ * S p e g n i i l LED s v e g l i a . * /

*LED = 6 ;

s v e g l i a a t t i v a = 0;

}

i f ( ( * c u r s o r i & 4) != 0) / * C o n t r o l l a l ' i n t e r r u t t o r e imposta

{

DISP ( o r a a t t u a l e ) ;

/* Mostra l ' o r a r i o d e l gio rno . */

i f ( ( * ( p u l s a n t i + 3) & 1) != 0) / * Imposta i m i n u t i ? * /

o r a a t t u a l e = AGGIUSTA( o r a a t t u a l e , 1 ) ;

e l s e i f ( ( * ( p u l s a n t i + 3) & 2) != 0) / * Imposta l e ore ? * /

o r a a t t u a l e = AGGIUSTA( o r a a t t u a l e , 6 0 ) ;

* ( p u l s a n t i + 3 ) = 0 ; / * A z z e r a i l r e g i s t r o C a t t u r a −f r o n t e

}

else

i f ( ( * c u r s o r i & 2) != 0) / * C o n t r o l l a l ' i n t e r r u t t o r e imposta

{

DISP ( o r a s v e g l i a ) ;

/* Mostra l ' o r a r i o di s v e g l i a . */

i f ( ( * ( p u l s a n t i + 3) & 1) != 0) / * Imposta i m i n u t i ? * /

o r a s v e g l i a = AGGIUSTA( o r a s v e g l i a , 1 ) ;

e l s e i f ( ( * ( p u l s a n t i + 3) & 2) != 0) / * Imposta l e ore ? * /

o r a s v e g l i a = AGGIUSTA( o r a s v e g l i a , 6 0 ) ;

* ( p u l s a n t i + 3 ) = 0 ; / * A z z e r a i l r e g i s t r o C a t t u r a −f r o n t e

}

else

DISP ( o r a a t t u a l e ) ;

/* Mostra l ' o r a r i o d e l gio rno . */

}

}

orario . */

. */

sveglia . */

. */

Figura C1.6: Programma C per la sveglia (Parte b).

Hamacher, Vranesic, Zaky, Manjikian, Introduzione all’architettura dei calcolatori 3e

© 2013 McGraw-Hill Education Italy S.r.l.

17

Caso di studio 1: Progetto di un sistema su un chip

.equ

.equ

.equ

.equ

.equ

.equ

.equ

.equ

.equ

.equ

br

start:

temp minuti, 0x05000

temp tono, 0x5020

cursori, 0x5040

pulsanti, 0x5050

display, 0x5060

LED, 0x5070

altoparlante, 0x5080

ORA ATTUALE, 0x1000

ORA SVEGLIA, 0x1010

PILA, 0x2000

MAIN

Gestore interruzione

.org

0x20

subi

sp, sp, 8

stw

r2, 0(sp)

stw

ra, 4(sp)

rdctl

et, ipending

beq

et, r0, MAIN

/*

/*

MAIN:

subi

ea, ea, 4

movia

sthio

call

r2, temp minuti

r0, (r2)

AGGIORNA ORA

ldw

ldw

addi

eret

r2, 0(sp)

ra, 4(sp)

sp, sp, 8

Programma principale

movia sp, PILA

movia r2, ORA SVEGLIA

stw

r0, (r2)

movia r2, ORA ATTUALE

stw

r0, (r2)

movia r2, cursori

movia r3, LED

movia r4, display

movia r5, pulsanti

*/

/* Salva registri.

*/

/* Errore se non è un’interruzione

/* esterna, trattarlo come riavvio.

/* Decrementa ea per eseguire

/* l’istruzione interrotta quando

/* ritorna al programma principale.

/* Azzera il bit TO nel

/* temporizzatore dei minuti.

/* Chiama routine di servizio

/* dell’interruzione.

/* Ripristina i registri.

*/

*/

*/

*/

*/

*/

*/

*/

*/

*/

/* Inizializza puntatore alla pila.

/* Azzera buffer dell’orario sveglia.

*/

*/

*/

/* Azzera buffer dell’orario attuale.

*/

/* Indirizzo interruttori a cursore.

/* Indirizzo dei LED.

/* Indirizzo schermi a 7 segmenti.

/* Indirizzo dei pulsanti.

*/

*/

*/

*/

. . . continua nella Parte b

Figura C1.7: Programma Nios II per la sveglia (Parte a).

Hamacher, Vranesic, Zaky, Manjikian, Introduzione all’architettura dei calcolatori 3e

© 2013 McGraw-Hill Education Italy S.r.l.

Caso di studio 1: Progetto di un sistema su un chip

movi

stbio

movia

ori

sthio

ori

sthio

movi

sthio

movia

addi

sthio

movi

wrctl

wrctl

movia

call

ldbio

andi

beq

movi

stbio

movia

ldw

ldw

bne

movia

movi

CICLO SVEGLIA:

call

ldbio

andi

beq

ldhio

sthio

andi

xor

movia

stbio

br

CICLO:

r6, 6

r6, (r3)

r6, temp tono

r7, r0, 0x0D40

r7, 8(r6)

r7, r0, 0x03

r7, 12(r6)

r7, 6

r7, 4(r6)

r6, temp minuti

r7, r0, 7

r7, 4(r6)

r7, 1

ienable, r7

status, r7

r10, ORA ATTUALE

DISP

r7, (r2)

r11, r7, 1

r11, r0, PROSSIMO

r11, 7

r11, (r3)

r9, ORA SVEGLIA

r11, (r9)

r12, (r10)

r11, r12, PROSSIMO

r8, temp tono

r12, 1

DISP

r7, (r2)

r13, r7, 1

r13, r0, PROSSIMO

r9, (r8)

r0, (r8)

r9, r9, 1

r12, r9, r12

r11, altoparlante

r12, (r11)

CICLO SVEGLIA

18

/* Accendi i due LED

/* verticali.

*/

*/

/* Inizializza il periodo

/* del temporizzatore del tono.

*/

*/

/* Avvia temporizzatore del tono.

*/

/* Indirizzo temporizzatore minuti.

/* Avvia il temporizzatore.

*/

*/

/* Abilita interruzioni

/* dal temporizzatore.

/* Abilita interruzioni esterne.

/* Visualizza orario del giorno.

*/

*/

*/

*/

/* Interruttore sveglia attivo?

*/

/* Se sı̀, allora accendi il

/* LED sveglia.

*/

*/

/* Confronta l’orario di sveglia

/* con l’orario attuale.

/* La sveglia dovrebbe suonare?

*/

*/

*/

/* Interruttore sveglia attivo?

*/

/* Leggi stato temporizzatore tono.

/* Azzera il bit TO.

/* Controlla se il contatore è a 0.

/* Genera successivo semiciclo

/* dell’onda quadra; invia

/* il segnale all’altoparlante.

*/

*/

*/

*/

*/

*/

. . . continua nella Parte c

Figura C1.7: Programma Nios II per la sveglia (Parte b).

Hamacher, Vranesic, Zaky, Manjikian, Introduzione all’architettura dei calcolatori 3e

© 2013 McGraw-Hill Education Italy S.r.l.

Caso di studio 1: Progetto di un sistema su un chip

PROSSIMO:

movi

stbio

TEST CURSORI:

ldbio

andi

beq

movia

br

ATTIVA:

andi

beq

movia

ORARIO:

call

call

br

/*

DISP:

19

r11, 6

r11, (r3)

/* Spegni LED che indica che la

/* sveglia è attiva.

*/

*/

r7, (r2)

r11, r7, 2

r11, r0, ATTIVA

r10, ORA SVEGLIA

ORARIO

/* Interruttore imposta sveglia attivo?

/* Se no, controlla orario corrente.

/* Va impostata l’ora di sveglia.

*/

*/

*/

/* Interruttore imposta orario attivo?

/* Tutti i cursori sono disattivati.

*/

*/

r11, r7, 4

r11, r0, CICLO

r10, ORA ATTUALE

DISP

SETSUB

TEST CURSORI

Visualizza l’orario sugli schermi a 7 segmenti.

subi

sp, sp, 24

/* Salva registri.

stw

r11, 0(sp)

stw

r12, 4(sp)

stw

r13, 8(sp)

stw

r14, 12(sp)

stw

r15, 16(sp)

stw

r16, 20(sp)

ldw

r11, (r10)

/* Carica l’orario da mostrare.

movi

r12, 600

/* Per determinare la prima cifra

divu

r13, r11, r12

/* delle ore, dividi per 600.

ldb

r15, TABELLA(r13)

/* Ottieni serie dei 7 segmenti.

slli

r15, r15, 8

/* Fai spazio alla prossima cifra.

mul

r14, r13, r12

/* Calcola il resto della

sub

r11, r11, r14

/* divisione.

movi

r12, 60

/* Dividi il resto per 60 per avere

divu

r13, r11, r12

/* la seconda cifra delle ore.

ldb

r16, TABELLA(r13)

/* Ottieni serie dei 7 segmenti,

or

r15, r15, r16

/* concatenala alla prima cifra

slli

r15, r15, 8

/* e falla scorrere.

mul

r14, r13, r12

/* Determina i minuti che

sub

r11, r11, r14

/* devono essere mostrati.

. . . continua nella Parte d

Figura C1.7: Programma Nios II per la sveglia (Parte c).

Hamacher, Vranesic, Zaky, Manjikian, Introduzione all’architettura dei calcolatori 3e

© 2013 McGraw-Hill Education Italy S.r.l.

*/

*/

*/

*/

*/

*/

*/

*/

*/

*/

*/

*/

*/

*/

*/

*/

20

Caso di studio 1: Progetto di un sistema su un chip

movi

divu

ldb

or

slli

mul

sub

ldb

or

movia

stw

ldw

ldw

ldw

ldw

ldw

ldw

addi

ret

r12, 10

r13, r11, r12

r16, TABELLA(r13)

r15, r15, r16

r15, r15, 8

r14, r13, r12

r11, r11, r14

r16, TABELLA(r11)

r15, r15, r16

r11, display

r15, (r11)

r11, 0(sp)

r12, 4(sp)

r13, 8(sp)

r14, 12(sp)

r15, 16(sp)

r16, 20(sp)

sp, sp, 24

/* Imposta l’orario desiderato.

SETSUB:

subi

sp, sp, 16

stw

r11, 0(sp)

stw

r12, 4(sp)

stw

r13, 8(sp)

stw

r14, 12(sp)

ldbio

r12, 12(r5)

stbio

r0, 12(r5)

andi

r13, r12, 1

beq

r13, r0, ORE

ldw

r11, (r10)

movi

r12, 60

divu

r13, r11, r12

mul

r14, r13, r12

sub

r11, r11, r14

addi

r11, r11, 1

blt

r11, r12, SALVAM

mov

r11, r0

/* Per determinare la prima cifra dei

/* minuti, dividi per 10.

/* Ottieni la serie dei 7 segmenti,

/* concatenala alle prime due cifre

/* e falla scorrere.

/* Calcola il resto, che

/* è l’ultima cifra.

/* Concatena l’ultima cifra alle

/* 3 cifre precedenti.

*/

*/

*/

*/

*/

*/

*/

*/

*/

/* Visualizza la serie ottenuta.

/* Ripristina registri.

*/

*/

*/

/* Salva registri.

*/

/* Controlla i pulsanti.

/* Azzera registro Cattura-fronte.

/* Il pulsante dei minuti è pigiato?

/* Se no, controlla le ore.

/* Carica l’orario corrente.

/* Dividi per 60 per determinare

/* il numero di ore.

/* Il resto della divisione

/* è il numero di minuti.

/* Incrementa i minuti.

/* Salva se minore di 60,

/* altrimenti poni i minuti a 00.

*/

*/

*/

*/

*/

*/

*/

*/

*/

*/

*/

*/

. . . continua nella Parte e

Figura C1.7: Programma Nios II per la sveglia (Parte d).

Hamacher, Vranesic, Zaky, Manjikian, Introduzione all’architettura dei calcolatori 3e

© 2013 McGraw-Hill Education Italy S.r.l.

Caso di studio 1: Progetto di un sistema su un chip

SALVAM:

ORE:

SALVAO:

FATTO:

add

stw

br

andi

beq

ldw

addi

movi

blt

sub

stw

r11, r14, r11

r11, (r10)

FATTO

r13, r12, 2

r13, r0, FATTO

r11, (r10)

r12, r11, 60

r13, 1440

r12, r13, SALVAO

r12, r12, r13

r12, (r10)

ldw

ldw

ldw

ldw

addi

ret

r11, 0(sp)

r12, 4(sp)

r13, 8(sp)

r14, 12(sp)

sp, sp, 16

/* (ore x 60) + (minuti aggiornati).

/* Salva il nuovo orario.

*/

*/

/* Il pulsante delle ore è pigiato?

/* Se no, allora rientra.

/* Carica l’orario corrente in minuti.

/* Aggiungi 60 minuti.

/* Controlla se l’orario aggiornato

/* è minore di 24:00.

/* Reimposta l’orario a 00:00.

/* Salva il nuovo orario.

*/

*/

*/

*/

*/

*/

*/

*/

/* Ripristina registri.

*/

/*

Routine di servizio interruzioni che aggiorna orario corrente

AGGIORNA ORA:

subi

sp, sp, 12

/* Salva registri.

stw

r2, 0(sp)

stw

r3, 4(sp)

stw

r4, 8(sp)

movia r2, ORA ATTUALE

ldw

r3, (r2)

/* Carica l’orario attuale del giorno.

addi

r3, r3, 1

/* Incrementa di uno i minuti.

movi

r4, 1440

/* Fatto se l’orario aggiornato è

blt

r3, r4, SALVAT

/* minore di 24:00.

mov

r3, r0

/* Altrimenti, ponilo a 00:00.

SALVAT:

stw

r3, (r2)

/* Salva l’orario aggiornato.

ldw

r2, 0(sp)

/* Ripristina registri.

ldw

r3, 4(sp)

ldw

r4, 8(sp)

addi

sp, sp, 12

ret

/*

TABELLA:

21

Tabella di conversione da cifre esadecimali a 7 segmenti

.org

0x1050

.byte

0x40, 0x79, 0x24, 0x30, 0x19, 0x12, 0x02, 0x78

.byte

0x00, 0x18, 0x3F, 0x3F, 0x3F, 0x3F, 0x3F, 0x3F

.end

Figura C1.7: Programma Nios II per la sveglia (Parte e).

Hamacher, Vranesic, Zaky, Manjikian, Introduzione all’architettura dei calcolatori 3e

© 2013 McGraw-Hill Education Italy S.r.l.

*/

*/

*/

*/

*/

*/

*/

*/

*/

*/

Caso di studio 1: Progetto di un sistema su un chip

C1.4

22

Osservazioni conclusive

Il progettista di un sistema embedded cerca inevitabilmente l’approccio più

semplice e più conveniente. Un chip microcontrollore che possiede le risorse

per realizzare un intero sistema può essere la scelta migliore. La situazione

è diversa se sono necessari chip aggiuntivi per realizzare il sistema. In tal

caso le soluzioni FPGA sono molto interessanti poiché hanno probabilmente

bisogno di un minor numero di chip per realizzare il sistema.

Un’altra considerazione è la disponibilità di moduli predefiniti. Un chip

microcontrollore contiene un certo numero di moduli differenti. Qualsiasi

caratteristica che non si possa realizzare usando questi moduli deve essere

realizzata utilizzando chip aggiuntivi. Un dispositivo FPGA consente al progettista di progettare qualsiasi tipo di circuito digitale. Si possono realizzare

circuiti molto grandi e complessi nei dispositivi FPGA moderni.

Progetti pratici spesso coinvolgono circuiti che eseguono operazioni di

uso comune. Tali circuiti sono di solito disponibili come moduli di libreria,

come illustrato dalle interfacce di I/O e dai circuiti dei cronometri utilizzati nel

paragrafo precedente. Per le applicazioni di elaborazione di segnali, la libreria

comprende tipici circuiti di filtraggio. Se un sistema si deve collegare a un

altro calcolatore utilizzando uno schema standard di interconnessione, come

per esempio PCI Express, il compito del progettista è molto più semplice se è

disponibile un’interfaccia PCI Express come modulo predefinito.

C1.5

Problemi

C1.1 [F] Nel Paragrafo C1.3.4, si è detto che il segnale a 500 Hz a onda

quadra si può generare semplicemente invertendo il valore logico del segnale

al termine di ciascun periodo di timeout del cronometro del segnale acustico, progettato per aver luogo ogni millisecondo. Modificare il programma in

Figura C1.6 per sfruttare questo fatto.

C1.2 [F] Ripetere il Problema C1.1 per il programma in Figura C1.7.

C1.3 [M] Si consideri il formato di visualizzazione per la sveglia nel Paragrafo C1.3. Invece di visualizzare l’orario da 00:00 a 23:59, si desidera visualizzarlo come da 12:00 a 11:59 AM o PM. Si supponga che un quarto LED

sia disponibile e collegato al bit b3 di una PIO larga quattro bit invece della

PIO larga tre bit usata nel Paragrafo C1.3. Questo LED indica PM quando è

Hamacher, Vranesic, Zaky, Manjikian, Introduzione all’architettura dei calcolatori 3e

© 2013 McGraw-Hill Education Italy S.r.l.

Caso di studio 1: Progetto di un sistema su un chip

23

acceso. Modificare il programma in Figura C1.6 per visualizzare l’orario in

questo modo.

C1.4 [M] Ripetere il Problema C1.3 per il programma in Figura C1.7.

C1.5 [F] Si supponga che un solo cronometro, con un periodo predefinito di timeout di 1 ms, sia usato nella sveglia del Paragrafo C1.3. Apportare le appropriate modifiche al programma in Figura C1.6 per fornire il comportamento

richiesto.

C1.6 [F] Ripetere il Problema C1.5 per il programma in Figura C1.7.

C1.7 [F] In Figura C1.7 si sono usate le interruzioni per gestire il cronometro

dei minuti e la scansione per il cronometro del segnale acustico. Modificare

il programma per usare le interruzioni per entrambi i cronometri.

C1.8 [M] Nella sveglia del Paragrafo C1.3, si imposta l’orario incrementando

il valore corrente ogni volta che si preme un pulsante. Questo potrebbe essere

noioso se si deve premere molte volte un pulsante. Un’alternativa migliore

sarebbe quella di incrementare l’ora automaticamente ogni 0,5 secondi mentre un pulsante viene tenuto premuto. Quali cambiamenti si dovrebbero fare

all’hardware per fornire questa funzionalità, se è il caso di farne? Modificare

il programma in Figura C1.6 per realizzare la funzionalità.

C1.9 [M] Ripetere il Problema C1.8 per il programma in Figura C1.7.

C1.10 [M] Si desidera rendere intermittenti a intervalli di un secondo i due

LED disposti verticalmente nella sveglia quando si fornisce l’alimentazione.

Essi dovrebbero cessare di lampeggiare non appena l’utente inizia a impostare l’orario. Modificare il programma in Figura C1.6 per realizzare questo

comportamento.

C1.11 [M] Ripetere il Problema C1.10 per il programma in Figura C1.7.

Hamacher, Vranesic, Zaky, Manjikian, Introduzione all’architettura dei calcolatori 3e

© 2013 McGraw-Hill Education Italy S.r.l.