Informatica Applicata – Progettazione dei sistemi di elaborazione

3DUWH

3URFHVVRUH

Facoltà di Scienze MM FF NN – Università di Urbino – A.A. 2001/2002

© Alessandro Bogliolo

1

Informatica Applicata – Progettazione dei sistemi di elaborazione

© Alessandro Bogliolo

,OSURFHVVRUHFRPHFRPSRQHQWHGLXQVLVWHPD

'HILQL]LRQHGHOSUREOHPD

•

•

•

L’utilizzo di un microprocessore come componente di un sistema richiede la definizione di un modello

funzionale e parametrico e la specifica logica ed elettrica dell’interfaccia. Il modello è detto black-box se

nasconde i dettagli implementativi a livello microarchitetturale.

I modelli sono eseguibili se possono essere utilizzati per effettuare simulazioni funzionali e parametriche.

Il livello di accuratezza/astrazione di un modello di microprocessore può essere:

• ,QVWUXFWLRQOHYHO I risultati della simulazione del modello coincidono con i risultati prodotti dal

microprocessore reale istruzione per istruzione, ma vengono trascurati i dettagli dell’esecuzione di

ciascuna istruzione. All’esecuzione di ogni istruzione possono essere associati parametri temporali

(quali il numero di cicli di clock dedicati all’esecuzione, CPI), ma generalmente a questo livello di

astrazione non è possibile prevedere i cicli di stallo provocati da conflitti di dati e risorse legati alla

microarchitattura. Pertanto il tempo di esecuzione valutato dalla simulazione puo’ non coincidere con

quello effettivo. In linea di principio è possibile aumentare l’accuratezza dei modelli di timing, come

vedremo nel seguito, riducendo l’inaccuratezza delle simulazione.

• &\FOHDFFXUDWHI risultati della simulazione del modello coincidono con i risultati prodotti dal

microprocessore reale ciclo di clock per ciclo di clock. Questo richiede maggiore conoscenza

dell’architettura interna e minore astrazione. Le stime sui tempi di esecuzione sono più accurate

perchè tengono conto degli stalli della pipeline, ma il modello è più complesso e la simulazione più

lenta.

6SHFLILFDIXQ]LRQDOH

•

•

•

Instruction set

Interfaccia

Protocolli di comunicazione

•

CPI (clock per instruction): numero di cicli di clock dedicati all’esecuzione di un’istruzione

indipendentemente dai dati e dal contesto. Il CPI è una proprietà di ogni istruzione (o tipo di istruzione)

dell’instruction set

Latenza: numero di cicli di clock che intercorrono tra l’inizio dell’esecuzione di un’istruzione e la

disponibilità dei risultati per le istruzioni successive. La latenza è una proprietà di ogni istruzione, se

riferita al momento del write-back dei risultati nel register file, poichè il write back non dipende dall’uso

che dei dati verrà fatto in seguito. La latenza puo’ essere anche definita con riferimento a coppie di

istruzioni contigue di cui la seconda usa i risultati della prima. In tal caso la latenza puo’ essere definita

come numero di cicli di clock che intercorrono tra l’esecuzione della prima e l’esecuzione della seconda.

In questo caso la latenza dipende anche dall’istruzione che segue, poichè il forwarding dei risultati puo’

avere effetti diversi. A volte la latenza è definita come numero di ciclo di stallo introdotti tra le due

istruzioni per effetto del conflitto di dati. Questa definizione porta ad un valore di latenza diminuito di 1

rispetto alla precedente definizione. Se non diversamente specificato nel seguito intenderemo per

latenza la distanza tra le istruzioni: in assenza di cicli di stallo la latenza è 0.

In generale la latenza tiene conto dei conflitti di dati.

Repetition time: minimo numero di cicli di clock che intercorrono tra due esecuzioni successive della

stessa istruzione, in assenza di conflitti di dati. Il repetition time tiene conto dei conflitti di risorse. E’ una

proprietà delle singole istruzioni (da cui il nome repetition time), ma piu’ in generale è una proprietà di

coppie di istruzioni che condividono risorse di esecuzione.

Costruzione del modello

Il modello puo’ essere costituito da una matrice quadrata le cui righe e colonne sono associate alle

istruzione dell’instruction set. Ad ogni elemento della matrice (in posizione i,j) sono associati latenza e

repetition time relativi all’esecuzione in sequenza dell’istruzione i e dell’istruzione j. Agli elementi sulla

diagonale sono associati anche i CPI.

Caratterizzazione

La caratterizzazione del modello puo’ essere effettuata analizzando o simulando la microarchitattura.

Valutazione

La valutazione del modello non richiede la conoscenza della microarchitettura.

Osservando il codice assembler è possibile stimare accuratamente il numero di cicli di stallo introdotti

per conflitti di dati e risorse, stimando il tempo di esecuzione. Il numero di cicli di stallo da introdurre è il

minimo che garantisca il rispetto del CPI di ogni istruzione e di Latenza e Repetition time di ogni coppia

di istruzioni.

Legame tra parametri del modello e microarchitettura

6SHFLILFDSDUDPHWULFDSUHVWD]LRQL

•

•

•

•

•

•

Facoltà di Scienze MM FF NN – Università di Urbino – A.A. 2001/2002

2

Informatica Applicata – Progettazione dei sistemi di elaborazione

•

•

•

•

•

© Alessandro Bogliolo

Esempio: somma tra interi nel DLX

CPI = 1

Latenza = 1 (nei confronti di istruzioni aritmetico-logiche)

Latenza = 2 (nei confronti dei salti condizionati)

Repetition time = 1 (nei confronti di qualsiasi istruzione)

Esempio: somma FP nel DLX, assumendo che l’unità di esecuzione FP sia unica, impieghi 5 cicli di

clock e non sia pipelined

CPI = 5

Latenza = 5 (nei confronti di istruzioni aritmentico-logiche)

Latenza = 6 (nei confronti dei salti condizionati)

Repetition time = 5 (nei confronti di somme e sottrazioni FP)

Esempio: somma FP nel DLX, assumendo che l’unità di esecuzione FP sia unica, impieghi 5 cicli di

clock e sia pipelined

CPI = 1

Latenza = 5 (nei confronti di istruzioni aritmentico-logiche)

Latenza = 6 (nei confronti dei salti condizionati)

Repetition time = 1 (nei confronti di somme e sottrazioni FP)

Esempio: somma FP nel DLX, assumendo che le unità di esecuzione FP siano 2, impieghino 5 cicli

di clock e non siano pipelined

CPI = 1

Latenza = 5 (nei confronti di istruzioni aritmentico-logiche)

Latenza = 6 (nei confronti dei salti condizionati)

Repetition time = 1 (nei confronti della prima somma o sottrazione FP successiva)

Repetition time = 5 (nei confronti della seconda somma o sottrazione FP successiva)

Esempio: load nel DLX

CPI = 1 (assumendo che l’architettura di memoria sia Harvard)

Latenza = 2 (nei confronti di istruzioni aritmentico-logiche)

Latenza = 3 (nei confronti dei salti condizionati)

Repetition time = 1

6SHFLILFDSDUDPHWULFDFRQVXPRGLSRWHQ]DHQHUJLD

•

•

•

•

•

•

Potenza media

Energia per istruzione

Energia per ciclo di clock

Costruzione del modello

Il modello puo’ essere costituito da un vettore i cui elementi sono associati alle istruzioni dell’instruction

set. L’elemento in posizione i contiene l’energia spesa per processare l’i-esima istruzione dell’instruction

set e il numero di stadi della pipeline attraversati dall’istruzione. Il rapporto tra i due è l’energia media per

ciclo di clock consumata dall’istruzione.

Caratterizzazione

La caratterizzazione del modello puo’ essere effettuata a diversi livelli di accuratezza. Assumendo di

conoscere la microarchitattura e di aver associato un consumo medio per ciclo di clock ad ogni

componente, la stima dell’energia per istruzione si ottiene come somma dell’energia consumata da ogni

componente per eseguire quell’istruzione, a sua volta ottenuta moltiplicando l’energia media di quel

componente per il numero di cicli di clock in cui il componente è impegnato ad eseguire l’istruzione.

Valutazione

La valutazione del modello non richiede la conoscenza della microarchitettura. Il consumo totale relativo

ad un segmento di codice puo’ essere stimato come somma delle energie totali spese per ogni

istruzione. Il profilo di consumo istantaneo (per ciclo di clock) puo’ essere stimato ripartendo il consumo

totale di ogni istruzione su tanti cicli di clock quanti sono gli stadi attraversati dall’istruzione. In prima

approssimazione si puo’ trascurare il consumo associato agli stalli della pipeline.

&DUDWWHUL]]D]LRQHGHOOHSUHVWD]LRQLGLXQPLFURSURFHVVRUH

&38SHUIRUPDQFHHTXDWLRQ

&387 = [Seconds/Program] = ,&&3,&/. &38&&/.

,& = [Instructions/Program] (dipende dall’instruction set e dal compilatore)

&3, = [Clock cycles/Instruction] (dipende dall’instruction set e dalla microarchitattura)

&/. = [Seconds/Clock cycle] (dipende dalla microarchitettura e dalla tcnologia)

&38& = ,&&3,

Facoltà di Scienze MM FF NN – Università di Urbino – A.A. 2001/2002

3

Informatica Applicata – Progettazione dei sistemi di elaborazione

Il CPI medio è dato da:

∑

&3, =

=1

,& ⋅ &3,

,&

=∑

=1

© Alessandro Bogliolo

,&

&3,

,&

'HILQL]LRQHGHOSUREOHPD

Con riferimento alla CPU performance equation osserviamo che:

• CLK generalmente noto

• Difficoltà di misura di IC e di CPI

• Limitata risoluzione temporale nella determinazione di CPUT. Indichiamo con HUU l’errore di

approssimazione dovuto alla limitata risoluzione temporale.

$SSURFFLRJHQHUDOHPLFUREHQFKPDUNLQFUHPHQWDOL

•

•

•

•

Impiego di due benchmarks che differiscono solo per il segmento di codice da analizzare, detto

,QVWUXFWLRQ8QGHU7HVW, IUT, o &RGHVHJPHQW8QGHU7HVW, CUT.

Detto B0 il benchmark che non contiene il CUT e B1 quello che lo contiene, risulta:

CPUT(CUT)=CPUT(B1)-CPUT(B0)

Problemi:

• Condizioni al contorno: il CUT deve essere indipendente dai segmenti di codice che precededono e

seguono il punto di inserimento

• CPUT(CUT) puo’ essere inferiore alla risoluzione del clock di sistema (CPUT(CUT)<err)

Soluzione: inserire il CUT in un ciclo eseguito N volte. Il template del benchmark e’ il seguente:

code segment A;

for (i = 0; i < N; i++) {

code segment B;

CUT;

code segment C;

}

code segment D;

•

•

Il CUT deve essere indipendente dai segmenti B e C tra i quali è inserito

I segmenti B e C devono essere sufficientemente lunghi da rendere indipendenti le esecuzioni

successive del CUT

CPUT(CUT)=(CPUT(B1)-CPUT(B0))/N

•

La risoluzione temporale (errore) nella misura di CPUT(CUT) è HUU1, che puo’ essere reso

arbitrariamente piccolo aumentando 1

9DOXWD]LRQHGHO&3,GLXQ¶LVWUX]LRQH

•

•

Si impiegano due benchmark incrementali come descritto nel paragrafo precedente, utilizzando come

CUT solo l’istruzione di cui si vuol valutare il CPI

Avvertenze: l’istruzione che rappresenta il CUT deve essere indipendente dai segmenti di codice

precedente e seguente, sia in termini di dati che di risorse. Altrimenti la valutazione del CPI sarebbe

falsata da latenza e repetition time.

9DOXWD]LRQHGHOODODWHQ]DGLXQ¶LVWUX]LRQHQHLFRQIURQWLGLXQ¶DOWUD

•

•

•

Benchè la latenza di un’istruzione dipenda prevalentemente dal tempo di esecuzione dell’istruzione

stessa, più in generale è definita come proprietà di una coppia di istruzioni di cui la prima fornisce dei

risultati che vengono utilizzati come operandi dalla seconda. La generalizzazione è necessaria poichè in

alcuni casi il numero di stalli che è necessario introdurre per attendere la disponibilità dei risultati della

prima istruzione dipende anche dalla natura dell’istruzione che segue. Ad esempio, nel DLX un salto

condizionato ha bisogno del valore della condizione nella fase di ID, anzichè nella fase di EX,

determinando un ciclo di stallo in piu’ nel caso in cui i dati non siano già disponibili.

Si utilizza un CUT0 composto solo dalle due istruzioni e se ne valuta il CPUT utilizzando una coppia di

benchamrk incrementali come al paragrafo 2.3. Il valore che si ottiene è CPUT(CUT0).

Si crea un nuovo CUT, detto CUT1, in cui tra le due istruzioni è inserita una terza istruzione DUMMY

indipendente dalle altre due per dati e risorse. Si valuta CPUT(CUT1) con una coppia di benchmark

incrementali come al punto precedente.

Facoltà di Scienze MM FF NN – Università di Urbino – A.A. 2001/2002

4

Informatica Applicata – Progettazione dei sistemi di elaborazione

•

•

•

•

•

•

•

•

© Alessandro Bogliolo

Si creano nuovi CUT, detti CUT<n>, in cui tra le due istruzioni sono inserite <n> istruzioni DUMMY

uguali tra loro e indipendenti dalle due originali e tra loro. Per ogni CUT si valuta CPUT(CUT<n>) con

una coppia di benchmark incrementali come al punto precedente.

Si costruisce un grafico di CPUT(CUT<n>) in funzione di <n>. Il grafico presenta un primo tratto costante

e un secondo tratto crescente linearmente. Il tratto costante indica che le istruzioni DUMMY inserite tra

le due istruzioni oggetto di studio non aumentano il tempo di esecuzione complessivo poichè

sostituiscono cicli di stallo della pipeline dovuti alla latenza. Il tratto lineare indica invece che le nuove

istruzioni influenzano il tempo di CPU perchè non sono più coperte dalla latenza. Quindi il valore della

latenza puo’ essere ricavato dal valore di <n> in cui la curva cambia pendenza. Detto N il piu’ grande

valore di <n> per cui CPUT(CUT<n>)=CPUT(CUT0), N indica quante istruzioni DUMMY possono essere

eseguite rimpiazzando i cicli di stallo dovuti alla latenza in esame.

Nota: N rappresenta il numero di cicli di stallo misurati in termini di CPI dell’istruzione DUMMY.

Supponendo che il numero di cicli di stallo sia 10, se ogni istruzione DUMMY avesse CPI=1, N sarebbe

uguale a 10, se ogni istruzione DUMMY avesse CPI=2, N sarebbe uguale a 5, se ogni istruzione

DUMMY avesse CPI=3, N sarebbe uguale a 3. Per sapere il numero effettivo di cicli di stallo occorre

quindi conoscere il CPI di DUMMY.

Il CPI di DUMMY può essere ricavato dalla pendenza della curva nel tratto lineare crescente. Infatti vale

la seguente relazione:

CPI(DUMMY) = CPUT(CUT<n+1>)-CPUT(CUT<n>)

per n>N

L’effettivo numero di cicli di stallo può quindi essere calcolato moltiplicando CPI(DUMMY) per N.

Nota: nel caso in cui il numero di cicli di stallo non sia multiplo intero del CPI(DUMMY), la misura fornita

dal prodotto di cui al punto precedente è approssimata per difetto. Per eliminare tale approssimazione,

al posto di N si può usare il valore X che rappresenta l’ascissa del punto di intersezione tra la retta

orizzontale che interpola il tratto costante e la rette con pendenza positiva che interpola il tratto

crescente del grafico. Nel caso in cui il numero di cicli di stallo non sia multiplo del CPI(DUMMY), il

valore di X non sara’ intero.

Tenendo conto che la latenza è definita come numero di cicli di stallo + 1, la latenza in oggetto è data

da:

Lat(I1,I2) = X*CPI(DUMMY)+1

Nota: se I1 e I2 sono istruzioni dello stesso tipo si pone il problema di discriminare tra latenza e

repetition time. Per questo si veda il paragrafo 2.7.

9DOXWD]LRQHGHOUHSHWLWLRQWLPHGLXQDFRSSLDGLLVWUX]LRQL

•

•

•

Il repetition time dipende dai conflitti di risorse. In senso stretto il repetition time è tempo minimo che

deve intercorrere tra l’esecuzione di due istruzioni di uno stesso tipo, ma in generale può essere definito

come tempo minimo che deve intercorrere tra l’esecuzione di due istruzioni, assumendo che queste non

abbiano dipendenze di dati.

Si utilizza un CUT0 composto solo dalle due istruzioni e se ne valuta il CPUT utilizzando una coppia di

benchamrk incrementali come al paragrafo 2.3. Il valore che si ottiene è CPUT(CUT0).

Si procede come descritto nel paragrafo precedente, ottenendo:

Rep(I1,I2) = X*CPI(DUMMY)+1

&RPHGLVFULPLQDUHWUDODWHQ]DHUHSHWLWLRQWLPH

•

•

•

Per discriminare tra latenza e repetition time nel caso in cui le due istruzioni I1 e I2 in esame siano dello

stesso tipo è sufficiente ripetere l’esperimento descritto al paragrafo precedente utilizzando istruzioni

con e senza dipendenza di dati.

Se si ottengono gli stessi risultati, allora la latenza è mascherata dal repetition time, cioè il ripetition time

è maggiore o uguale alla latenza, e non c’è modo di isolare l’effetto della latenza, se non utilizzando

come seconda istruzione (che impiega i risultati della prima) un’istruzione di tipo diverso.

Se si ottengono risultati diversi allora la latenza è superiore al repetition time

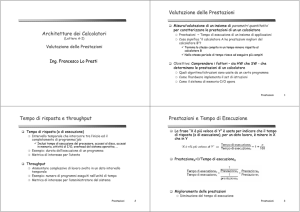

&RPHGLVFULPLQDUHWUDSLSHOLQLQJHUHSOLFD

•

•

•

•

•

Se un’unità di esecuzione non è nè pipelined, nè replicata, latenza e repetition time delle istruzioni la cui

esecuzione è affidata a quell’unità coincidono

Il pipelining riduce il repetition time, ma non la latenza

La replica dell’unità di esecuzione ha un effetto analogo: riduce il repetition time, ma non la latenza

In condizioni ideali, sia pipelining sia replica riducono il repetition time a 1, indipendentemente dalla

latenza

La differenza tra pipelining e replica si osserva in caso di ripetizioni multiple di istruzioni dello stesso tipo.

In particolare, se il numero di repliche dell’unità di esecuzione è inferiore alla latenza di ciascuna di esse,

Facoltà di Scienze MM FF NN – Università di Urbino – A.A. 2001/2002

5

Informatica Applicata – Progettazione dei sistemi di elaborazione

•

•

•

•

© Alessandro Bogliolo

ripetendo istruzioni dello stesso tipo si creano conflitti di risorse nell’implementazione con replica, mentre

non se ne creano nell’implementazione pipelined.

Per evidenziare il fenomeno è possibile utilizzare dei benchmark incrementali in cui il CUT sia costituito

da un numero crescente <n> di istruzioni in sequenza del tipo in esame, e senza dipendenze di dati

Se il tempo di CPU del CUT (rispetto al benchamrk di riferimento senza CUT) aumenta linearmente

all’aumentare di <n>, l’unità è pipelined, o replicata un numero di volte almeno pari alla latenza.

Se l’unità non è pipelined e le repliche sono inferiori alla latenza, allora il grafico del tempo di CPU in

funzione di <n> è lineare a tratti, con salti posizionati in corrispondenza dei valori di <n> multipli del

numero di repliche, e di ampiezza pari alla differenza tra la latenza e il numero di repliche.

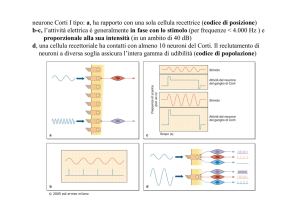

La figura seguente mostra l’andamento di CPUT(CUT<n>) in funzione di <n> in diverse implementazioni

di un’istruzione la cui unità di esecuzione richiede 4 cicli di clock.

40

35

Pipelined

Replica >= 4

Replica 3

Replica 2

Replica 1

&387&87Q!

30

25

20

15

10

5

0

1

2

3

4

5

Q!

6

7

8

9

10

&RPHFDUDWWHUL]]DUHLVDOWL

1. Anche i salti, condizionati e incondizionati, possono essere caratterizzati inserendoli nel CUT di

opportuni benchmarks. In particolare è possibile definire dei salti che bypassino una o più istruzioni del

CUT. Per caratterizzare il CPI di un salto condizionato la cui condizione non è verificata si può inserire

nel CUT un’unica istruzione di salto con condizione mai verificata e misurare il CPUT del benchmark per

confronto con quello di riferimento con CUT vuoto. Per caratterizzar il CPI di un salto condizionato a cui

condizione è verificata si può utilizzar un CUT in cui il salto (condizionato ad una condizione sempre

vera) è la prima istruzione del CUT e porta alla prima istruzione successiva al CUT.

/DERUDWRULRPLFUREHQFKPDUNLQFUHPHQWDOLSHU&38FKDUDFWHUL]DWLRQ

6FHOWHLPSOHPHQWDWLYH

*&&,QOLQHDVVHPEO\

(VHPSL

2WWLPL]]D]LRQLGLQDPLFKH

2XWRIRUGHUH[HFXWLRQ222[HP c3.7]

Il riordinamento dinamico delle istruzioni effettuato dal processore offre ulteriori opportunità di ottimizzazione,

ma pone numerose difficoltà implementative e complica notevolmente la logica di controllo. Il mantenimento

della coerenza sequenziale puo’ essere compromesso da tre tipi di conflitti di dati:

• 5HDGDIWHUZULWH (RAW): un’istruzione deve utilizzare come operando un risultato prodotto da

un’istruzione precedente. In tal caso è importante che la lettura dell’operando avvenga dopo la scrittura

del risultato. Questo è il conflitto di dati propriamente detto, legato alla dipendenza funzionale.

Facoltà di Scienze MM FF NN – Università di Urbino – A.A. 2001/2002

6

Informatica Applicata – Progettazione dei sistemi di elaborazione

© Alessandro Bogliolo

:ULWHDIWHUZULWH (WAW): due o più istruzioni aggiornano lo stesso registro interno. Se l’ordine di

esecuzione delle istruzioni viene modificato si rischia che il valore finale de registro non sia quello

logicamente corretto.

• :ULWHDIWHU5HDG(WAR): un’istruzione legge il contenuto di un registro ed un’istruzione successiva lo

sovrascrive. Cambiando l’ordine si rischia che la sovrascrittura preceda la lettura sporcando il dato. In

questo caso si parla di DQWLGLSHQGHQ]D, in quanto due istruzioni logicamente indipendenti finiscono per

essere dipendenti a causa della condivisione di un registro. I principali accorgimenti che rendono possibile l’esecuzione fuori ordine sono i seguenti:

• Decentramento del controllo dei conflitti (un controller per ogni unità di esecuzione)

• Distribuzione broadcast dei risultati attraverso un bus comune

• Rinomina dei registri per risolvere eventuali conflitti

I supporti architetturali sono i seguenti (fig. 3.29):

• Fasi di ,QVWUXFWLRQGHFRGH e 5HJLVWHUIHWFK separate

• ,QVWUXFWLRQTXHXH

• 5HVHUYDWLRQVWDWLRQ

• &RPPRQGDWDEXV

• 5HRUGHUEXIIHU

In un processore OOO si distinguono 4 fasi i esecuzione di ogni istruzione:

1. ,VVXH (indica il momento in cui un’istruzione è affidata ad una reservation station)

2. ([HFXWH (indica l’effettiva eseuzione da parte dell’unità di esecuzione)

3. :ULWH (indica la scrittura dei risultati, attraverso il common data bus, sul ROB)

4. &RPPLW (indica il write back dei risultati nel register file)

•

%UDQFKSUHGLFWLRQ[HP c3.5]

Maggiori sono il grado di parallelismo e il numero di istruzioni pre-processate contemporaneamente,

maggiore è la perdita relativa di performance dovuta alla non-predicibilità del flusso di istruzioni. Per questo

è utile fare previsioni attendibili sui salti condizionati, per poter continuare a fare fetch e decodifica delle

istruzioni seguenti prima di aver eseguito il salto. Tali previsioni si basano su informazioni statistiche molto

semplici aggiornate dinamicamente per ciascuna istruzione di salto. Il supporto hardware alla previsione dei

salti condizionati è di due tipi:

• %UDQFKSUHGLFWLRQEXIIHU

• %UDQFKWDUJHWEXIIHU

&DUDWWHUL]]D]LRQHGLSUHVWD]LRQLGLSURFHVVRULFRQ222

La caratterizzazione delle prestazioni dei processori OOO mediante microbenchmark incrementali è resa

complessa dallo scarso controllo che il programmatore ha sull’effettivo ordine di esecuzione delle istruzioni.

• Perchè venga preservato l’ordine di esecuzione delle istruzioni del CUT durante l’esecuzione occorre

che tali istruzioni siano nell’ordine più conveniente e che non sia conveniente mescolarle dinamicamente

a quelle esterne al CUT. Questo requisito di ottimalità rende più complessa la creazione di microbenchmarks ed inefficaci i microbenchmarks descritti ai capitoli 2 e 3.

• Caso 1: se il CUT contiene due istruzioni con conflitto di dati o di risorse seguite da una o più istruzioni

indipendenti, l’esecuzione avverrà OOO falsando il risultato. Per ovviare a questo inconveniente occorre

utilizzare CUT con istruzioni in ordine ottimo

• Caso 2: se il CUT contiene due istruzioni con conflitto di dati o di risorse, in fase di esecuzione alcune

delle istruzioni indipendenti esterne al CUT verranno eseguite tra le due istruzioni del CUT. Per ovviare

a questo inconveniente occorre utilizzare benchamrk di natura diversa, come descritto nel seguente

paragrafo.

0LFUREHQFKPDUNLQFUHPHQWDOLFRQ&87ULSHWXWR

•

•

•

Per verificare che i tempi di esecuzione del CUT non siano falsati dall’esecuzione fuori ordine di

istruzioni esterne al CUT, è possibile utilizzare benchmarks in cui la sequenza di istruzioni in esame

compaia ripetutamente nel CUT. Indicando con <m> il numero di repliche della sequenza di istruzioni in

esame, si costruiscono benchmark incrementali che contengano un numero crescete di repliche,

graficando il CPUT in funzione di <m>. Quando l’andamento diventa lineare è segno che le istruzioni

esterne al CUT non sono più utilizzabili per eliminare gli stalli interni al CUT, e il CPUT del CUT è

misurabile come differenza tra i CPUT di due benchmark con <m+1> ed <m> repliche.

Del resto occorre progettare il CUT in modo tale che non sorgano opportunità di esecuzione fuori ordine

di istruzioni prese da due repliche contigue del CUT. Inoltre va osservato che in questo caso le

condizioni al contorno in cui vengono valutate le prestazioni di ciascun CUT sono dati dalle repliche del

CUT stesso, e quindi non sono indipendenti dal CUT.

Esempio:

Facoltà di Scienze MM FF NN – Università di Urbino – A.A. 2001/2002

7

Informatica Applicata – Progettazione dei sistemi di elaborazione

© Alessandro Bogliolo

code segment A;

for (i = 0; i < N; i++) {

code segment B;

CUT;

CUT;

CUT;

CUT;

CUT;

code segment C;

}

code segment D;

dove ciascun CUT è composto da una somma floating point e da un nop, tutti i CUT utilizzano gli

stessi dati e il CUT evidenziato in grassetto è quello il cui CPUT non è mascherato da esecuzioni fuori

ordine

•

In questo tipo di benchmark i segmenti di codice B e C non sono necessari, poichè l’effetto

dell’eventuale accoppiamento tra iterazioni successive viene comunque eliminato incrementando il

numero di repliche del CUT interne ad ogni ciclo.

(VHPSLRO¶DUFKLWHWWXUD3GL,QWHO[HP c3.10]

•

•

•

•

•

•

µRSV (µFRGH) simili alle istruzioni di un processore RISC

3 istruzioni IA-32 caricate, decodificate e tradotte per ciclo di clock

6 µRSVgenerati per ciclo di clock

• se un’istruzione viene tradotta in più di 4 µRSVallora la traduzione è distribuita su più cicli di clock

lo scheduling delle µRSVè dinamico e OOO

supporta issuing e committment di un massimo di 3 µRSVper ciclo di clock

La pipeline intera è a 14 stadi

• la pipeline di esecuzione va da 1 a 32 cicli

• PDFURSLSHOLQH a 5 elementi [figura 3.49]

3URFHVVRULDEDVVRFRQVXPRGLSRWHQ]D

/¶HTXD]LRQHGHOFRQVXPRGLSRWHQ]D

•

L’energia minima necessaria a far commutare dal valore logico basso al valore logico alto l’uscita di un

gate CMOS è

(=

•

=∞

∫ 9 W , W GW = 94 =9

2

&

=0

dove V(t) e I(t) sono valori istantanei della tensione di alimentazione e della corrente assorbita dal gate,

V è il valore (assunto costante) della tensione di alimentazione, C è la capacità di carico del gate e Q è

la quantità di carica trasferita dall’alimentazione al condensatore per supportare la variazione di tensione

d’uscita da 0 a V (secondo la nota relazione Q=CV).

Se in un periodo di clock di durata T l’uscita del gate commuta dal basso verso l’alto, la potenza media

consumata durante il periodo è

3=

•

( 9 2&

=

7

7

Se indichiamo con α la probabilità che in determinate condizioni operative l’uscita del gate commuti dal

basso verso l’alto in un generico periodo di clock, la potenza media consumata dal gate in quelle

condizioni operative è:

3=

9 2&

α

7

ottenuta trascurando la potenza consumata dal gate quando non commuta e quando ha una transizione

dall’alto verso il basso. Il corrispondente consumo di energia è:

( = 9 2 &α1 dove Nclk è il numero totale di cicli di clock (nei microprocessori indicato con CPUC)

Facoltà di Scienze MM FF NN – Università di Urbino – A.A. 2001/2002

8

Informatica Applicata – Progettazione dei sistemi di elaborazione

•

© Alessandro Bogliolo

La potenza media consumata da un circuito composto da N gates può essere espressa in modo analogo

come somma dei contributi dei singoli

gates:

92

3=

7

92

&α =

& ∑

7

=1

∑& α

=1

& 92

=

& α = 9 2 )& α 7

2SSRUWXQLWjGLULGX]LRQHGHOFRQVXPRGLSRWHQ]D

•

•

•

•

•

•

•

Riduzione delle capacità di carico. La capacità di carico si riduce per effetto dello scaling tecnologico e di

scelte progettuali a livello elettrico e gate.

Riduzione del numero di componenti. Ottimizzazione logica.

Riduzione della probabilità di commutazione. Ottimizzazione a livello logico e a livello RT.

Tensione di alimentazione. La riduzione delle tensioni di alimentazione (che accompagna lo scaling

tecnologico) produce un beneficio quadratico sul consumo di potenza.

Frequenza operativa. La riduzione della frequenza operativa produce un risparmio lineare di potenza.

Vantaggi in termini di potenza e di energia

• Ridurre la tensione di alimentazione produce un risparmio quadratico di potenza e di energia

• Ridurre la frequenza operativa produce un risparmio lineare di potenza, ma non produce alcun

risparmio di energia, in quanto aumenta il tempo totale di esecuzione necessario a portare a termine

un certo task. Si noti infatti che la frequenza operativa (o il periodo di clock) non compaiono

nell’equazione dell’energia.

Legame tra Tensione e Frequenza

Tensione di alimentazione e frequenza operativa non sono scorrelati: abbassando la tensione di

alimentazione si riducono le prestazioni dei gate CMOS. In prima approssimazione, ed entro un range di

variabilità limitato, la performance di un gate CMOS è proporzionale alla tensione di alimentazione.

Quindi, riducendo la tensione occorre ridurre in ugual misura la frequenza. Indicando con Fil fattore di

riduzione della tensione di alimentazione e assumendo di ridurre in ugual misura la frequenza operativa,

3

2

il consumo di potenza si riduce di F , mentre l’energia si riduce di F .

'\QDPLFSRZHUPDQDJHPHQW

•

•

•

•

Cosiccome le prestazioni di un microprocessore possono essere incrementate con accorgimenti di

ottimizzazione dinamica, anche il consumo di potenza puo’ essere ulteriormente ridotto sfruttando

opportunità di ottimizzazione che si creano dinamicamente in quanto dipendono dalle condizioni

operative, incognite in sede di progetto.

L’ottimizzazione dinamica del consumo di potenza prende il nome di G\QDPLFSRZHUPDQDJHPHQW

'30.

Il DPM sfrutta il fatto che i sistemi a microprocessore sono progettati per garantire prestazioni di picco

quando richieste, ma l’effettivo carico di lavoro il più delle volte richiede prestazioni molto inferiori a

quelle di picco sostenibili dal sistema. In tali condizioni è quindi concettualmente possibile ridurre le

prestazioni al minimo indispensabile per risparmiare potenza.

Le tecniche DPM sono principalmente di quattro tipi:

1. spegnimento dei componenti non utilizzati (annullando la tensione di alimentazione di un

componente se ne annulla il consumo, ma il prezzo da pagare è la perdita dello stato interno e la

latenza nella riaccensione)

2. bloccaggio del clock dei componenti non utilizzati (bloccando il clock si riduce l’attività, cioè la

probabilità di commutazione, dei nodi del circuito, riducendo al minimo il consumo di potenza. In

questo caso lo stato interno del componente non viene perso e il risveglio ha latenza trascurabile)

3. riduzione della frequenza operativa (portandola al minimo indispensabile a garantire la prestazione

richiesta dal carico di lavoro corrente)

4. riduzione della tensione di alimentazione (portandola al minimo necessario a garantire prestazioni

compatibili con la frequenza operativa del circuito)

(VHPSLRGLSURFHVVRUHSRZHUPDQDJHDEOH,QWHO;6FDOH

>GDFRPSOHWDUH@

(VHPSLRGLSURFHVVRUHDEDVVRFRQVXPR7UDQVPHWD&UXVRH

>GDFRPSOHWDUH@

Facoltà di Scienze MM FF NN – Università di Urbino – A.A. 2001/2002

9

Informatica Applicata – Progettazione dei sistemi di elaborazione

© Alessandro Bogliolo

Fig 3.29

Fig. 3.49

Facoltà di Scienze MM FF NN – Università di Urbino – A.A. 2001/2002

10