28/03/17

Università degli Studi di Cagliari

Facoltà di Scienze

Corso di Laurea in Matematica

Corso di Elementi di Informatica

Lezione 5

28 marzo 2017

Dott. Paolo Garau

A.A. 2016/2017

[email protected]

1

Paolo Garau

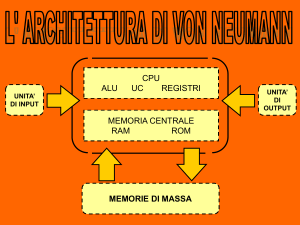

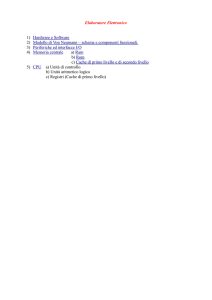

Schema Funzionale dell’elaboratore

Schema dell’elaboratore

CPU

Memoria

Secondaria

Periferiche

collegate

Interfaccia I/O

Interfaccia I/O

Memoria

Centrale

BUS di Connessione

Paolo Garau

2

1

28/03/17

Schema Funzionale dell’elaboratore

Schema funzionale dell’elaboratore

Unità di

Elaborazione

(CPU)

2

1

Input (Dati in

Ingresso)

3

4

Memoria

Centrale

Output (Dati

in Uscita)

Quando noi utilizziamo un elaboratore e facciamo un input andiamo a

scrivere direttamente sulla memoria o ci serviamo di qualche altro

apparecchio?

E quando facciamo un output andiamo a leggere direttamente dalla

memoria?

3

Paolo Garau

Rappresentazione delle informazioni

Unità di

Elaborazione

(CPU)

3

4

Memoria

Centrale

Input (Dati in

Ingresso)

Paolo Garau

1

2

5

Periferiche

di Input

Periferiche

di Output

6

Output (Dati

in Uscita)

4

2

28/03/17

Schema Funzionale dell’elaboratore

L’elaboratore

Ø La memoria centrale (RAM)

-

contiene

le

istruzioni

e

i

dati

che

devono

essere

rispettivamente eseguite ed elaborati dal processore, oltre ai

risultati ottenuti dall’esecuzione di ogni singola istruzione.

Ø Il processore

-

esegue le istruzioni, elabora i dati dopo averli prelevati dalla

memoria e trasferisce i risultati ottenuti dall’esecuzione

dell’istruzione nella memoria.

5

Paolo Garau

La memoria Centrale

La memoria Centrale (RAM)

l

La memoria centrale può essere

intesa come una successione

ordinata di bit.

l

I

bit

della

memoria

sono

raggruppati in celle o locazioni di

memoria di lunghezza fissa

(solitamente

1

byte),

ognuna

identificata in modo univoco da

un indirizzo.

Paolo Garau

6

3

28/03/17

La memoria Centrale

Ø Le celle di memoria sono raggruppate in parole (word) di uguale

lunghezza.

• il numero di bit che costituisce la parola viene detto lunghezza

di parola (oggi 32/64 bit per PC e 128 bit per calcolatori più

potenti).

Ø La lunghezza della parola di memoria è un elemento fondamentale

della memoria centrale e di tutto il calcolatore (corrisponde al

numero di bit che la CPU può trattare simultaneamente)

7

Paolo Garau

La memoria Centrale

WORD a 16bit

Paolo Garau

8

4

28/03/17

Diversi tipi di Memorie

Distinzione dei diversi tipi di memorie

l

La memoria centrale è costituita principalmente dalla memoria RAM

che contiene temporaneamente i dati da eseguire o porzioni di

programma.

-

RAM (Random Access Memory)

• La memoria ROM contiene il firmware

-

ROM (Read Only Memory)

9

Paolo Garau

Diversi tipi di memorie

Distinzione dei diversi tipi di memorie

La RAM (Random Access Memory) contiene le istruzioni e i dati dei

programmi in esecuzione

-

Paolo Garau

Costituisce la quasi totalità della memoria centrale

Memoria di lettura/scrittura

Volatile

Accesso diretto alle informazioni memorizzate.

Veloce (tempo di accesso costante e molto basso 60-70 ns, dove

1 ns=10-9 s)

Capacità limitata (qualche Gbyte)

Molto costosa ($)

10

5

28/03/17

Diversi tipi di memorie

La ROM (Read Only Memory) è la memoria che contiene tutti

programmi necessari all’avviamento del sistema di calcolo (bootstrap)

-

Memoria di sola lettura

-

Permanente

-

Capacità molto limitata (dell’ordine delle centinaia di Kbyte)

-

Tra i principali programmi presenti nella ROM ricordiamo il

BIOS che consente il caricamento del Sistema Operativo dal

disco. Questo tipo di software viene chiamato firmware perché

consente di mettere in comunicazione l’hardware con il software

di livello superiore.

11

Paolo Garau

Il Processore

Il processore CPU (Central Processing Unit)

E’ formato da due unità

Paolo Garau

-

Unità logico-aritmetica (ALU Aritmetic Logic Unit)

-

Unità di controllo (CU Control Unit)

12

6

28/03/17

Il Processore

Unità logico-aritmetica (ALU)

l

Costituita da circuiti in grado di eseguire le operazioni logiche (>,<, =, etc…)

e aritmetiche (+,-,*,/, etc…).

Unità di controllo (CU)

Preleva l’istruzione da eseguire dalla memoria e la porta al suo interno (fase di

prelevamento o fetching).

l Analizza l’istruzione per determinare l’operazione da eseguire e gli eventuali

operandi (fase di decodifica).

l Comanda l’unità preposta ed esegue le istruzioni attivando i circuiti (fase di

esecuzione).

l Terminata l’ultima fase l’unità di controllo riprende dalla prima fase in

maniera ciclica.

l

13

Paolo Garau

Il Processore

Dettaglio del ciclo del Processore

1) Dati ed istruzioni stanno nella

memoria RAM.

2) Si prelevano le istruzioni dalla

memoria RAM per essere decodificate

in operazioni da svolgere.

3) Il risultato della decodifica viene

salvato nei registri delle istruzioni.

4) Si prelevano i dati da elaborare dalla

memoria che vengono poi caricati nei

registri dei dati della CPU.

5) La ALU prende dai registri le

istruzioni e i dati, e gli elabora.

6) Il risultato viene rimesso nei registri o

nella memoria.

7) Dai registri vengono letti i risultati per

che verranno poi caricati in memoria.

Paolo Garau

14

7

28/03/17

Il Processore

I registri della CPU

Nello svolgimento delle proprie attività le unità dell’elaboratore

si servono dei registri:

-

piccole memorie di supporto temporanee per contenere dati,

istruzioni o indirizzi di memoria;

-

memorie volatili di limitatissima capacità ma con un tempo di

accesso estremamente basso;

-

velocità di lettura/scrittura superore della memoria RAM.

Paolo Garau

15

Il Processore

Due tipologie di processori

Esistono due grandi famiglie di processori

Processori RISC (Reduced Instruction Set Computer)

Sono dei processori che hanno un Instruction Set molto limitato, ovvero

conoscono poche operazioni. Questi però da queste istruzioni di base

riescono a risolvere anche i calcoli più complessi. Ad esempio

l’elevazione a potenza. [Elaboratori General Purpose]

Processori CISC (Complex Instruction Set Computer)

Sono quei processori che sono ricchi di istruzioni specifiche e dedicate ad

uno scopo ben definito. L’alta specificità di queste operazioni non

consente di poter risolvere qualsiasi genere di operazione in tempi ridotti.

Le prestazioni che si ottengono sono molto elevate per un contesto

specifico ma scarse per uno generico. [Elaboratori Specific Purpose]

Paolo Garau

16

8

28/03/17

Il Processore

Velocità del Processore

MIPS (Milioni di Istruzioni Per Secondo), usata tradizionalmente.

-

l

Con l’avvento dei personal computer si è diffusa l’usanza di misurare

la velocità di un processore con la frequenza del clock (orologio).

-

-

l

Gli attuali processori hanno una velocità di migliaia di MIPS.

La frequenza del clock corrisponde al numero di operazioni

elementari, eseguibili nell’unità di tempo e si misura in Hertz

(1Hertz corrisponde ad una operazione al secondo).

Gli attuali processori hanno una frequenza di alcuni GHz

(eseguono miliardi di operazioni elementari al secondo)

La frequenza del clock da solo non è una misura oggettiva della

velocità di elaborazione di un processore perchè dipende anche da

altri fattori (lunghezza della parola di memoria, velocità del bus, etc.)

Paolo Garau

17

Altre memorie

Le memorie Cache

l

Le memorie cache nascono dall’esigenza di adeguare la velocità delle

RAM a quella degli attuali processori, sempre più in aumento.

l

Per evitare che il processore perda tempo ad aspettare i dati dalla

RAM, si inserisce una cache, che è più veloce ma più piccola, tra i due

per contenere i dati più frequentemente usati.

l

In tal modo, la prima volta che il processore carica i dati dalla RAM,

tali dati vengono caricati anche sulla cache, cosi che le volte

successive vengono cercati prima nella cache e poi nella RAM. Se i

dati non dovessero essere nella cache vengono caricati. Così facendo

nella cache ci sono sempre i dati utilizzati più di recente.

Paolo Garau

18

9

28/03/17

Altre memorie

Le memorie di Massa

• Sono permanenti (permettono di conservare dati e

programmi nel tempo) a differenza della memoria centrale.

• Capacità maggiore di quella della memoria centrale

• Hanno un basso costo

• Hanno tempi di accesso più lunghi di quelli della memoria

centrale

• Non sempre hanno accesso diretto

19

Paolo Garau

Caratteristiche delle memorie

Criteri di caratterizzazione delle Memorie

l

Velocità di trasferimento

-

l

Tempo di accesso

-

l

Il numero di byte che la memoria è in grado di trasferire ad un

altro dispositivo in un secondo (sostanzialmente misura la

rapidità nelle operazioni di lettura/scrittura)

Il tempo che intercorre fra la richiesta di un’operazione di lettura

o scrittura e l’inizio dell’operazione (latenza).

Capacità

-

Paolo Garau

Cioè il numero di bit che possono essere memorizzati e sempre

espressa in byte.

20

10

28/03/17

Caratteristiche delle memorie

Criteri di caratterizzazione delle Memorie

l

Modalità di accesso

-

l

Diretta (o casuale)

Sequenziale

Mista

Tecnologia costruttiva

-

Magnetica

Ottica

Elettronica

Magneto-ottica

Paolo Garau

21

Caratteristiche delle memorie

Tecnologia delle memorie di massa

Paolo Garau

22

11

28/03/17

Caratteristiche delle memorie

Gerarchia delle memorie viste

REGISTRI

Memoria locale

Memoria centrale

CACHE

RAM

Memoria di massa

Paolo Garau

DISCHI

23

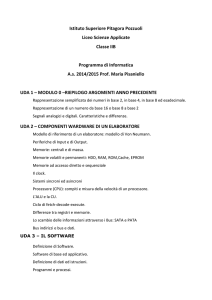

Architettura di Von Neumann

La macchina di Von Neumann

Paolo Garau

24

12

28/03/17

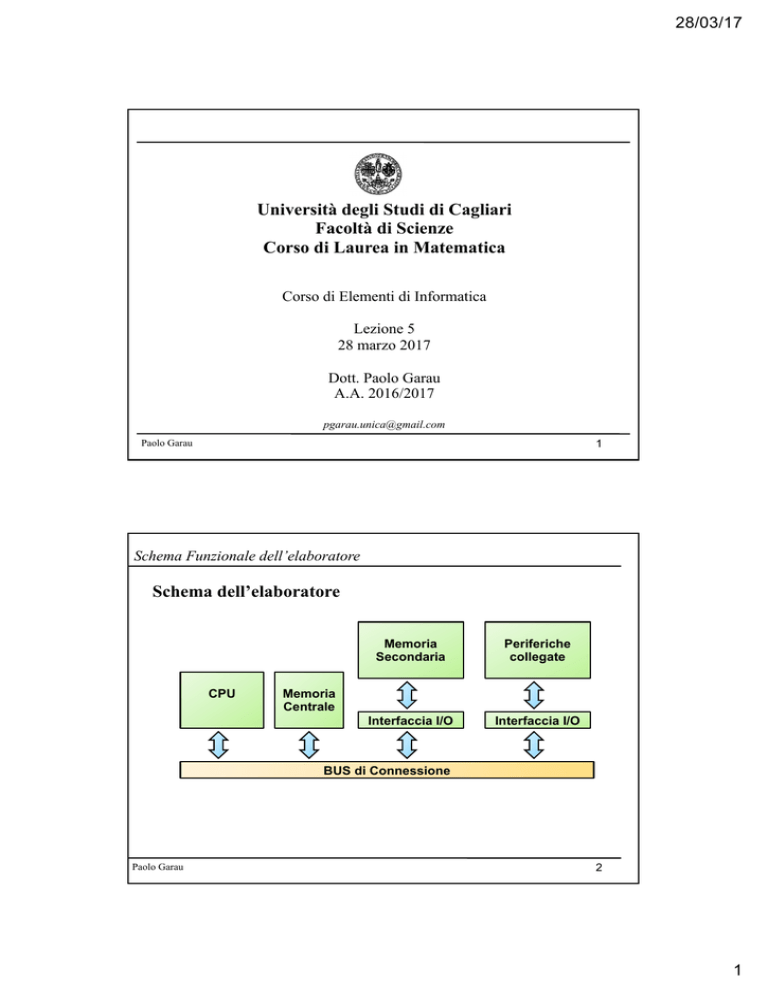

Bus di Sistema

Bus di Sistema

l

Il Bus di sistema interconnette la CPU, la memoria principale e

le interfacce delle periferiche

l

E’ costituito da un insieme di connessioni elementari disposte in

parallelo, dette linee, ciascuna in grado di trasferire

esattamente un bit.

l

Se

il

bus

dispone

di

n

linee

si

possono

trasferire

contemporaneamente n bit.

25

Paolo Garau

Bus di Sistema

l

E’ organizzato in tre gruppi di linee con specifiche funzioni:

-

l

bus dati, bus indirizzi, bus comandi.

Ai fini delle prestazioni dell’elaboratore è importante

-

che il numero di linee del bus sia adeguata alla lunghezza della

parola di memoria e a quella degli indirizzi della macchina.

-

Che la velocità di trasferimento sia adeguata

-

Gli attuali bus hanno una velocità che va da qualche

centinaia di MBps a qualche GBps.

Paolo Garau

26

13

28/03/17

Bus di Sistema

Modello del Bus di Sistema

Scheda

madre

(motherboar

d)

RAM

CPU

Bus dati

Bus

indirizzi

Bus di

controllo

Interfacc

e di I/O

Interfaccia di

I/O

Schermo

Paolo Garau

Tastiera e

mouse

Altoparlanti

Interfacc

e di I/O

Memoria di massa

27

14