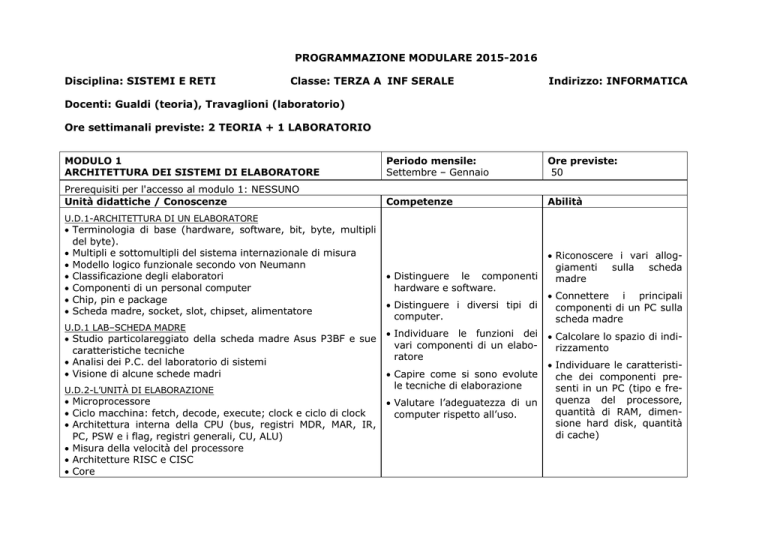

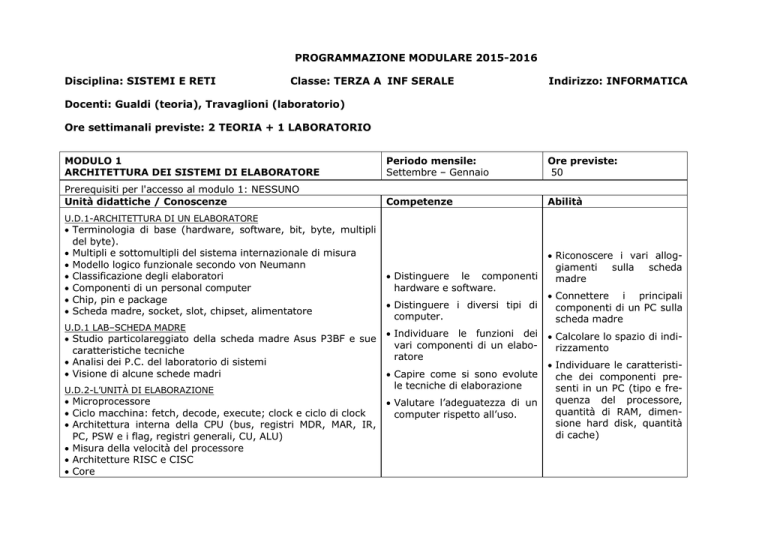

PROGRAMMAZIONE MODULARE 2015-2016

Disciplina: SISTEMI E RETI

Classe: TERZA A INF SERALE

Indirizzo: INFORMATICA

Docenti: Gualdi (teoria), Travaglioni (laboratorio)

Ore settimanali previste: 2 TEORIA + 1 LABORATORIO

MODULO 1

ARCHITETTURA DEI SISTEMI DI ELABORATORE

Periodo mensile:

Settembre – Gennaio

Ore previste:

50

Prerequisiti per l'accesso al modulo 1: NESSUNO

Unità didattiche / Conoscenze

Competenze

Abilità

U.D.1-ARCHITETTURA DI UN ELABORATORE

Terminologia di base (hardware, software, bit, byte, multipli

del byte).

Multipli e sottomultipli del sistema internazionale di misura

Modello logico funzionale secondo von Neumann

Classificazione degli elaboratori

Componenti di un personal computer

Chip, pin e package

Scheda madre, socket, slot, chipset, alimentatore

U.D.1 LAB–SCHEDA MADRE

Studio particolareggiato della scheda madre Asus P3BF e sue

caratteristiche tecniche

Analisi dei P.C. del laboratorio di sistemi

Visione di alcune schede madri

U.D.2-L’UNITÀ DI ELABORAZIONE

Microprocessore

Ciclo macchina: fetch, decode, execute; clock e ciclo di clock

Architettura interna della CPU (bus, registri MDR, MAR, IR,

PC, PSW e i flag, registri generali, CU, ALU)

Misura della velocità del processore

Architetture RISC e CISC

Core

Distinguere le componenti

hardware e software.

Riconoscere i vari alloggiamenti

sulla

scheda

madre

Distinguere i diversi tipi di

computer.

Connettere i principali

componenti di un PC sulla

scheda madre

Individuare le funzioni dei

vari componenti di un elaboratore

Calcolare lo spazio di indirizzamento

Capire come si sono evolute

le tecniche di elaborazione

Valutare l’adeguatezza di un

computer rispetto all’uso.

Individuare le caratteristiche dei componenti presenti in un PC (tipo e frequenza del processore,

quantità di RAM, dimensione hard disk, quantità

di cache)

U.D.3-LE MEMORIE

Tipi di memoria: RAM e ROM

Indirizzi delle celle di memoria

Gestione della memoria di un PC

Memorie flash: di tipo NOR e NAND

Memoria dinamica

U.D.4-LA GESTONE DELL’INPUT/OUTPUT

Dispositivi di I/O

Periferiche e controller

U.D.5-LE ARCHITETTURE NON VON NEUMANN

Evoluzione dei sistemi di elaborazione

Evoluzioni che riguardano l’elaborazione: esecuzione fuori ordine, prefetch, pipeline, tecnologie superscalari, branch prediction

Evoluzioni che riguardano la memoria centrale: cache memory, memoria virtuale

Evoluzioni che riguardano l’I/O: DMA

MODULO 2

FAMIGLIA X86

Periodo mensile:

Gennaio - Febbraio

Ore previste:

12

Prerequisiti per l'accesso al modulo 2: MODULO 1

Unità didattiche / Conoscenze

Competenze

Abilità

U.D.1-FAMIGLIE DI PROCESSORI

La famiglia x86

U.D.2-PROCESSORE 8086

Caratteristiche

Set di registri: generali, puntatori, IP, Flags, di segmento

La segmentazione della memoria. I registri di segmento e i

segmenti di memoria. Indirizzo segmentato e indirizzo fisico

U.D.3-IA-32

Il set di registri: generali, puntatori, IP, Flags, di segmento

Ambiente di esecuzione

Modalità operative

Modello segmentato di memoria in modalità protetta

Comprendere il concetto di

famiglia di processori.

Conoscere la dimensione dei

bus dati ed indirizzi, i nomi e

le dimensioni dei registri dell’8086 e dei suoi successori.

Calcolare un indirizzo fisico partendo da un indirizzo segmentato

U.D.4-EM64T

I processori a 64 bit

EM64T

MODULO 3

FONDAMENTI DI NETWORKING

Periodo mensile:

Febbraio - Aprile

Ore previste:

16

Prerequisiti per l'accesso al modulo 3: NESSUNO

Unità didattiche / Conoscenze

Competenze

Abilità

U.D.1-INTRODUZIONE AL NETWORKING

Reti: definizioni e concetti di base

Aspetti hardware delle reti: tecnologia trasmissiva, scala dimensionale

Reti locali

Topologia delle reti locali

Reti geografiche

Reti wireless

U.D.2-IL TRASFERIMENTO DELL’INFORMAZIONE

La trasmissione delle informazioni, modalità di comunicazione,

modalità di utilizzo del canale

Tecniche di trasferimento dell’informazione

Multiplazione

Tecniche di accesso

Classificazione delle tecniche di accesso multiplo: accesso

multiplo senza contesa, accesso multiplo con contesa, CDMA

La commutazione: commutazione di circuito, commutazione di

messaggio, commutazione di pacchetto

U.D.3-L’ARCHITETTURA A STRATI ISO-OSI E TCP-IP

L’architettura a strati

Il modello OSI: livello fisico, livello di collegamento dati, livello

di rete, livello di trasporto, livello di sessione, livello applicativo

Il modello TCP/IP: accesso in rete, internet layer, transport

layer, application layer, application layer

Classificare le reti in base

all’estensione

Individuare i campi di utilizzo

delle diverse topologie.

Comprendere i vantaggi di

una architettura a livelli.

Delineare i compiti dei livelli

OSI

Confrontare il modello

ISO/OSI con l’architettura

TCP/ IP

MODULO 4

DISPOSITIVI PER LA REALIZZAZIONE DI RETI LOCALI

Periodo mensile:

Aprile - Maggio

Ore previste:

14

Prerequisiti per l'accesso al modulo 4: MODULO 3

Unità didattiche / Conoscenze

Competenze

Abilità

Utilizzare la terminologia degli standard del cablaggio

strutturato

Realizzare un cavo di rete

diretto e incrociato

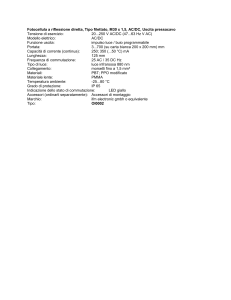

U.D.1-LA CONNESSIONE CON I CAVI IN RAME

Trasmissione di segnali elettrici via cavo

Tipologie di cavi: coassiale, doppino, classificazione dei doppini

Cavi: collegamento dei pin

U.D.2-LE MISURE SUI CAVI IN RAME

Caratteristiche elettriche: impedenza, AWG, velocità di propagazione, attenuazione, rumore, diafonia

Categorie e classi ISO

U.D.2 LAB–INTESTAZIONE DI UN CAVO UTP

Cablaggio diretto (standard EIA/TIA – 568B)

Cablaggio crossover – incrociato (standard EIA/TIA – 568B)

U.D.3–LA CONNESSIONE OTTICA

La trasmissione di segnali elettrici in fibra

La struttura di una fibra, ottica

Installazione, rumore e test sulle fibre ottiche

U.D.4–LA CONNESSIONE WIRELESS

La trasmissione di segnali wireless

Realizzazione di una rete wireless

Comunicazione wireless

La sicurezza nelle comunicazioni wireless

U.D.5–IL CABLAGGIO STRUTTURATO DEGLI EDIFICI

Standard internazionali

Lo standard EIA/TIA 568

Sviluppi tecnologici e normativi

U.D.5 LAB–CISCO PACKET TRACER

Interfaccia grafica

Aggiungere e collegare due dispositivi

Creazione di una rete LAN

Progettare il cablaggio strut- Realizzare delle reti locali

turato di un edificio e di un

di varia complessità con

campus

Cisco Tracer Pcket