Laboratorio di Elettronica T

Esperienza 3 – Gate CMOS

Postazione N°

Cognome

Nome

Matricola

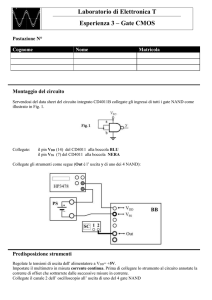

Montaggio del circuito

Servendosi del data sheet del circuito integrato CD4011B collegate gli ingressi di tutti i gate NAND come

illustrato in Fig. 1.

Collegate:

il pin VDD (14) del CD4011 alla boccola BLU

il pin VSS (7) del CD4011 alla boccola NERA

Collegate gli strumenti come segue (Out è l’ uscita y di uno dei 4 NAND):

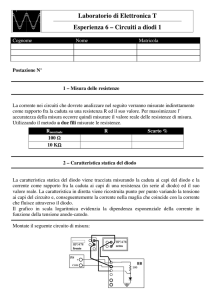

Predisposizione strumenti

Regolate le tensioni di uscita dell' alimentatore a VDD= +5V.

Impostate il multimetro in misura corrente continua. Prima di collegare lo strumento al circuito annotate la

corrente di offset che sottrarrete dalle successive misure in corrente.

Collegate il canale 2 dell’ oscilloscopio all’ uscita di uno del 4 gate NAND

1 - Analisi della funzionalità logica

Collegate gli ingressi a e b del NAND la cui uscita y è collegata all’ oscilloscopio a VDD o a massa come

illustrato nella tabella e registrare le corrispondenti tensioni di uscita e correnti di alimentazione. In

corrispondenza dei diversi stati degli ingressi il gate produrrà sull’ uscita il valore di tensione corrispondente

al valore logico del risultato dell’ operazione.

Va

Vb

VDD

VDD

0V

VDD

VDD

0V

0V

0V

Vy (V)

µA)

IDD (µ

Inserite la schermata attuale : premete ALT-F8 + “inserisci schermata”

2 - Misura della soglia (1) e della corrente di penetrazione

Applicate ora allo stesso gate usato al punto precedente le tre combinazioni di tensioni di ingresso indicate

nella Fig. 2.

Con i collegamenti illustrati in Fig. 2, l’ uscita del gate CMOS si fissa sulla soglia.

Misurate la tensione di soglia, cioè la tensione al nodo y, e la corrente di alimentazione IDD nelle diverse

configurazioni.

a

b

VTH (V)

IDD (µ

µA)

Inserite la schermata attuale : premete ALT-F8 + “inserisci schermata”

c

3 - Misura della soglia (2)

Rimuovete la capacità da 22nF.

Collegare il gate come segue:

Modificate i collegamenti con gli strumenti come segue:

Al fine di annullare l’ errore dovuto ai ritardi di propagazione e minimizzare le capacità parassite, utilizzate

cavi corti di uguale lunghezza per il collegamento all’ oscilloscopio.

Predisponete il generatore di funzione in modo che all’ ingresso del circuito sia imposto un segnale dalle

seguenti caratteristiche: :

• Livello alto 5V

• Livello basso 0V

• Genera onda triangolare frequenza 1 KHz simmetria 50%

N.B. la linea dal FG al circuito non è terminata: predisporre di conseguenza il FG.

Con i cursori, misurate la soglia di scatto del gate come punto di incrocio fra la forma d’ onda in ingresso e

quella di uscita.

VTH (salita)

VTH (discesa)

Inserite la schermata attuale : premete ALT-F8 + “inserisci schermata”

4 - Ritardo di propagazione (1)

Predisponete il generatore di funzione in modo che all’ ingresso del circuito sia imposto un segnale dalle

seguenti caratteristiche: :

• Livello alto 5V

• Livello basso 0V

• Genera onda quadra frequenza 1 KHz simmetria 50%

Misurate il ritardo fra il fronte applicato all’ ingresso del gate ed il conseguente fronte di commutazione dell’

uscita per le due commutazioni HL e LH. Utilizzate come soglia logica il valore misurato al puto 2.

Inserite la schermata relativa alla misura di tPLH: premete ALT-F8 + “inserisci schermata”

Inserite la schermata relativa alla misura di tPHL: premete ALT-F8 + “inserisci schermata”

Riportate i valori misurati nella seguente tabella

tPLH

tPHL

Confrontate il valore massimo misurato (caso peggiore) con la curva riportata sul data sheet.

A quale valore di capacità di carico CL corrispondono i valori ottenuti nell’ ipotesi che il dispositivo si

comporti in maniera tipica?

CL

5 - Ritardo di propagazione (2)

Modificare i collegamenti come indicato in Fig. 5.

Collegare il nodo OUT al canale 1 dell’ oscilloscopio e misurate la frequenza di oscillazione del ring

oscillator. Calcolate quindi il tempo di propagazione medio come tp=1/(2·f·N), dove N=3

f OUT

tP

Inserite la schermata attuale : premete ALT-F8 + “inserisci schermata”

Smontate il circuito e riponete i componenti nella busta .