Transistor MOS

Il transistor MOS è un dispositivo a 4 terminali (drain, gate, source, body di

seguito indicati D, G, S, B)

Esistono due tipologie di transistor MOS:

Tecnologia CMOS

Lucidi del Corso di Elettronica Digitale

Modulo 3

Transistor a canale N (NMOS), in cui i portatori di carica sono gli elettroni

Transistor a canale P (PMOS) ), in cui i portatori di carica sono le lacune

Le caratteristiche del PMOS sono duali rispetto a quelle del NMOS

E’ completamente simmetrico, i terminali di drain e source si possono

scambiare ruolo a seconda del funzionamento

Il ruolo di source è assunto, convenzionalmente, dal terminale (fra S e D) a

potenziale più basso (nel caso del nmos) o più alto (nel caso del pmos)

Il quarto terminale (B, body o bulk) può essere trascurato solo quando

cortocircuitato col source (cosa non sempre, o quasi mai, possibile). Negli

altri casi il body del nmos (pmos) deve essere collegato al potenziale più

basso (alto) presente nel circuito.

La caratteristica del dispositivo dipende da un insieme di parametri di

processo (tensione di soglia, mobilità, capacità dell’ossido) noti a priori una

volta scelta una determinata tecnologia, e da parametri geometrici (W e L)

determinabili dal progettista.

Università di Cagliari

Dipartimento di Ingegneria Elettrica ed Elettronica

Laboratorio di Elettronica (EOLAB)

10 Ottobre 2006

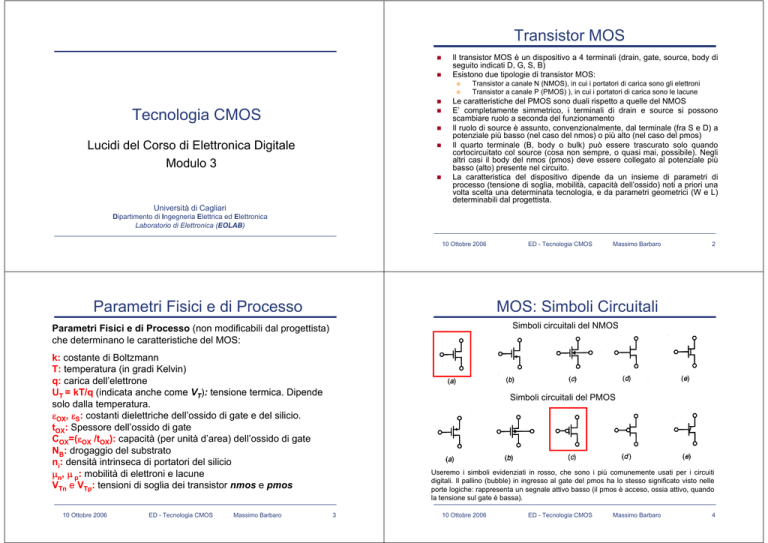

Parametri Fisici e di Processo

Massimo Barbaro

2

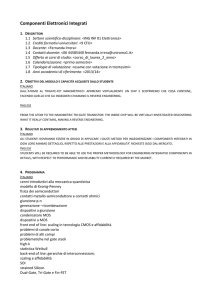

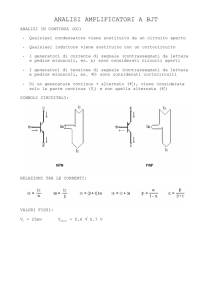

Simboli circuitali del NMOS

k: costante di Boltzmann

T: temperatura (in gradi Kelvin)

q: carica dell’elettrone

UT = kT/q (indicata anche come VT): tensione termica. Dipende

solo dalla temperatura.

εOX, εS: costanti dielettriche dell’ossido di gate e del silicio.

tOX: Spessore dell’ossido di gate

COX=(εOX /tOX): capacità (per unità d’area) dell’ossido di gate

NB: drogaggio del substrato

ni: densità intrinseca di portatori del silicio

µn, µ p: mobilità di elettroni e lacune

VTn e VTp: tensioni di soglia dei transistor nmos e pmos

ED - Tecnologia CMOS

Massimo Barbaro

MOS: Simboli Circuitali

Parametri Fisici e di Processo (non modificabili dal progettista)

che determinano le caratteristiche del MOS:

10 Ottobre 2006

ED - Tecnologia CMOS

Simboli circuitali del PMOS

Useremo i simboli evidenziati in rosso, che sono i più comunemente usati per i circuiti

digitali. Il pallino (bubble) in ingresso al gate del pmos ha lo stesso significato visto nelle

porte logiche: rappresenta un segnale attivo basso (il pmos è acceso, ossia attivo, quando

la tensione sul gate è bassa).

3

10 Ottobre 2006

ED - Tecnologia CMOS

Massimo Barbaro

4

Il transistor MOS: sezione trasversale

Struttura del transistor MOS (NMOS in questo caso)

Gate (polisilicio)

Source

Drain

VG>VTH

+ + + +

-

-

+++ + + + ++

Massimo Barbaro

10 Ottobre 2006

Il transistor MOS: triodo

- -

- --

Canale (formato se la tensione

di gate è maggiore della

tensione di soglia)

VB=0

5

-

ED - Tecnologia CMOS

Isolamento

(SiO2)

---

-

10 Ottobre 2006

Il substrato è di tipo P, quindi

ricco di portatori positivi

(lacune)

n+

-

p-Si (body)

VS=0

n+

n+

-

Ossido di gate

All’aumentare della tensione di gate (VG) rispetto al bulk (VB), il potenziale positivo

prima allontana i portatori positivi (lacune) naturalmente presenti nel silicio tipo P e

poi richiama dei portatori negativi (elettroni) nella zona immediatamente sotto il gate.

In tal modo si forma un canale conduttivo fra drain e source, non appena ilpotenziale

di gate supera una certa soglia (VTH)

++

Il transistor MOS: funzionamento

Se esiste il canale, applicando

una tensione positiva fra D e S si

può fare scorrere una corrente

elettrica (ID, corrente di drain)

ED - Tecnologia CMOS

VG1

VG2

VG3

VG3>VG2>VG1

n+

Massimo Barbaro

6

Per ulteriori incrementi della tensione di drain rispetto al source (VDS) ad un certo

punto la differenza di potenziale fra il gate ed il canale (in prossimità del drain)

diventa tanto piccola da diventare inferiore alla tensione di soglia ed il canale si

strozza (pinch-off)

Per aumenti della tensione di drain oltre questo limite (VG-VD=VTH, ossia

VDS=VGS-VTH) la corrente non aumenta più perché il canale è strozzato

VG>VTH

VG>VTH

n+

VD>0

Il transistor MOS: saturazione

Per basse tensioni di drain rispetto al source (VDS=VD-VS) il canale si comporta

come resistore (comportamento ohmico o lineare) e la corrente aumenta linearmente

con l’aumento della VDS.

Al variare della tensione di VGS (VG-VS) il canale diventa via via più popolato di

elettroni e quindi più conduttivo, quindi diminuisce il valore del resistore

Il transistor in triodo (o regione ohmica, o regione lineare) si comporta come un

resistore di valore variabile ed impostabile agendo sulla tensione di gate.

VS=0

n+

VD>0

VS=0

n+

n+

VD>0

Canale strozzato

VB=0

10 Ottobre 2006

All’aumentare di VGS vengono richiamati più elettroni nel

canale che diventa più conduttivo (lo spessore è più o

meno sempre lo stesso ma cambia la densità i portatori, la

grafica è volutamente esagerata per rendere il principio)

ED - Tecnologia CMOS

Massimo Barbaro

VB=0

7

10 Ottobre 2006

La condizione di strozzamento è:

VG – VD = VTH

Ossia

VG –VS – VD + VS = VTH => (VG-VS)-(VD-VS)=VTH

VDS = VGS - VTH

ED - Tecnologia CMOS

Massimo Barbaro

8

MOS come interruttore

MOS: modulazione lunghezza di canale

In realtà, per ulteriori aumenti della VDS, aumenta la polarizzazione ininversa della

giunzione pn fra drain e substrato, quindi aumenta la regione di carica spaziale

(RCS) di svuotamente della giunzione stessa.

L’effetto è quello di spostare verso sinistra il punto di pinch-off dunque diminuire la

effettiva lunghezza del canale.

A canale più corto corrisponde maggiore corrente (nell’unità di tempo riesce, a parità

di velocità a passare una maggiore quantità di carica)

In elettronica digitale il transistor MOS viene

fondamentalmente usato come interruttore, quindi in

prima approssimazione possiamo dire che:

VG>VTH

VS=0

VB=0

n+

n+

Il punto di strozzamento si sposta a

sinistra e diminuisce la lunghezza

del canale

10 Ottobre 2006

ED - Tecnologia CMOS

VD>0

La resistenza, quando il MOS (N o P) è acceso, dipende

dalla regione di funzionamento, in particolare è:

Regione di svuotamento

(RCS)

Massimo Barbaro

9

NMOS: è spento per tensioni gate-source minori della

tensione di soglia (VGS<VTn) ed è acceso ed equivalente ad

una resistenza RON per tensioni gate-source maggiori della

tensione di soglia.

PMOS: è spento per tensioni source-gate minori della

tensione di soglia in valore assoluto (VSG<|VTp|) ed è acceso

ed equivalente ad una resistenza (piccola) RON per tensioni

source-gate maggiori della tensione di soglia.

PICCOLA: se il transistor è in regione lineare (triodo)

GRANDE: se il transistor è in regione di saturazione (dipende

dalla modulazione di lunghezza di canale)

10 Ottobre 2006

ED - Tecnologia CMOS

Interruttore NMOS

VGS>VTn

S

VGS<VTn

Il terminale di source è

(tipicamente) quello in basso ed

è collegato alla massa

10 Ottobre 2006

ED - Tecnologia CMOS

10

Interruttore PMOS

RON

VSG>|VTp|

E’ sicuramente

acceso

se

VG=VDD

G

Massimo Barbaro

S

Massimo Barbaro

E’ sicuramente

acceso se VG=0

G

E’ sicuramente

spento se VG=0

VSG<|VTp|

Il terminale di source è

(tipicamente) quello in alto ed è

collegato all’alimentazione (VDD)

Circuito

aperto

11

RON

10 Ottobre 2006

ED - Tecnologia CMOS

E’ sicuramente

spento

se

VG=VDD

Circuito

aperto

Massimo Barbaro

12

MOS: calcolo della corrente (analitico)

In ogni punto x del canale (x=0 nel source, x=L) nel

drain, la corrente è data dalla carica per unità d’area,

moltiplicata per l’area percorsa dai portatori di carica

nell’unità di tempo

W

I DS = −Qi ( x)vn ( x)W

Quantità di carica per unità d’area

nel sistema MOS (la carica è

proporzionale a quanto la VG-V(x)

eccede la VTH)

L’area ricoperta dai portatori

nell’unità di tempo è data da un

rettangolo, largo come il canale e

lungo quanto lo spazio percorso dai

portatori nell’unità di tempo (ossia

la loro velocità)

W

vn

La velocità è proporzionale

al campo elettrico tramite il

parametro di mobilità

Qi ( x) = COX (VGS − V ( x) − VTH )

10 Ottobre 2006

Il campo elettrico

è la derivata del

potenziale

ED - Tecnologia CMOS

vn ( x ) = µ n E ( x )

E ( x) = −

I DS = WCOX (VGS − V − VTH ) µ n dV

Massimo Barbaro

13

VDS

0

0

Moltiplicando ambo i membri per dx:

I DS dx = WCOX (VGS − V − VTH ) µ n dV

2

10 Ottobre 2006

ED - Tecnologia CMOS

I D = µ nCOX

I DS ∫ dx = WCOX µ n ∫ (VGS − V − VTH )dV

2

⎡

VDS ⎤

I DS L = WCOX µ n ⎢(VGS − VTH )VDS −

⎥

2 ⎦

⎣

ID =

W

L

2

⎡

VDS ⎤

⎢(VGS − VTn )VDS −

⎥

2 ⎦

⎣

5

I DS = µ nCOX

2

⎡

VDS ⎤

⎢(VGS − VTH )VDS −

⎥

2

⎣

⎦

ED - Tecnologia CMOS

Massimo Barbaro

Equazione in

regione lineare

Contributo della modulazione di

lunghezza di canale

Equazione in regione di saturazione

W

k =µC

L

n

10 Ottobre 2006

14

1

⎛W ⎞

µ nCOX ⎜ ⎟(VGS − VTn )2 [1 + λVDS ]

2

⎝L⎠

Corrente di saturazione

W

L

Massimo Barbaro

NMOS: equazione caratteristica classica

Sapendo che la corrente deve essere costante lungo il canale per il principio di

conservazione della carica, possiamo integrare dx fra 0 e L e dV fra 0 e VDS:

L

dx

dV

dx

MOS: espressione della corrente

4

Mettendo tutto assieme e tenendo conto della formula della velocità, abbiamo:

1

L

3

MOS: espressione della corrente

15

10 Ottobre 2006

n

OX

Rapporto di forma:

unico parametro

modificabile dal progettista

ED - Tecnologia CMOS

Massimo Barbaro

16

NMOS: Regioni di funzionamento

ID =

I D ≈ µ nCOX

W

[(VGS − VTn )VDS ]

L

NMOS: curve caratteristiche classiche

1

⎛W ⎞

µ nCOX ⎜ ⎟(VGS − VTn )2 [1 + λVDS ]

2

⎝L⎠

IDS

Curve caratteristiche di

un NMOS con W/L=1 e

L=10um in tecnologia

90nm

Saturazione

ID

La corrente è positiva quando

scorre dal drain al source

VGS=0.875

Triodo

Pendenza curva I/V molto piccola,

quindi elevata resistenza

VGS=1.000

Saturazione

VGS=0.750

VDS ⎤

W⎡

⎢(VGS − VTn )VDS −

⎥

2 ⎦

L⎣

Le

curve

crescono

all’aumentare di VGS (allo

VGS=0.625

aumentare di VG)

2

I D = µ nCOX

Triodo

Pendenza curva I/V molto grande,

quindi piccola resistenza

L’asse delle ascisse è VDS (quindi

la

corrente

aumenta

allo

aumentare di VD)

VDS

ED - Tecnologia CMOS

Massimo Barbaro

VDS

17

10 Ottobre 2006

PMOS: curve caratteristiche classiche

ISD

La corrente è positiva quando

scorre dal source al drain

VSG=1.000

Curve caratteristiche di

un PMOS con W/L=2 e

L=10um in tecnologia

90nm

Le curve crescono

all’aumentare di VSG (al

diminuire di VG)

L’asse delle ascisse è VSD (quindi

la corrente aumenta al diminuire

di VD)

VGS=0.375

VGS=0.250

VGS-VTn

10 Ottobre 2006

VGS=0.500

Massimo Barbaro

18

MOS: effetti di canale corto

VSG=0.875

VSG=0.750

VSG=0.625

VSG=0.500

ED - Tecnologia CMOS

Le equazioni viste valgono per transistor classici a canale lungo e

sono comunque sufficienti per fare ragionamenti qualitativi sui

circuiti

In realtà, il comportamento di transistor comunemente usati per

realizzare circuiti digitali si discosta pesantemente da quello visto

poiché entrano in gioco effetti del secondo ordine che un tempo

erano trascurabili data la lunghezza del transistor

Per fare ragionamenti quantitativi è necessario avere una maggiore

comprensione del reale funzionamento dei MOS e di quali sono le

vere equazioni che ne descrivono il comportamento

Fra i fenomeni che modificano le equazioni dei MOS digitali (a

canale sub-micrometrico), il più importante è quello della

saturazione della velocità (velocity saturation) ed è quello di cui

dovremo tenere conto per l’analisi quantitativa dei nostri circuiti

VSG=0.375

VSG=0.250

VSD

10 Ottobre 2006

ED - Tecnologia CMOS

Massimo Barbaro

19

10 Ottobre 2006

ED - Tecnologia CMOS

Massimo Barbaro

20

Velocity saturation

vn = µ n E

MOS: espressione della corrente

Le equazioni classiche si basano sull’assunzione che la velocità

dei portatori di carica (elettroni o lacune) sia proporzionale al

campo elettrico orizzontale fra drain e source, attraverso una

costante di proporzionalità denominata mobilità.

vp = µ p E

Rifacendo i conti analitici e tenendo conto della formula della velocità, abbiamo:

I DS = WCOX (VGS − V − VTH )

1

In

realtà la velocità dei portatori, per campi elettrici elevati,

non aumenta linearmente ma viene limitata dagli effetti di

scattering (collisioni) col reticolo del semiconduttore.

1+

La

conseguenza è che la mobilità non è una costante ma

varia col campo elettrico orizzontale (E).

Esiste un valore critico del campo elettrico (EC) oltre il quale la

velocità satura e non aumenta più per ulteriori aumenti del

campo elettrico.

µ n dV dx

vn =

Quindi la dipendenza della velocità dal campo è non lineare

Questo effetto è presente anche nei transistor a canale lungo,

µn E

E

1+

EC

dV

dx

EC

⎛ dV ⎞

dx ⎟ = WC (V − V − V ) µ dV

I DS ⎜1 +

OX

GS

TH

n

⎜

dx

EC ⎟

⎝

⎠

2

solo che in tale caso il campo elettrico orizzontale risulta più

piccolo e non raggiunge il valore critico

10 Ottobre 2006

ED - Tecnologia CMOS

Massimo Barbaro

21

10 Ottobre 2006

MOS: espressione della corrente

L

4

5

I

I DS ∫ dx + DS

EC

0

VDS

∫ dV = WC

OX

0

VDS

µ n ∫ (VGS − V − VTH )dV

0

2

⎡

VDS ⎤

I DS

VDS = WCOX µ n ⎢(VGS − VTH )VDS −

I DS L +

⎥

2 ⎦

EC

⎣

I DS =

10 Ottobre 2006

µ nCOX W ⎡

1+

VDS

LEC

VDS ⎤

⎢(VGS − VTH )VDS −

⎥

2 ⎦

L⎣

ED - Tecnologia CMOS

2

Massimo Barbaro

Massimo Barbaro

22

Velocity saturation: considerazioni

Moltiplicando ambo i membri per dx ed integrando (sapendo che la corrente deve

essere costante lungo il canale per il principio di conservazione della carica):

3

ED - Tecnologia CMOS

23

L’espressione è uguale a quella classica con, in

più, un termine al denominatore

La corrente effettiva è dunque più piccola di

quanto atteso, tanto più piccola quanto più è

grande il termine VDS/L, che fornisce una sorta

di misura del “campo medio” nel canale

Tanto più tale valore si avvicina al valore critico

(quindi maggiore è VDS o minore è L) tanto più il

transistor è affetto dal fenomeno di saturazione

della velocità

10 Ottobre 2006

ED - Tecnologia CMOS

Massimo Barbaro

24

Il transistor MOS: saturazione

MOS: corrente di saturazione

Il primo effetto che si può osservare è che la saturazione del transistor non avviene

più a causa del pinch-off.

Infatti, per tensioni minori della tensione di pinch-off, la velocità dei portatori di carica

satura e raggiunge un valore massimo

La conseguenza quantitativa è che la corrente di saturazione è molto più piccola di

quanto predetto dall’equazione classica ed avviene per tensioni molto più basse

VS=0

-

n+

n+

supponiamo che la saturazione della velocità avvenga bruscamente per un certo

campo critico e che prima del valore critico abbia il valore costante normalmente

utilizzato.

In questo modo l’equazione del transistor in triodo rimane quella classica e cambia

solo l’espressione per la corrente di saturazione, che ricaviamo dall’equazione

classica sostituendo il nuovo valore della tensione di saturazione (che è la tensione per

cui il campo raggiunge il valore critico)

VG>VTH

vsat

Le equazioni reali sono di difficile utilizzo, quindi useremo una semplificazione del

primo ordine che si rileva però molto utile ed efficace per l’analisi dei circuiti digitali:

VD>0

vn

vsat

Approssimazione

con una spezzata

vsat = µ n EC = µ n

Curva reale

Prima ancora che il canale si strozzi gli elettroni

raggiungono la velocità di saturazione e la corrente non

può aumentare pù

VB=0

10 Ottobre 2006

ED - Tecnologia CMOS

Massimo Barbaro

VDSAT =

EC

25

MOS: corrente di saturazione

10 Ottobre 2006

E

ED - Tecnologia CMOS

I DS = µ nCOX

I DS = µ nCOX

VGS=0.875

VGS=0.750

IDS

V

W

⎤

⎡

VDSAT ⎢(VGS − VTH ) − DSAT ⎥

L

2 ⎦

⎣

VGS=0.625

VGS=0.500

La saturazione

tensioni più basse

arriva

per

Massimo Barbaro

27

VGS=0.375

VGS=0.250

La dipendenza dalla VGS è LINEARE anzi che

QUADRATICA

ED - Tecnologia CMOS

26

VGS=1.000

I delta di corrente di saturazione

sono

uguali

quindi

la

dipendenza

dalla

VGS

è

LINEARE

V

⎡

⎤

I DS = k nVDSAT ⎢(VGS − VTH ) − DSAT ⎥

2 ⎦

⎣

10 Ottobre 2006

µn

MOS: caratteristiche a canale corto

2

⎡

VDSAT ⎤

⎢(VGS − VTH )VDSAT −

⎥

2

⎣

⎦

Costanti di processo e progetto

Lvsat

Massimo Barbaro

La corrente di saturazione risulta quindi pari a:

W

L

VDSAT

L

VDS

10 Ottobre 2006

ED - Tecnologia CMOS

Massimo Barbaro

28

Confronto fra canale corto e lungo

MOS: caratteristica IDS/VGS

Canale lungo

Canale

lungo:

QUADRATICA

A parità di W/L

IDS

dipendenza

IDS

Canale corto

Canale

lungo:

LINEARE

dipendenza

VDS

10 Ottobre 2006

ED - Tecnologia CMOS

Massimo Barbaro

VGS

29

10 Ottobre 2006

ED - Tecnologia CMOS

PMOS

⎡

VDSATp

⎢(VSG − VTHp ) −

2

⎢⎣

⎤

⎥

⎥⎦

ED - Tecnologia CMOS

Massimo Barbaro

Per calcoli manuali è possibile, quindi, utilizzare un modello unificato (semplificato) che

dia un’unica espressione valida in tutte le regioni di funzionamento:

VGS − VTH ≤ 0

0

ID =

W

k'

L

2

⎡

Vmin ⎤

⎢(VGS − VTn )Vmin −

⎥

2 ⎦

⎣

Vmin = min(VGS − VTH ,VDS , VDSAT )

Con

Positiva se scorre dal source al drain

10 Ottobre 2006

30

MOS: modello unificato

Nel caso del PMOS vale tutto in modo duale

Le equazioni sono identiche a patto di considerare la

corrente IDS positiva quando scorre dal source al drain

Al posto delle tensioni VDS e VGS bisognerà usare le

tensioni VSD e VSG

Le tensioni di saturazione (VDSATp) e di soglia (VTHp)

sono negative, quindi nella formula se ne prende il

valore assoluto:

I SDp = k p VDSAT

Massimo Barbaro

31

E’ facile verificare che per

VDS<(VGS-VTH,VDSAT)

si ottiene l’espressione in triodo.

Con

VDSAT<(VDS,VGS-VTH)

siamo in regime di saturazione di

velocità

k ' = µCOX

10 Ottobre 2006

VGS − VTH > 0

ED - Tecnologia CMOS

Massimo Barbaro

32

Capacità parassite

Sovrapposizioni (overlap) fra gate/drain e gate/source: danno origine a 2

capacità proporzionali all’area di sovrapposizione

Tecnologia CMOS

n+

n+

Capacità parassite

Capacità di giunzione del

diodo PN (due contributi:

area e perimetro). Le

stesse capacità sono

ovviamente

associate

anche al drain

Università di Cagliari

Dipartimento di Ingegneria Elettrica ed Elettronica

Laboratorio di Elettronica (EOLAB)

10 Ottobre 2006

Layout

ED - Tecnologia CMOS

ED - Tecnologia CMOS

Massimo Barbaro

34

Layout e capacità parassite

Il layout è una vista dall’alto della fetta di silicio

che consente di determinare dove verranno

realizzati i dispositivi

Ad ogni passo di processo è associato un

diverso layer (colore)

Rettangoli appartenenti a diversi layer

rappresentano, ad esempio, dove verranno

realizzati i gate di polisilicio, le diffusioni di drain

e source, le piste di metal e così via

Sul layout è possibile stimare le dimensioni e

quindi le capacità parassite associate

10 Ottobre 2006

Capacità dell’ossido, fra

gate e canale (se esiste il

canale) altrimenti fra gate

e body

Massimo Barbaro

35

W

Area di source

AS=WZ

Poly

Z

Diffusione n+

Si forma un

MOS per ogni

intersezione

fra

poly

e

diffusione

Metallo

L

Contatto

Perimetro di drain

PD=W+2Z

Area di gate

AG=WL

10 Ottobre 2006

(non si computa il lato

che confina col canale)

ED - Tecnologia CMOS

Massimo Barbaro

36

Capacità parassite

Capacità di gate/canale (gate/body)

Tutte le capacità parassite sono non lineari, il

che vuole dire che non sono parametri costanti

del problema ma cambiano al cambiare delle

tensioni in gioco.

In particolare, il valore delle capacità connesse

al gate cambia a seconda della regione di

funzionamento del MOS

Cutoff: non esiste il canale quindi gate e source/drain

sono isolati, tutta la capacità dell’ossido (COXWL) è fra

gate e body

Triodo: si è formato il canale che è omogeneamente

distribuito sotto tutto il gate. Il body è isolato dal gate

dalla presenza del canale, mentre la capacità dell’ossido

si suddivide equamente fra gate/drain e gate/source

ED - Tecnologia CMOS

Massimo Barbaro

37

CGB=0, Cgs=COXWL/2, Cgs=COXWL/2

Saturazione: il canale si strozza quindi non c’è più

capacità fra gate e drain, la capacità dell’ossido solo in

parte si associa al source

10 Ottobre 2006

CGB=COXWL, Cgs=0, Cgd=0

CGB=0, Cgs=2/3 COXWL, Cgd=0

10 Ottobre 2006

Capacità di sovrapposizione (overlap)

Fra gate/drain e gate/source è sempre presente anche

la capacità dovuta alla sovrapposizione (overlap) del

gate di polisilicio con l’area di drain o gate. Tale capacità

è proporzionale alla larghezza del canale.

Le capacità parassite di overlap

sono proporzionali all’area di

sovrapposizione:

10 Ottobre 2006

xd

CgsO=COXxdW=COVW

CgdO=COXxdW=COVW

W

Il parametro xd (quindi COV) è una

costante del processo quindi non

dipende dal progettista

ED - Tecnologia CMOS

Massimo Barbaro

38

La capacità di diffusione (di source e drain) è data da

due contributi: area e perimetro della diffusione. Tali

contributi sono non lineari (variano al variare della

tensione) ma possono essere sostituiti da due capacità

equivalenti costanti (nel range di tensioni di interesse)

L’area di source (drain) è proporzionale a W. Il perimetro

invece viene calcolato senza tenere conto del lato che

confina col canale

39

Massimo Barbaro

Capacità di diffusione

L

ED - Tecnologia CMOS

I valori equivalenti delle due capacità sono dunque

AD=WZ, AS=WZ

PD=W+2Z, PS=W+2Z

CSB=Keq(CJ0AS+CJSW0PS)

CDB= Keq(CJ0AD+CJSW0PD)

I parametri CJ0 e CJSW0 sono costanti di tecnologia, Keq

dipende dal range di tensioni

10 Ottobre 2006

ED - Tecnologia CMOS

Massimo Barbaro

40

Capacità parassite

Capacità parassite

Riassumendo, le capacità parassite di un MOS

sono:

G

COXWL

0

0

COVW

COXWL/2+ COVW

2/3COXWL+ COVW

S

D

CGD

COVW

COXWL/2+ COVW

COVW

CGB

CSB Keq(CJ0AS+CJSW0PS) Keq(CJ0AS+CJSW0PS) Keq(CJ0AS+CJSW0PS)

CDB

CDB Keq(CJ0AD+CJSW0PD) Keq(CJ0AD+CJSW0PD) Keq(CJ0AD+CJSW0PD)

ED - Tecnologia CMOS

Massimo Barbaro

41

Riassumendo

Esistono 2 tipi di transistor (NMOS e PMOS) che hanno

comportamento duale

Per un’analisi del primo ordine lo NMOS (PMOS) è un

interruttore che si apre se la tensione in ingresso al gate

è bassa (alta) e si chiude se è alta (bassa)

L’effetto di saturazione di velocità nei MOS a canale

corto fa sì che:

CGB

CGS

10 Ottobre 2006

Saturazione

CGD

B

Triodo

CGS

CSB

Cutoff

Saturino per tensioni molto più piccole di quanto atteso

La corrente di saturazione dipenda linearmente anzi che

quadraticamente dalla tensione di gate

La presenza di varie capacità parassite limita le

prestazioni dinamiche dei dispositivi

10 Ottobre 2006

ED - Tecnologia CMOS

Massimo Barbaro

43

10 Ottobre 2006

ED - Tecnologia CMOS

Massimo Barbaro

42