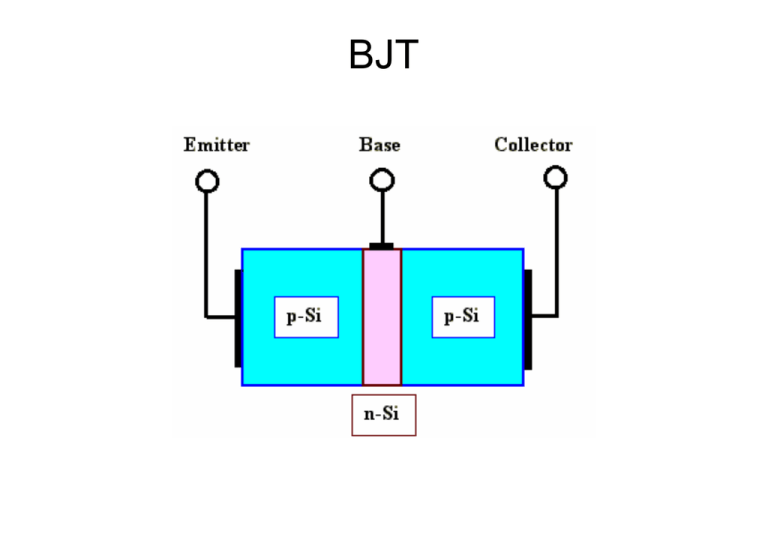

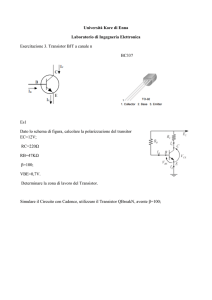

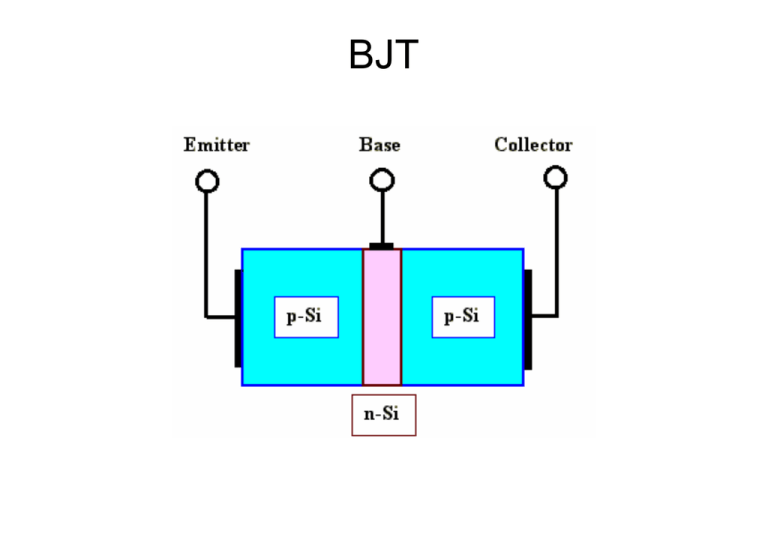

BJT

MOS

Come non fare un circuito integrato

• I transistor non sarebbero isolati. Il substrato di Si con un certo tipo di

drogaggio (o n o p) semplicemente cortocircuita tutte le parti di transistor

con lo stesso genere di drogaggio.

• Non c'è abbastanza spazio per “collegare un filo". Ricordate che la base

deve essere molto stretta ( < 1 µm)?

• Come si fa a disegnare la sequenza di transistor sia npn che pnp in un

pezzo di Si drogato di tipo n o p?

Bisogna lavorare con dimensioni molto piccole nella direzione longitudinale.

Un altro modo che non funziona

Base

Emitter

Pro

• Abbastanza spazio per le connessioni.

• È relativamente facile produrre il drogaggio: Si inizia con un substrato pi

(p.es. con B); si diffonde del P nel Si dove si vuole la Base,

sovracompensando il B. Per fare l'emettitore, si diffonde molto B nel cristallo

e lo si converte di nuovo in p-Si

• L'ampiezza della base può essere molto piccola

Contro

• Ancora nessun isolamento tra i collettori: il substrato è il collettore di tutti i

transistor

Un altro passo avanti…

Collettore

Base

Emitter

Pro

Questo disegno garantisce buone condizioni di isolamento, perché c'è sempre

una congiunzione p-n polarizzata inversamente tra due terminali di transistor

diversi.

Contro

Ora si deve cambiare il substrato n-drogato in un drogaggio di tipo p,

(compensando con B), poi di nuovo convertire il drogaggio in tipo n, ed ancora

una volta in tipo p.

Vediamo un diagramma di profilo di diffusione…

Base

Emettitore

Collettore

Ricordate che il drogaggio deve essere Emettitore > Base > Collettore?

… e i problemi che derivano

Il log della concentrazione è

all’incirca ciò che si dovrebbe avere.

(A parte il fatto che la scala di

profondità nei moderni IC è minore).

Problemi:

• E’ piuttosto difficile produrre

giunzioni con profondità esattamente

determinate.

• Il controllo dell'ampiezza della base non è semplice.

• Non è semplice raggiungere il drogaggio necessario sovra-compensando il

drogaggio esistente tre volte. Se il substrato ha una resistività di 10 W.cm, il

collettore avrà una resistività minore (ha una maggiore concentrazione di

droganti), diciamo 5 W.cm; questo porta la base a circa 1 W.cm e l’emettitore

a circa 0.1 W.cm. Sono valori accettabili, ma vincolano il progetto.

• Ricordate: è il rapporto del drogaggio tra base ed emettitore che fornisce il

fattore di amplificazione!

Come fare un circuito integrato …

• Si inizia con un wafer drogato n (ovviamente è possibile anche partire con

un wafer drogato di tipo p). Si diffonde sopra uno strato p+.

• Sopra al wafer si pone uno strato epitassiale di Si drogato p. Lo strato

epitassiale sarà sempre il collettore del transistor.

• Quindi diffondiamo un anello chiusodi materiale n attorno all’area che

definisce il transistor, in modo che affondi nel wafer. Questo isola il transistor

dai vicini in quanto, indipendentemente dal potenziale applicato, una

giunzione p-n sarà sempre polarizzata inversamente.

• Quindi diffondiamo le regioni di base (n) e di emettitore (p) nell’epi-strato.

… e perché questo funziona

Vantaggi:

• Abbiamo solo due diffusioni "critiche“, dove è importante avere una precisa

concentrazione di drogante.

• Il transistor è nello strato epitassiale dove si ha una qualità decisamente

migliore (in termini di difetti del cristallo, livello e omogeneità del drogaggio,

vita media dei portatori minoritari, ...) che nel substrato di Si.

• Abbiamo a disposizione un livello di connessioni (lo strato p+ layer sotto il

transistor) che si può estendere a qualcos’altro, per esempio al collettore di

un altro transistor!

Monocristallo di Si

Un tipico wafer è fatto di Si di elevata purezza,

cresciuto in forma monocristallina sotto forma di

lingotto (di forma quasi cilindrica) con un diametro

massimo attuale (2006) di 40 cm.

Wafer

I lingotti vengono sezionati in wafer (fette),

attualmente sono di spessore 0.75 mm. Lo

spessore del wafer aumenta all'aumentare del

diametro del lingotto. Da lingotti di 40 cm si

riescono a produrre wafer di 30 cm di diametro.

La superficie del wafer viene sottoposta ad un

trattamento superficiale di planarizzazione e le

due facce vengono rese parallele. La planarità di

un wafer di silicio è tra le massime possibili tra le

superfici lavorate di interesse tecnologico.

wafer di silicio di 10 cm con finitura a specchio

Crescita epitassiale

Per crescita epitassiale si intende la deposizione di

sottili strati di materiale cristallino su un substrato

massivo, anch'esso cristallino, che ne indirizza la

crescita e ne determina le proprietà strutturali. Lo

spessore dello strato epitassiale può variare dalla

frazione di nanometro a centinaia di micron.

L'epitassia può definirsi omoepitassia quando il

materiale epitassiale è lo stesso del substrato

massivo, oppure eteroepitassia, quando il materiale

epitassiale è chimicamente differente dal substrato.

Le connessioni in un IC

Come connettiamo alcuni milioni di transistors (per esempio 50 000 000…) tra

loro e alla alimentazione? E senza che Ie connessioni si tocchino?

Ovviamente bisogna avere le connessioni su diversi piani (è inevitabile che si

incrocino).

Si copre tutto con un isolante (SiO2).

Sopra l’ossido di fanno correre dei “fili”, e dove si vuole connettere il transistor

si fa un foro nello strato di SiO2.

Ogni transistor ha bisogno di tre fori (E-B-C) e presto si presenta il problema

degli incroci.

Metallizzazione multi-level

C’è già un secondo livello nel Si, “nascosto” che abbiamo steso prima della

crescita epitassiale. Può essere utilizzato per collegare i collettori dove ciò ha

senso. (Nota: spesso i collettori sono collegati all’alimentazione)

Questo non è abbastanza: si ripete allora il processo di stesura dell’isolante e di

uno strato metallico, e poi ancora un altro etc…

Si può arrivare a 7 o più strati di connessione (o metallizzazione)

I materiali

Tra gli strati metallici abbiamo bisogno di un isolante.

Si usa molto SiO2; per i chip moderni preferiremmo usare qualcosa di meglio: in

particolare, un materiale con una costante dielettrica ε inferiore (per il SiO2 vale

circa 3.7).

Per il metallo Al viene sostituito da Cu, anche se è molto più costoso. Perchè?

La resistenza totale R di una linea di Al è determinata dalla resistività ρ = 2,7

µΩ.cm dell’Al e dalla geometria della linea. Poiché le dimensioni sono sempre

le più piccole che si può realizzare, siamo legati da ρ. Tra linee vicine, si ha una

capacità parassita C, determinata dalla geometria e dalla costante dielettrica ε

dell’isolante tra le linee.

Assieme queste determinano una costante di tempo R·C, direttamente

proporzionale a ρ·ε. Questa costante di tempo del collegamento cade nella

regione dei ps, e dà un limite superiore assoluto per la propagazione del

signale. In altre parole: il ritardo del segnale in strati di metallizzazione in Al

isolati da strati di SiO2 restringe la frequenza operativa di un IC a circa 1 GHz.

Questo andava bene prima del 1998, perchè I transistor erano comunque più

lenti, ma è un problema al giorno d’oggi (2000 +)!

Quindi bisogna usare materiali con valori di ρ e ε minori. La scelta è limitata;

per il metallo è stato scelto Cu (ρ = 1,7 µΩ.cm); per quanto riguarda il

dielettrico, il SiO2 (ε = 3,7) non è stato ancora rimpiazzato..

Un esempio

Immagini di un chip IBM avanzato con 7 strati di metallizazione, completamente

realizzato in W and Cu. A sinistra: il dielettrico tra gli strati metallici è stato tolto. In

questa scala I transistor non si vedono; si trovano sotto le “interconnessioni locali in

tungsteno” nell’immagine di destra.

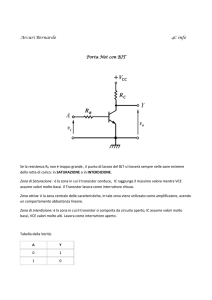

Transistor MOS integrati

I transistors MOS sono completamente differenti dai BJT,

anche nel modo in cui sono integrati.nel substrato di SI.

Abbiamo una regione di source e una di drain nel Si

(drogato differentemente rispetto al substrato) con alcune

connessioni. Tra S e D c’è un sottile gate dielettrico, sul

quale c’è l’elettrodo di gate fatto dello stesso materiale

conduttore che conduce al mondo esterno.

Lo spessore del dielettrico è minore di 10 nm, la

dimensione laterale delle regioni di S, G e D è ben minore

di 1 µm.

Se integriamo diversi transistor MOS,

potrebbe sembrare che li possiamo

mettere nello stesso substrato di Si.

Un problema …

Sembra tutto a posto: i transistor sono

isolati uno dall’altro perchè una delle

giunzioni p-n tra loro è sempre

polarizzata inversamente…

In realtà dobbiamo considerare dei

“transistor parassiti”: se nello spazio

tra i transistor un filo passa sopra lo

strato isolante, può capitare che si trovi in qualche momento ad alto potenziale.

Il D del transistor di sinistra assieme al S del transistor di destra allora formano un

transistor “parassita” avendo lo strato isolante come dielettrico di gate, e il filo che

passa sopra l’isolante come elettrodo di gate. Poichè tutto è piccolo, la tensione di

soglia può essere raggiunta e troviamo un passaggio per la corrente dove non

dovrebbe esserci.

Questo è un aspetto della tecnologia dei circuiti integrato: oltre agli elementi

progettati, è possibile ritrovare transistor, resistenze, capacità e diodi parassiti.

… e la soluzione

La soluzione è rendere la tensione di soglia maggiore di qualunque

voltaggio si possa incontrare nel sistema. Per fare questo si aumenta

localmente la larghezza del dielettrico isolante.

Notiamo l’isolamento addizionale chiamato “ossido di campo”

C’è il problema addizionale che le interfacce e le superfici non sono più piatte.

Questo costituisce uno dei maggiori problemi nell’integrazione su larga-scala!

Notiamo che il Gate è, in linea di principio, un condensatore. La stessa tecnica può

essere quindi utilizzata per realizzare capacità.

I condensatori

Per realizzare grandi capacità (dell’ordine di 50 f F) servono grandi superfici

(diversi µm2) in quanto non possiamo rendere il dielettrico arbitrariamente sottile

(effetti di tunneling, breakdown precoce etc). Serve quindi uno spessore di circa 5

nm of SiO2. Se l’areadel condensatore divanta troppo grande, la scappatoia è la

terza dimensione: si arrotola il condensatore, o in giù nel substrato, o in su negli

strati sopra il Si.

Il condensatore a destra viene chiamato “trench”.

Notiamo, soprattutto, che la tecnologia integrata non è più “planare” ma tridimensionale.

Memorie

Tecnologia CMOS integrata

Configurazione CMOS