00PrPag_HAMACHER_2011 04/12/12 12:01 Pagina VII

Indice

Prefazione

XV

Autori

XX

Ringraziamenti dell’Editore

XXI

Guida alla lettura

XXII

1

Introduzione al calcolatore

1

1.1

Famiglie di calcolatori

1

1.2

Componenti funzionali

1.2.1

Unità di ingresso

1.2.2

Unità di memoria

1.2.3

Unità aritmetica-logica

1.2.4

Unità di uscita

1.2.5

Unità di controllo

2

4

4

5

6

6

1.3

Concetti operativi di base

7

1.4

Rappresentazione dei numeri e operazioni

1.5

1.6

1.7

aritmetiche

1.4.1

Numeri interi

1.4.2

Numeri frazionari

10

10

16

Rappresentazione dei caratteri

17

Approfondimento applicativo 1.1

Codici di controllo e correzione di errore

19

Approfondimento applicativo 1.2

Rappresentazione binaria di informazione multimediale

22

Approfondimento applicativo 1.3

Compressione di dati

24

Considerazioni di efficienza

1.6.1

Tecnologia

1.6.2

Parallelismo

26

26

26

Breve storia del calcolatore

1.7.1

Prima generazione

1.7.2

Seconda generazione

1.7.3

Terza generazione

1.7.4

Quarta generazione

Sommario

Note bibliografiche

27

29

29

30

30

31

31

00PrPag_HAMACHER_2011 04/12/12 12:01 Pagina VIII

VIII Indice

2

Istruzioni macchina

33

2.1

Memoria del calcolatore

2.1.1

Indirizzamento di byte

2.1.2

Ordinamento di byte

Allineamento di parola

2.1.3

2.1.4

Dati numerici e testuali

34

36

36

37

38

2.2

Operazioni di memoria

38

2.3

Istruzioni macchina di base

2.3.1

Trasferimento di registro

2.3.2

Notazione simbolica

2.3.3

Insiemi di istruzioni RISC e CISC

2.3.4

Introduzione agli insiemi di istruzioni RISC

38

39

40

40

41

Approfondimento applicativo 2.1

Architetture di insiemi di istruzioni di processori in commercio: NIOS II,

ColdFire, ARM, IA-32

2.3.5

Esecuzione Sequenziale

2.3.6

Esecuzione con salto

2.3.7

Calcolo di indirizzo

42

44

45

48

Modi di indirizzamento

2.4.1

Costante e variabile

2.4.2

Modo indiretto e puntatore

2.4.3

Modo con indice e vettore

48

49

50

52

Approfondimento applicativo 2.2

Modi di indirizzamento NIOS II, ColdFire, ARM, IA-32

56

Linguaggio assemblativo

2.5.1

Direttive di assemblatore

2.5.2

Assemblaggio ed esecuzione

58

59

62

Approfondimento applicativo 2.3

Direttive di assemblatore e sintassi di GNU Assembler

2.5.3

Notazione per i numeri

63

67

2.6

Gestione di pila

67

2.7

Gestione di sottoprogramma

2.7.1

Annidamento e pila

2.7.2

Passaggio di parametri

2.7.3

Area di attivazione

69

70

71

75

2.8

Altre istruzioni macchina

2.8.1

Istruzioni logiche

80

80

Approfondimento applicativo 2.4

Collegamento di sottoprogrammi, macroistruzioni

2.8.2

Scorrimento e rotazione

2.8.3

Moltiplicazione e divisione

81

83

86

2.9

Trattamento di valori immediati a 32 bit

88

2.10

Insiemi di istruzioni CISC

2.10.1 Altri indirizzamenti

2.10.2 Bit di esito o condizione

89

90

91

2.11

Stili RISC e CISC

93

2.4

2.5

00PrPag_HAMACHER_2011 04/12/12 12:01 Pagina IX

Indice IX

2.12

2.13

3

4

Esempi di programma

2.12.1 Prodotto scalare di vettori

2.12.2 Programma di ricerca di una stringa

94

94

95

Approfondimento applicativo 2.5

Codici operativi e sintassi delle istruzioni

96

Codifica numerica di istruzione

103

Approfondimento applicativo 2.6

Esempi e problemi di programmazione assemblativa

Sommario

Note bibliografiche

104

107

107

Operazioni di ingresso e uscita

109

3.1

Accesso

3.1.1

3.1.2

3.1.3

3.1.4

109

110

111

114

114

3.2

Tecnica di interruzione

116

Approfondimento applicativo 3.1

I/O nei processori NIOS II, ARM, ColdFire e IA-32

3.2.1

Controllo di interruzione

3.2.2

Gestione di dispositivi multipli

3.2.3

Controllo della richiesta

3.2.4

Registri di controllo del processore

3.2.5

Esempi di programmi con interruzioni

3.2.6

Concetto di eccezione

117

122

123

125

126

127

132

Approfondimento applicativo 3.2

I/O con interruzioni NIOS II, ARM, ColdFire, IA-32

134

a dispositivo di I/O

Interfaccia dei dispositivi di I/O

I/O controllati da programma

Un esempio di un programma per I/O in stile RISC

Un esempio di un programma per I/O in stile CISC

Approfondimento applicativo 3.3

Eccezioni nei processori NIOS II, ARM, ColdFire, IA-32

Sommario

139

141

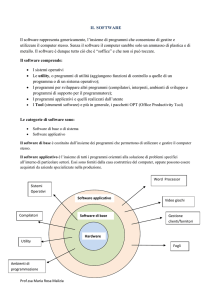

Software

143

4.1

Processo assemblativo

4.1.1

Assemblatore a due passi

143

144

4.2

Caricare ed eseguire programmi oggetto

144

4.3

Il collegatore

145

4.4

Librerie

146

4.5

Il compilatore

4.5.1

Ottimizzazioni del compilatore

4.5.2

Combinare programmi scritti in linguaggi diversi

146

147

147

4.6

Il debugger

147

4.7

Uso di un linguaggio di alto livello per operazioni di I/O

150

4.8

Interazioni tra linguaggio assemblativo e linguaggio C

152

00PrPag_HAMACHER_2011 04/12/12 12:01 Pagina X

X

Indice

4.9

5

6

Sistema operativo

4.9.1

Processo di avvio

4.9.2

Gestione dell’esecuzione di programmi

di applicazioni

4.9.3

Uso delle interruzioni in un sistema operativo

Sommario

Note bibliografiche

157

158

161

161

Struttura di base del processore

163

5.1

Alcuni concetti fondamentali

163

5.2

Esecuzione di istruzioni

5.2.1

Istruzioni di caricamento

5.2.2

Istruzioni aritmetiche e logiche

5.2.3

Istruzioni di immagazzinamento

166

166

167

168

5.3

Componenti hardware

5.3.1

Banco di registri

5.3.2

ALU

5.3.3

Percorso dati

5.3.4

Sezione di prelievo delle istruzioni

169

169

169

171

174

5.4

Prelievo di istruzioni e passi di esecuzione

5.4.1

Salti

5.4.2

In attesa della memoria

176

178

181

5.5

Segnali di controllo

181

5.6

Controllo di tipo cablato

5.6.1

Segnali di controllo del percorso dati

5.6.2

Gestione dei ritardi della memoria

185

186

187

155

156

5.7

Processori in stile CISC

5.7.1

Interconnessione che usa i bus

5.7.2

Controllo microprogrammato

Sommario

187

189

191

193

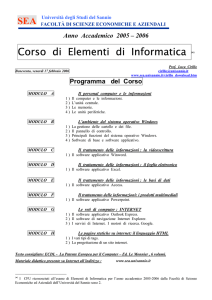

Introduzione al pipelining

195

6.1

Concetti fondamentali

195

6.2

Organizzazione in pipeline

196

6.3

Problematiche del pipelining

198

6.4

Dipendenze di dato

6.4.1

Inoltro di operandi

6.4.2

Gestione in software di dipendenze di dato

198

199

200

6.5

Ritardi della memoria

201

6.6

Ritardi

6.6.1

6.6.2

6.6.3

6.6.4

203

203

204

205

206

6.7

Limiti di risorse

nei salti

Salti incondizionati

Salti condizionati

Il posto del ritardo di salto

Predizione di salti

209

00PrPag_HAMACHER_2011 04/12/12 12:01 Pagina XI

Indice XI

7

8

6.8

Valutazione della prestazione

6.8.1

Effetti di stalli, penalità e cache miss

6.8.2

Numero di stadi della pipeline

210

211

212

6.9

Funzionamento superscalare

6.9.1

Salti e dipendenze di dato

6.9.2

Esecuzione fuori ordine

6.9.3

Completamento dell’esecuzione

6.9.4

Funzionamento dello smistamento

212

214

215

216

217

6.10

Pipeline nei processori CISC

6.10.1 Pipeline nei processori ColdFire

6.10.2 Pipeline nei processori Intel

Sommario

Note bibliografiche

218

219

219

220

220

Sistema di ingresso e uscita

221

7.1

Struttura a bus

221

7.2

Funzionamento del bus

7.2.1

Bus sincrono

7.2.2

Bus asincrono

7.2.3

Considerazioni elettriche

223

223

228

232

7.3

Arbitraggio

232

7.4

Interfacce di I/O

7.4.1

Interfaccia parallela

7.4.2

Interfaccia seriale

234

234

238

7.5

Standard di interconnessione

7.5.1

Bus seriale universale (USB)

7.5.2

FireWire

7.5.3

Bus PCI

7.5.4

Bus SCSI

7.5.5

SATA

7.5.6

SAS

7.5.7

PCI Express

Sommario

Note bibliografiche

242

242

246

247

251

252

253

253

254

254

Sistema di memoria

255

8.1

Concetti fondamentali

255

8.2

Memoria RAM a semiconduttori

8.2.1

Componente di memoria

8.2.2

Memoria statica

8.2.3

Memoria dinamica asincrona

8.2.4

Memoria dinamica sincrona

8.2.5

Banco di memoria

257

258

259

262

265

268

8.3

Memoria a sola lettura

8.3.1

Memoria ROM

8.3.2

Memoria PROM

271

271

272

00PrPag_HAMACHER_2011 04/12/12 12:01 Pagina XII

XII Indice

8.3.3

8.3.4

8.3.5

9

Memoria EPROM

Memoria EEPROM

Memoria flash

273

273

274

8.4

Tecnica di DMA

275

8.5

Gerarchia di memoria

278

8.6

Memoria cache

8.6.1

Schema di indirizzamento

8.6.2

Algoritmo di sostituzione

8.6.3

Esempio di indirizzamento

280

284

289

290

8.7

Considerazioni di prestazione

8.7.1

Guadagno di prestazione

8.7.2

Integrazione con il processore

8.7.3

Altre migliorie

294

295

296

297

8.8

Memoria virtuale

8.8.1

Traduzione di indirizzo

299

300

8.9 Gestione della memoria

306

8.10

Memoria di massa

8.10.1 Disco magnetico

8.10.2 Dischi ottici

8.10.3 Sistemi a nastri magnetici

Sommario

Note bibliografiche

306

307

313

317

318

319

Aritmetica

321

9.1

Addizionatore e sottrattore

9.1.1

Unità logica per addizione e sottrazione

321

323

9.2

Progettazione di addizionatori veloci

9.2.1

Addizione con anticipo del riporto

325

325

9.3

Moltiplicazione di numeri senza segno

9.3.1

Moltiplicatore a matrice

9.3.2

Circuito moltiplicatore sequenziale

329

330

331

9.4

Moltiplicazione di numeri con segno

9.4.1

Algoritmo di Booth

333

333

9.5

Moltiplicazione veloce

9.5.1

Ricodifica bit-pair dei moltiplicatori

9.5.2

Addizione di addendi con salvataggio del riporto

9.5.3

Albero di addizione degli addendi con riduttori 3-2

9.5.4

Albero di addizione degli addendi con riduttori 4-2

9.5.5

Sommario della moltiplicazione veloce

336

336

337

339

341

344

9.6

Divisione di interi

344

9.7

Numeri

9.7.1

9.7.2

9.7.3

347

351

352

354

9.8

Conversione da decimale a binario

e operazioni in virgola mobile

Operazioni Fondamentali

Bit di guardia e troncamento

Realizzazione di operazioni in virgola mobile

356

00PrPag_HAMACHER_2011 04/12/12 12:01 Pagina XIII

Indice XIII

Sommario

Note bibliografiche

10 Sistemi embedded

di sistemi embedded

Forno a microonde

Macchina fotografica digitale

Domotica

357

358

359

10.1

Esempi

10.1.1

10.1.2

10.1.3

10.2

Chip microcontrollori per applicazioni embedded

363

10.3

Un microcontrollore semplice

10.3.1 Interfacce parallele di I/O

10.3.2 Interfaccia di I/O seriale

10.3.3 Contatore/Temporizzatore

10.3.4 Meccanismo di controllo delle interruzioni

10.3.5 Esempi di programmazione

364

365

368

369

371

372

10.4

Cronometro di riflessi, un esempio completo

372

10.5

Sensori

10.5.1

10.5.2

10.5.3

375

375

379

380

10.6

Famiglie di microcontrollori

10.6.1 Microcontrollori basati su processore Intel 8051

10.6.2 Microcontrollori Freescale

10.6.3 Microcontrollori ARM

e attuatori

Sensori

Attuatori

Esempi di applicazione

10.7 Aspetti di progettazione

Sommario

Note bibliografiche

11 Elaborazione parallela e prestazioni

359

360

361

363

381

381

382

382

383

385

386

387

11.1

Multithreading hardware

387

11.2

Elaborazione vettoriale (SIMD)

11.2.1 Unità di elaborazione grafica (GPU)

388

391

11.3

Multiprocessori a memoria condivisa

11.3.1 Reti di interconnessione

391

393

11.4

Coerenza di cache

11.4.1 Protocollo di scrittura immediata

11.4.2 Protocollo di scrittura differita

11.4.3 Cache snoopy

11.4.4 Coerenza di cache basata su directory

396

396

396

397

398

11.5

Multicalcolatori a scambio di messaggi

399

11.6

Programmazione parallela per multiprocessori

399

11.7 Modellazione della prestazione

Sommario

Note bibliografiche

402

403

404

00PrPag_HAMACHER_2011 04/12/12 12:01 Pagina XIV

XIV

Indice

Caso di studio C1 Progetto di un sistema su un chip

405

Caso di studio C2 Architettura Intel IA-32

407

Appendice A Elementi di logica della commutazione

409

A.1

Funzioni logiche fondamentali

409

A.2

Sintesi di funzioni logiche

A.2.1

Sintesi intuitiva

A.2.2

Forma canonica

413

414

416

A.3

Sintesi in forma minima

A.3.1

Metodo di Karnaugh

A.3.2

Condizione di indifferenza

417

421

425

A.4

Sintesi con porte universali

426

A.5

Tecnologia microelettronica

A.5.1

Tecnologia CMOS

A.5.2

Ritardo di propagazione

A.5.3

Vincoli di fan-in e fan-out

A.5.4

Porta tri-state (o in alta impedenza)

A.5.5

Circuito integrato

430

432

438

439

440

441

A.6

Bistabili e flip-flop

A.6.1

Bistabile asincrono

A.6.2

Bistabile sincrono

A.6.3

Flip-flop master-slave

A.6.4

Flip-flop edge-triggered

A.6.5

Flip-flop di tipo T

A.6.6

Flip-flop di tipo JK

A.6.7

Flip-flop con preset e clear

443

443

445

448

449

451

451

453

A.7

Registro seriale-parallelo (ser.-par. register)

453

A.8

Contatore binario (binary counter)

456

A.9

Decodificatore (decoder)

457

A.10

Multiplatore (multiplexer)

458

A.11 Componenti programmabili (FPGA)

Sommario

Note bibliografiche

461

462

463

Indice analitico

I1

Eserciziario

E1