CAPITOLO 3

Questo capitolo presenta l’architettura del processore fuzzy HEPE96 progettato

all’interno del gruppo di ricerca dal dottor Gabrielli e realizzato alla fine del ’96,

con particolare attenzione alle caratteristiche di funzionamento ed ai motivi che

ne hanno portato alla realizzazione. Di questo progetto ho personalmente assistito

alla fase finale di modellazione del layout e alla fase di collaudo del chip con un

ASIC Tester LV500 di proprietà dell’Università di Bologna. Vengono anche date

alcune informazioni preliminari sul chip HEPE97 con particolare riguardo alle

differenze strutturali e funzionali rispetto al processore precedente. Una

descrizione più dettagliata di ogni blocco che compone il chip e di tutti i passi

seguiti durante la fase di progettazione é riportata nel prossimo capitolo.

3.1 Perché un processore fuzzy

Un algoritmo fuzzy progettato per risolvere un particolare problema può essere

implementato su una piattaforma software o hardware. E’ ovvio che

l’implementazione più semplice di un algoritmo é via software attraverso la

stesura di codice in un qualsiasi linguaggio di programmazione che viene fatto

girare su un processore tradizionale. Sebbene questa sia la soluzione più

economica e semplice da implementare può non essere adatta per molti tipi di

applicazioni dove la velocità é un fattore determinante. Per questo motivo un

passo ulteriore consiste nel fare girare questi programmi su coprocessori

progettati esplicitamente per eseguire velocemente le operazioni di un algoritmo

fuzzy, i quali interagiscono con un processore tradizionale che provvede al

salvataggio dei dati prodotti su una memoria esterna. Un esempio famoso di

questo tipo di applicazione é il coprocessore fuzzy WARP 2.0 della SGSThomson.

Se la velocità non é ancora sufficiente occorre utilizzare un processore dedicato

che sia l’effettiva implementazione di tutto l’algoritmo fuzzy in hardware. Dati

gli ingressi da analizzare il chip deve essere in grado di portare avanti tutta

l’elaborazione in base al sistema fuzzy memorizzato in una RAM o ROM interna.

Nel caso di una ROM il sistema fuzzy memorizzato rimane fisso mentre nel caso

di una RAM o di una ROM programmabile (PROM) qualsiasi sistema fuzzy

desiderato dall’utente può essere caricato all’interno.

Una soluzione del genere presenta caratteristiche di maggiore compattezza e

velocità, ma il problema vero sta nel fatto che sul mercato non si trovano

processori di questo tipo. Le applicazioni industriali dei processori fuzzy sono

molto sviluppate e tuttora in continua crescita soprattutto nel campo del controllo

e del riconoscimento di immagini dove il vincolo principale non é la velocità ma

il risparmio. Per applicazioni in cui la velocità é l’obiettivo primario come negli

65

esperimenti di fisica delle alte energie per il riconoscimento on-line di tracce

l’unica soluzione possibile é quella di progettare interamente un chip fuzzy che

possieda tutte le caratteristiche richieste in relazione all’applicazione finale.

Sin dalla prima implementazione di un chip fuzzy veloce che risale al 1986

(Togai e Watanabe) molti ricercatori hanno migliorato le prestazioni hardware

adottando soluzioni di tipo analogico, digitale e misto analogico - digitale. Tutte

queste considerazioni hanno portato il gruppo di ricerca ad iniziare la

progettazione di una famiglia di processori fuzzy molto veloci in grado di

prendere delle decisioni in meno di 1 microsecondo. I prossimi paragrafi

contengono una descrizione dell’architettura del chip HEPE96 e di quali scelte

sono state necessarie per renderlo il più veloce possibile.

3.2 Caratteristiche generali del processore fuzzy

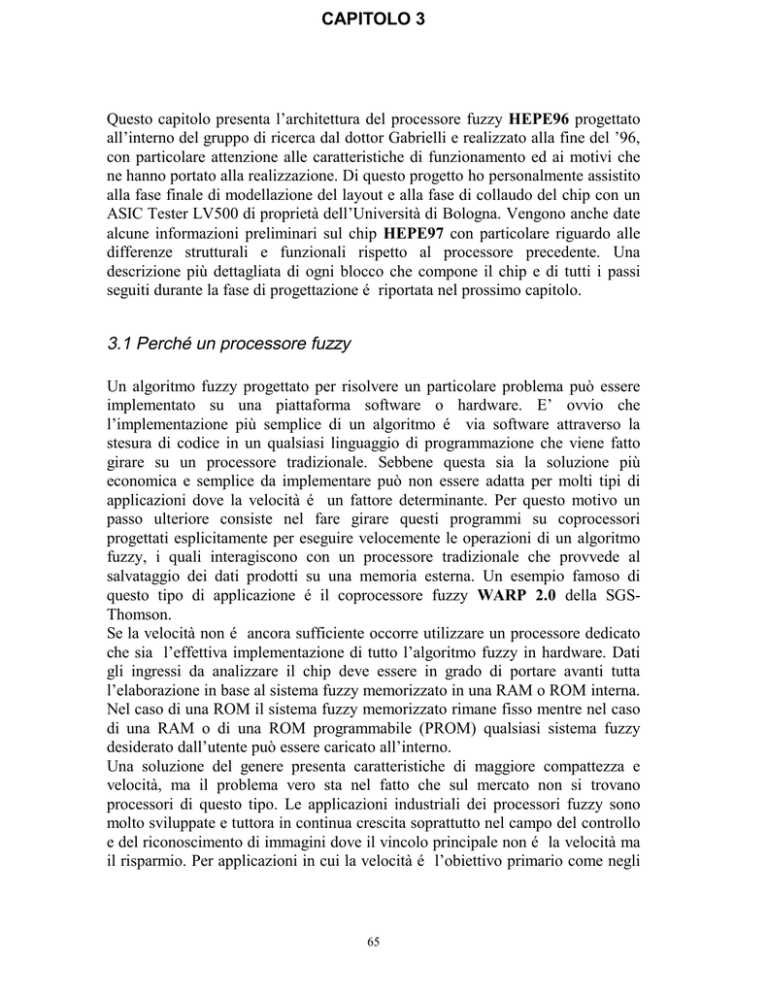

La caratteristica innovativa del chip HEPE96, di cui é riportato uno schema a

blocchi in fig. 3.1, é quella di avere una velocità di elaborazione indipendente

dal sistema fuzzy : infatti poiché nella soluzione adottata ogni sistema fuzzy é

sempre composto da tutte le possibili combinazioni dei fuzzy set degli ingressi, il

numero totale di regole da memorizzare in una memoria interna al processore

(Ramrule) è fisso e dipende dal numero di ingressi e dal numero di fuzzy set per

ogni ingresso.

L’architettura del chip é di tipo pipeline / parallela per incrementare al massimo

le prestazioni : la velocità di elaborazione é di 320 ns quando vengono processati

tutti e quattro gli ingressi qualunque sia il sistema fuzzy memorizzato all’interno,

mentre si possono incrementare ulteriormente le prestazioni utilizzando un

numero minore di ingressi. Il chip é stato realizzato con la tecnologia ES2 0.7

µm CMOS di tipo SPDM (Single Poly Double Metal) : il numero 0.7 µm indica

la larghezza minima del canale di un transistor CMOS che può essere realizzata,

mentre la sigla SPDM indica che i collegamenti fra le celle vengono realizzati

con un singolo strato di polisilicio e con due strati metallici che si trovano a

profondità diverse. L’area del chip é di circa 60 mm2, il numero di piedini usati

é 82 ed il package utilizzato é del tipo JLCC a 84 piedini.

Ecco le caratteristiche più importanti del processore fuzzy :

• da 2 a 4 ingressi codificati come numeri di 7 bit ;

• una uscita a 7 bit ;

• fino a 7 membership function (MF) trapezoidali per ogni ingresso ;

• sovrapposizione consentita, al massimo, di due MF adiacenti ;

• fino a 2401 regole fuzzy ;

• 128 funzioni di appartenenza crisp Zi per l’uscita zeta_out;

• 4 bit per il grado di verità di un antecedente e della premessa di una regola,

chiamati rispettivamente α e θ ;

• metodo di defuzzificazione di Sugeno di ordine 0 ;

• operazione T-norm implementata con il minimo o il prodotto per ottenere il

valore θ ;

66

• velocità di 50 MFLIPS (Mega Fuzzy Logic Inferences Per Second) quando il

processore é pilotato con un clock della frequenza di 50 MHz.

Gli ingressi e l’uscita del processore sono codificati come numeri di 7 bit, cioè i

dati in ingresso al chip sono già digitalizzati : l’opera di conversione del segnale

analogico da portare in ingresso al processore viene effettuata esternamente da un

convertitore A/D molto veloce che si trova sulla scheda madre. Dire che la

risoluzione di un ingresso é di 7 bit significa che l’intervallo di tensioni in cui

può variare il segnale in input viene scomposto in 128 (27=128) parti. Oltre agli

ingressi e all’uscita tutti i segnali interni al processore sono di tipo digitale, cioè

ogni valore numerico calcolato all’interno é espresso come un numero di più bit

X0

X1

X2

X3

M em o ria delle

S elettore di reg ole indirizzo delle

reg ole

rego le attive

attiv e

R am ru le

indirizzo di R am m f

F R P C (4 bit)

R am m f 0

M F gen . 0 α0 D ec 0

R am m f 1

M F gen . 1 α1 D ec 1

R am m f 2

M F gen . 2 α2 D ec 2

R am m f 3

M F gen . 3 α3 D ec 3

R egola (11 bit)

CRC

(7 b it)

M inim o

D efu zzificatore Z out

o

P rodotto

Fig. 3.1: Schema a blocchi del processore fuzzy.

a seconda della risoluzione desiderata. Così il grado di appartenenza α ad una

funzione di appartenenza ed il grado di verità della premessa di una regola θ sono

espressi come variabili di 4 bit.

Inoltre così come la velocità di un processore tradizionale si misura in MIPS

(Mega Instruction Per Second, cioè il numero di milioni di istruzioni elaborate in

un secondo) la velocità di un processore fuzzy si misura in MFLIPS cioè il

numero di milioni di processi di inferenza fuzzy effettuati ogni secondo. Poiché

HEPE96, nella fase di elaborazione vera e propria, esegue un’inferenza fuzzy in

un periodo di clock e quindi in 20 ns, in un secondo vengono effettuate 50

milioni di inferenze logiche.

L’architettura del chip può essere suddivisa logicamente nei seguenti blocchi :

1) il blocco della premessa : contiene le parti di un algoritmo fuzzy che

riguardano la fuzzificazione degli ingressi e l’inferenza. Quattro generatori di

funzioni di appartenenza trapezoidali MF Gen compiono il calcolo di α in base

alla geometria trapezoidale di ogni fuzzy set (contenuta all’interno delle

memorie Rammf) ; quindi in base ai valori assunti gli operatori di minimo e di

67

prodotto producono il valore di θ che viene poi inviato al blocco successivo.

Tutti i calcoli che avvengono all’interno di questo blocco richiedono 10 fasi di

pipeline.

2) la memoria delle regole Ramrule : contiene al suo interno tutte le regole

fuzzy usate per descrivere e risolvere qualsiasi tipo di problema. Come già

menzionato questa memoria è composta da 2401 parole per tenere in

considerazione il caso in cui 4 ingressi contemporaneamente siano elaborati.

3) il blocco della defuzzificazione : esegue le due addizioni Σ(Zi*Θi) e ΣΘi

tramite due sommatori pipelinizzati che lavorano in parallelo. Una volta che

tutte le regole attive, cioè quelle che danno un contributo non nullo, sono state

processate le somme finali sono date in ingresso al divisore che calcola il

valore finale di zeta_out in base alla seguente formula di Sugeno di ordine 0 :

zeta _ out =

(3.1)

∑ Zi * Θi

∑ Θi

La divisione fra le due somme qui sopra é eseguita da un circuito combinatorio

in meno di 80 ns mentre il processore comincia a elaborare un nuovo insieme di

dati. Visto che ogni regola é processata in un periodo di clock e visto che con 4

variabili in ingresso si hanno solo 16 regole attive (come spiegato più sotto) si

ottiene che il tempo totale di elaborazione si compone nel seguente modo :

• il numero di regole attive : 16 x 20 ns = 320 ns

• il numero di fasi di pipeline : 12 x 20 ns = 240 ns ;

• il tempo che occorre per la divisione : 90 ns

per un tempo totale di 650 ns dall’ingresso all’uscita.

3.3 Fase di fuzzificazione : i fuzzy set

Il processo di fuzzificazione consiste nel calcolo del grado di appartenenza α per

ogni variabile di ingresso. Questo valore indica quanto un ingresso appartiene ad

un dato insieme fuzzy mediante un numero compreso fra 0 e 1 : nel nostro caso la

variabile α è rappresentata come un numero di 4 bit.

I quattro ingressi X0, X1, X2, X3, codificati come numeri di 7 bit, entrano nello

stesso istante all’interno del processore. Il blocco Selettore di Regole Attive

seleziona, ingresso per ingresso, gli insiemi fuzzy coinvolti dai valori in ingresso.

Più in particolare nell’ipotesi che la massima sovrapposizione consentita fra

insiemi fuzzy adiacenti sia 2, si ha una situazione quale quella illustrata in fig.

3.2 dove si suppone di avere 7 insiemi fuzzy per ogni variabile. Come si vede in

figura l’ingresso X0 coinvolge i due insiemi Molto Piccolo e Piccolo mentre

l’ingresso X1 coinvolge gli insiemi Piccolo e Quasi Medio : il grado di

appartenenza di X0 e X1 a tutti gli altri gli insiemi è 0. Per questo motivo le

regole che includono gli insiemi fuzzy coinvolti si dicono regole attive ; tutte le

altre regole danno un contributo nullo e perciò possono essere trascurate. Quindi

68

si è dedicata molta attenzione alla progettazione di un circuito per la selezione

delle sole regole attive e cioè il selettore di regole attive : per opera di una serie

di confronti successivi fra i punti d’inizio e di fine di ogni fuzzy set questo

blocco fornisce in uscita i codici dei 2 insiemi fuzzy coinvolti. In base a questi

codici ed ai quattro parametri che caratterizzano ogni insieme trapezoidale i

generatori di membership function devono poi calcolare i due valori di α

corrispondenti ad ogni ingresso. Questi 4 parametri (vedi fig. 3.3) sono il punto

di partenza e di arrivo dei lati obliqui del trapezio e le rispettive pendenze. Nel

prossimo paragrafo viene spiegato dettagliatamente come funzionano i quattro

generatori dei gradi di appartenenza α che si trovano nel processore.

3.4 Generatori di funzioni di appartenenza trapezoidali

I due modi più usati per fuzzificare gli ingressi, cioè per associare un α ad ogni

ingresso X, sono la look-up table ed il generatore di membership function.

P ic c o lo

M ed io

A b b a sta n z a G ra n d e

G ra n d iss im o

M o lto P ic c o lo

G ra n d e

Q u a si M e d io

A b b as tan z a G ran d e

P ic c o lo

M ed io

M o lto P ic c o lo

Q u asi M e d io

G ran d iss im o

G ra n d e

X1

Fig. 3.2: Insiemi fuzzy.

Una look-up table è costituita da uno o più blocchi di memoria indirizzabile in

base al valore assunto dalla variabile di ingresso. In questo modo qualunque

valore assuma l’ingresso X i sette bit che lo codificano vengono messi sul bus di

indirizzi della look-up table e ciò che esce dal bus di dati della memoria sono

proprio i due valori di α corrispondenti. I vantaggi che presenta questo tipo di

soluzione sono la semplicità logica e circuitale, la possibilità di avere insiemi

fuzzy di qualsiasi forma e la velocità totale del processo di fuzzificazione che si

riduce ad un accesso in memoria e quindi ad un solo periodo clock. Per contro

una look-up table di questo tipo occupa un’area molto estesa : nel caso del fuzzy

69

chip con 4 variabili d’ingresso che hanno una risoluzione di 7 bit occorrono 4

blocchi di memoria contenenti ciascuno 128 parole di 8 bit (4 bit + 4 bit per i due

valori di α), il che corrisponde ad una memoria totale di 512 byte. Inoltre

volendo aumentare la risoluzione degli ingressi o degli α le dimensioni della

memoria esploderebbero : occorre quindi trovare una soluzione alternativa. La

soluzione adottata in HEPE96 é un generatore di membership function

trapezoidali : questo circuito approssima una generica funzione di forma

trapezoidale con due linee oblique e tre zone in cui α è fissato o al valore minimo

o massimo (zona alta e zona bassa). E’ ovvio che per definire una forma

trapezoidale sono necessari quattro parametri : come si vede in fig. 3.3 sono stati

scelti il punto di salita A e il punto di discesa B e i due coefficienti angolari dei

lati obliqui K1 e K2. Vediamo più da vicino come

Z o n a alta

15

α

Z o na b a ssa

0

A

K1

K2

A1

B

Z o n a b a ssa

B1

12 7

X

Fig.3.3: Funzione di appartenenza trapezoidale.

funziona il generatore nel caso di variabili d’ingresso di 7 bit e gradi di verità α

di 4 bit. Le due zone denominate zona alta e zona bassa possono essere generate

con dei comparatori digitali. Ogni comparatore verifica se la variabile X

appartiene ad una di queste zone: in caso affermativo il grado di verità α é posto

o a 0 o a 15. Il resto della funzione di appartenenza deve essere generato in

un’altra maniera. Per calcolare α lungo i lati obliqui in base a X deve essere

implementata in hardware una semplice formula di trigonometria piana.

Definiamo le seguenti grandezze in base alla fig. 3.3:

Salita = X - A; Discesa = X - B; K1 = 128 / (A1 - A); K2 = 128 / (B1 - B)

(A1-A) e (B1-B) sono gli intervalli di salita e discesa dei lati obliqui del trapezio:

in base al loro valore sono calcolati i valori K1 e K2 che sono numeri interi

compresi fra 0 e 127. Anche le variabili Salita e Discesa possono variare in tutto

l’universo del discorso di X e quindi sono codificate come variabili a 7 bit.

Usando queste notazioni valgono le seguenti formule:

70

α=(∆Y/(A1-A))*Salita; 8*α=8*(∆Y/(A1-A))*Salita; 8*α=(128/(A1-A))*Salita;

α = (K1 * Salita)/8

8*α=K1*Salita

(3.3)

Î

In queste formule ∆Y é stato posto uguale a 16 anche se il suo valore corretto

sarebbe 15 ma, poiché 15 / (A1-A) non é un numero intero e dovrebbe quindi

essere arrotondato, l’approssimazione fatta é ragionevole. Stesso discorso va fatto

per il numero 127 che é stato rimpiazzato con 128. Tutte le formule sopra

possono essere applicate anche per il lato discendente sostituendo le opportune

variabili ma si può notare che i valori di α relativi al lato discendente sono uguali

al complemento a 1 degli α corrispondenti ad una retta dalla pendenza opposta.

Grazie a questa osservazione le due rette possono essere generate con lo stesso

hardware riducendo di molto l’area globale effettivamente necessaria.

In questo modo, con la scelta operata dei 4 parametri che definiscono la forma

trapezoidale, il calcolo di α si riduce ad una moltiplicazione fra due numeri di 7

bit e ad una divisione per il numero 8 che viene effettuata tramite un semplice

troncamento delle ultime 3 cifre. Tutto questo ragionamento é stato ideato

appositamente per evitare un’operazione di divisione fra numeri diversi da

potenze di 2 in quanto una divisione in hardware é un processo che impiega

molto tempo rispetto alle altre operazioni. Il generatore di membership function

che si trova sul processore ha un’area di circa 2 mm2 e funziona correttamente

con un clock di 50 MHz grazie ad una struttura di tipo pipeline.

3.5 Organizzazione della memoria delle regole

Oltre alla codifica in hardware degli insieme fuzzy occorre porre particolare

attenzione alla gestione delle regole del sistema fuzzy. Appare evidente fin

dall’inizio che occorre un altro blocco di memoria RAM (che d’ora in poi sarà

chiamata memoria delle regole) per memorizzare tutte le regole fuzzy, il

problema che si pone ora sta nel come organizzare la memoria. Se ad esempio

una regola fuzzy é strutturata nel seguente modo :

se (X0 é Piccolo) e (X1 é Medio) allora (Z é Grande)

e gli insiemi fuzzy Piccolo, Medio e Grande sono codificati rispettivamente con i

bit 00, 01 e 10 un modo per esprimere la regola può essere il seguente : 00-01-10.

Inoltre può succedere che una variabile d’ingresso non sia presente in una regola,

é perciò necessario utilizzare un codice adatto che tenga conto della sua

esclusione, in questo caso é naturale scegliere 00.

Il numero totale di regole di un sistema fuzzy dipende dal numero di ingressi N e

dal numero K di fuzzy set associati ad ogni ingresso. Poiché gli ingressi possono

variare ovunque nei rispettivi domini si possono avere tante regole quante sono le

possibili combinazioni di N gruppi di K elementi a N a N. In questo modo il

numero totale di regole é dato da KN che, a seconda dei valori di K e di N, può

71

essere un numero decisamente alto. Nel nostro caso avendo 4 ingressi con 7

membership function ciascuno il numero complessivo di regole é 74=2401.

Quindi il numero totale di regole che devono essere memorizzate internamente al

chip é di 2401 in modo da tenere conto di un sistema fuzzy completo, cioè un

sistema fuzzy dove tutte le regole possibili sono presenti. Ciononostante dato

l’insieme dei valori d’ingresso X0, X1, X2, X3 il numero di regole attive, cioè le

regole che danno un contributo non nullo in uscita, é una frazione molto piccola

rispetto al totale. Sotto la condizione di una sovrapposizione massima fra fuzzy

set adiacenti di due il numero di regole che possono dare una uscita non nulla si

riduce da KN a 2N. Nel nostro caso quindi la selezione delle regole attive riduce il

peso computazionale del processore dal dovere analizzare 2401 regole fino a sole

16 (=24). Il tempo dovuto all’inferenza fuzzy di ogni insieme di valori in ingresso

si riduce quindi a 320 ns, cioè a 16 cicli di 20 ns ciascuno.

Il modo più efficace per riempire la memoria delle regole é quello di inserire le

regole negli indirizzi successivi di memoria in maniera ordinata : per esempio la

prima regola fuzzy (che si trova all’indirizzo 1) é quella riguardante tutti i primi

insiemi fuzzy mentre l’ultima riguarda tutti gli ultimi insiemi fuzzy. La memoria

delle regole potrebbe quindi essere ordinata in questo modo :

PRIMA REGOLA (indirizzo 1):

se(X0 é MF0) e (X1 é MF 0) e (X2 é MF0) e (X3 é MF0) allora (Z é MF1)

SECONDA REGOLA (indirizzo 2):

se(X0 é MF1) e (X1 é MF 0) e (X2 é MF0) e (X3 é MF0) allora (Z é MF2)

...............

ULTIMA REGOLA (indirizzo 2401):

se(X0 é MF6) e (X1 é MF 6) e (X2 é MF6) e (X3 é MF6) allora (Z é MF2401)

In questo modo dato l’indirizzo é già noto a priori, a parte l’uscita Z, quale regola

fuzzy si stia considerando : così il codice con cui si individua una regola fuzzy

non deve essere memorizzato in quanto é già compreso nell’indirizzo. L’indirizzo

di ogni regola attiva viene generato dal selettore di regole attive che mette

insieme i 3 bit dei fuzzy set coinvolti per ogni variabile dando luogo ad un

α

15

0

127

I

II

III

72

IV

V

Fig. 3.4: I cinque punti necessari al selettore di regole attive.

indirizzo a 12 bit che definisce in maniera univoca quale fra le 2401 regole

andare a leggere. Nella parola di memoria vanno quindi memorizzati solamente il

CRC (il Consequent Rule Code, cioé il valore Z della MF di uscita) ed il codice

FRPC (il Fuzzy Rule Premise Code) il quale tiene conto della presenza o meno

della regola fuzzy nel sistema fuzzy iniziale (prima di essere convertito via

software in un sistema fuzzy completo). Il seguente esempio può chiarire le idee :

se l’FRPC vale 0110 ciò significa che la regola fuzzy deriva da una regola

originale dove solo gli ingressi X1 e X2 erano presenti e cioè i valori di X0 e X3

erano ininfluenti. Se l’FRPC vale 0000 ciò vuole dire che non esiste nessuna

regola corrispondente nel sistema fuzzy originario e quindi il suo contributo deve

essere nullo.

In questo modo la memoria delle regole del processore risulta composta di 2401

parole da 11 bit. Infatti quattro bit sono usati per il codice FRPC, un bit per

ognuno degli ingressi, ed i rimanenti sette bit sono usati per il conseguente Z

della regola (CRC) che individua uno fra i 128 fuzzy set della variabile d’uscita

zeta_out. La memoria che ne risulta é molto grande e per questo motivo,

soprattutto per diminuire il tempo di accesso e la dissipazione, é stata divisa in 5

blocchi di memoria separati, 4 blocchi contenenti 512 parole da 11 bit ciascuno

ed un blocco di 353 parole.

3.6 Funzionamento del processore

Vediamo come scorre il flusso di dati all’interno del processore durante la fase di

running vera e propria, cioè una volta che il sistema fuzzy é stato memorizzato

all’interno. Non appena l’insieme di ingressi X0, X1, X2, X3 entra nel

processore il primo blocco interessato é il selettore di regole attive, che

identifica i fuzzy set interessati per ognuna delle 4 variabili. Per poter svolgere

questo compito il selettore contiene al suo interno una serie di registri dove sono

stati memorizzati 5 punti per ogni ingresso. Come si vede in fig. 3.4 5 punti sono

sufficienti a distinguere quali siano i due insiemi fuzzy interessati mantenendo

sempre l’ipotesi che al massimo due insiemi adiacenti possano sovrapporsi.

Quindi se il valore reale del dato in ingresso é compreso fra il primo ed il

secondo punto i due insiemi coinvolti sono il secondo ed il terzo, e così via.

Questo blocco esegue tutti i confronti fra il valore dell’ingresso ed i cinque punti

memorizzati fino a trovare il codice del primo dei due insiemi coinvolti : il

secondo codice viene generato banalmente sommando una unità al precedente.

Individuati gli insiemi fuzzy due processi partono in parallelo : il primo é volto a

comporre l’indirizzo di ognuna delle 16 regole attive, il secondo dà il via alla fase

di calcolo degli α attraverso i generatori di membership function. Il primo

processo avviene mettendo insieme i 3 bit di codice di ogni fuzzy set coinvolto

per ogni ingresso fino a formare i 16 indirizzi di 12 bit delle regole attive facendo

tutte le possibili combinazioni; il secondo processo avviene come segue : una

volta determinato il codice di un fuzzy set viene indirizzata la memoria degli

73

insiemi fuzzy Rammf per ricavare i dati della forma dell’insieme (A, K1, B, K2)

in base ai quali il generatore produce il grado di appartenenza α dell’ingresso al

corrispondente insieme. Per ragioni di velocità la natura di questo processo é di

tipo parallelo : per ognuno dei 4 ingressi l’accesso alla memoria Rammf avviene

contemporaneamente, uno per ciascuno dei 4 blocchi in cui é stata suddivisa ; in

più quattro generatori di membership function lavorano in parallelo fino a fornire

in uscita, ad ogni colpo di clock, i valori dei quattro α di ogni regola. Il passo

logico successivo é il processo di inferenza degli α tramite minimo o prodotto

dei 4 valori ottenuti : come visibile sempre in fig. 3.1 questo passo é vincolato al

valore degli FRPC ottenuti dalla lettura delle regole nella Ramrule. Grazie ai 4

blocchi circuitali Dec se una variabile non é presente in una regola fuzzy il

corrispondente grado di verità α viene settato al valore logico ‘1’ cioè 1111 in

binario, in modo tale da non dare alcun contributo alle operazioni di minimo e di

prodotto. In questo modo grazie ad una architettura

Z

( 7 b it)

M o ltip licaz io ne

Θ* Z

11 b it

S o m m a de i prodo tti

ΣΘΖ

N U M 15 b it

Θ

( 4 b it)

S o m m a de i Θ

ΣΘ

DEN

8 b it

D iv iso re

Z eta_ o u t ( 7 bit)

Fig. 3.5: Suddivisione interna del blocco di defuzzificazione.

fortemente parallelizzata e pipelinizzata in uscita dal blocco di inferenza si avrà,

per ogni colpo di clock e per 16 periodi successivi, il grado di verità θ della

premessa di ogni regola attiva e, contemporaneamente, dalla Ramrule il valore Z

dell’uscita di ogni regola. I valori Z e θ che escono in maniera sincrona da questo

blocco del processore vengono poi mandati in ingresso al terzo blocco

fondamentale del chip : il Defuzzificatore. Questo blocco (vedi fig. 3.5) prende in

ingresso i valori Z e θ e ne esegue la moltiplicazione per ottenere il prodotto Z *

θ di 11 bit. Due sommatori che lavorano in parallelo eseguono poi le sommatorie

da 1 a 16 di tutti i prodotti Z * θ (per ottenere il numeratore della formula di

Sugeno) e di tutti i θ (per ottenere il denominatore). Quando anche l’ultima

addizione é stata eseguita può partire in maniera asincrona il processo di

divisione del numeratore e denominatore così ottenuti, mentre quattro nuovi

74

ingressi possono già essere introdotti all’interno del processore. In questo modo

l’inferenza di tutte le regole attive é realizzata attraverso blocchi di tipo pipeline

mentre la divisione finale che dà in uscita il risultato é eseguita in parallelo al

processo di inferenza di un nuovo set di dati : tutto questo é fatto per

incrementare il throughput totale del chip. Le prestazioni ottenute soddisfano

infatti gli obiettivi proposti : ogni 320 ns si può presentare un nuovo set di

ingressi al chip ed ogni 320 ns si ha in uscita un valore utile.

3.7 Fasi di pipeline

L’architettura generale del processore fuzzy é di tipo pipeline come mostrato in

fig. 3.6 dove é visualizzato il flusso di dati all’interno del chip per ogni fase di

pipeline. Come già detto però vi sono varie strutture di tipo pipeline che lavorano

in parallelo: questo perché diversi calcoli devono essere effettuati

contemporaneamente. Ne sono un esempio i due sommatori che si trovano nel

blocco di defuzzificazione. Le 20 fasi di pipeline mostrate in figura sono

costituite da 12 fasi di pipeline vere e proprie e da 8 fasi dovute al numero di

regole attive. Infatti la figura riporta il caso di soli 3 ingressi usati che danno

luogo a 23=8 regole attive. Nel caso di 4 ingressi alle 12 fasi standard vanno

aggiunte 16 fasi dovute alle 16 regole attive per un totale di 28 passi totali.

Dall’istante in cui un nuovo insieme di dati entra nel chip sono necessarie 12 fasi

di pipeline per i processi di fuzzificazione e di inferenza. Più in dettaglio al primo

periodo di clock gli ingressi sono sincronizzati con il segnale di clock interno,

quindi il selettore di regole attive comincia ad esaminare gli insiemi fuzzy

coinvolti. Durante la seconda fase di pipeline é generato il primo indirizzo di

memoria (l’indirizzo della prima regola attiva) mentre durante la terza i 4

parametri degli insiemi trapezoidali sono già pronti per i generatori di

membership function. Questi circuiti impiegano ciascuno 3 fasi di pipeline per il

calcolo di α, dal quarto al sesto periodo di clock. Questo processo avviene mentre

la memoria delle regole Ramrule viene indirizzata e letta ad ogni colpo di clock.

Una volta che i tre α sono pronti devono essere selezionati in base all’FRPC della

regola corrispondente e ciò avviene nella settima fase di pipeline. Quindi i

quattro α (i tre selezionati più un quarto posto ad 1111 per non influenzare il

minimo o il prodotto) sono processati due alla volta fino ad ottenere il valore di

Θ. Il primo Θ é prodotto nella decima fase di pipeline poiché durante l’ottava e la

nona fase sono eseguiti il minimo ed il prodotto mentre nella decima viene scelto

fra i due valori quello desiderato. Il primo prodotto Θ*Z é valido due periodi

successivi durante la dodicesima fase di pipeline. Dopodiché é necessario

aspettare gli 8 periodi di clock dovuti alle 8 regole attive e finalmente sia la

somma ΣΘ*Z che ΣΘ sono completate : a questo punto parte la divisione. Quello

che é realmente interessante in una struttura pipeline di questo tipo é che il

processore a questo punto é in grado di ricevere un nuovo set di dati mentre sta

ancora eseguendo la divisione dei dati precedenti. La fig. 3.6 riporta quanto ora

esposto periodo clock dopo periodo.

75

In un caso come questo il ritardo globale dalla fase di carica degli ingressi al

risultato finale corrispondente é di 480 ns se si usa un clock di 50 MHz : 12 x 20

ns = 240 ns é il tempo dovuto alle vere e proprie fasi di pipeline; 8 x 20 ns = 160

ns é il ritardo dovuto al numero di regole attive; 80 ns é il tempo dovuto alla

divisione. Ciononostante il valore veramente interessante non é questo ma é la

distanza di tempo con cui si possono mandare nuovi ingressi al processore (input

data set rate) che in questo caso é di 160 ns.

C lo c k

L o a d _ In p u t

In g re ssi a sin cro n i

In g re ssi sin c ro n i

In p u t_ R ea d y

In d . d i R a m m f

In d . d i R am ru le

U scita R a m ru le

F RPC e CR C

v a lo ri d i α

αse le zio n ati

v a lo ri d i Θ

ΣΘ

ΣΖ∗Θ

O u tp u t_ R ea d y

Fig. 3.6: Fasi di pipeline

3.8 Generazione del layout del processore

Per raggiungere gli scopi proposti di velocità e basso consumo oltre allo studio di

una architettura logica ottimizzata per l’elaborazione di algoritmi fuzzy occorre

studiare varie soluzioni hardware che permettano di raggiungere il miglior

compromesso fra gli obiettivi da raggiungere. Perciò prima di tutto la memoria

76

Ramrule é stata divisa in cinque blocchi più piccoli, come già descritto, per

ridurre sia il tempo d’accesso sia il consumo. Infatti sapendo quale parte di

memoria dovrà essere letta é possibile abilitare soltanto il blocco di memoria

corrispondente invece che abilitarli tutti. Questa soluzione riduce il consumo

delle memorie ad un quinto del loro valore globale. In altre parole abilitando solo

un blocco di memoria alla volta e lasciando gli altri blocchi in modalità stand-by

la potenza dissipata é molto ridotta in confronto a quella di un unico blocco di

memoria equivalente. Inoltre generalmente più piccolo é il blocco di memoria e

minore risulta il tempo di accesso. Tutte queste considerazioni danno luogo ad

una maggiore area del chip ma ciò può essere accettato in virtù di una maggiore

velocità. In secondo luogo tutte le standard cell che sono state implementate nel

resto del processore fuzzy, dal generatore di membership function al selettore di

regole attive, dal blocco dell’inferenza a quello di defuzzificazione, sono state

divise in quattro blocchi principali in base alla funzione logica per la quale erano

stati progettati. Più in dettaglio i blocchi sono i seguenti :

1) il blocco degli indirizzi che contiene tutti i circuiti per la selezione degli

indirizzi delle memorie compreso pure il selettore degli intervalli ;

2) il blocco dei generatori di α che contiene i 4 generatori MF Gen;

3) il blocco di defuzzificazione che contiene i due sommatori paralleli, il

moltiplicatore 7 x 4 bit ed il divisore finale ;

4) il blocco della logica di controllo che gestisce la sincronizzazione di tutti i

segnali all’interno del processore.

C o ntrollo

M F G en

Indirizzi

D efuzz.

Divise in questo modo tutte le

celle e megacelle del processore

R am m f

possono essere disposte in

maniera razionale all’interno del

chip come si vede in fig. 3.7.

R am rule

Una disposizione di questo tipo

permette poi di tracciare in

R am rule

maniera semplice una struttura

R am rule

ad albero per la pista del clock e

una struttura tipo dita della

R am rule

mano

per

le

piste

di

alimentazione e di massa. Prima

R am rule

però di passare ad una

descrizione delle piste interne

conviene

fare

alcune

osservazioni sull’area occupata

F ig . 3 .7 : G eo m etria d el lay o u t d el ch ip .

da ciascuno dei blocchi ora

descritti. L’area di un blocco circuitale prevista teoricamente in base alla somma

delle aree di tutte le porte logiche e l’area vera e propria del blocco nel layout

hanno due valori molto diversi : ad esempio l’area teorica di un singolo

generatore di membership function é 0.55 mm2, mentre quella effettiva sul

layout é di circa 2 mm2. Questo é un fattore di cui é necessario tenere conto

77

quando si passa dallo schematic al layout : l’area prevista a priori può diventare

due o tre volte più grande. Ad esempio l’area prevista a priori per il chip HEPE96

era di circa 40 mm2 mentre in realtà si é oltrepassato questo valore di un fattore

2/3 fino all’area finale di 60 mm2.

Le memorie RAM occupano tutta la parte sinistra del processore : più in

dettaglio ogni memoria Rammf occupa 0.17 mm2 per un totale di 0.68 mm2. Lo

spazio necessario a queste RAM però é molto maggiore visto che, avendo bus di

dati di ingresso e uscita di 28 bit ciascuno, c’é bisogno di molto spazio per tutte

le piste che si dipartono dalle memorie e vanno alle standard cell. Per quanto

riguarda la memoria delle regole ogni blocco da 512 parole occupa 1.94 mm2

mentre il blocco di 313 occupa 1.59 mm2 per un totale di 9.35 mm2. In confronto

alla Rammf lo spazio fra due blocchi della Ramrule sembra molto minore in

quanto i bus di dati sono più piccoli e la regione su cui si estendono é molto più

vasta. In ogni caso le memorie RAM portano via più spazio di tutte le altre

strutture poste sul chip, ma la loro presenza é necessaria se si vogliono

mantenere i tempi di elaborazione raggiunti. L’altro blocco molto grande del chip

é dato dai 4 generatori di membership function i quali, insieme, occupano 5.5

mm2. Il blocco degli indirizzi compreso il selettore delle regole attive occupa

4.55 mm2, il blocco di defuzzificazione occupa 3.46 mm2. La logica di controllo

che presiede al corretto funzionamento del processore occupa infine circa 4 mm2.

Facendo la somma dei blocchi ora delineati si ottiene un’area di circa 28 mm2. I

rimanenti 32 mm2 sono spartiti nel seguente modo : 12.50 mm2 é l’area dovuta ai

pad mentre i rimanenti 19 mm2 sono riservati ai canali per i bus di alimentazione,

massa, clock, ecc. Questa é la conclusione abbastanza sorprendente che si

deduce da un’analisi quantitativa del layout : circa un terzo dell’area totale é

spesa per i collegamenti mentre un quinto é riservato ai soli pad di I/O.

78

Fig. 3.8: Layout finale del processore fuzzy HEPE96.

La figura 3.8 mostra i dettagli il layout finale del processore come visualizzato da

Cadence mentre la successiva figura 3.9 mostra alcuni particolari molto

interessanti del layout e cioè la disposizione delle piste di alimentazione, della

massa e del clock. Come si vede tutti i cinque piedini di alimentazione sono posti

sulla parte alta del chip e le piste di alimentazione si dipartono dall’alto in basso

con quattro piste diverse come le dita di una mano; nello stesso modo i cinque

piedini di massa sono posti in basso e quattro piste si dipartono verso l’alto

interdigitate rispetto a quelle di VDD. Poiché il clock deve pilotare solo le

standard cell e non anche le memorie vi é un’unica pista del clock larga 15 µm

che parte dall’alto e va in ingresso a tutti i flip-flop tipo D. La fig. 3.10 é una

microfotografia in bianco e nero che mostra l’interno del chip e le microsaldature

che collegano i pad del nucleo ai piedini esterni dell’integrato.

79

Fig. 3.9: Le piste di alimentazione, di massa e del clock nel layout del chip.

Fig. 3.10: Microfotografia del processore fuzzy HEPE96.

80

3.9 Trattamento dei segnali di I/O

Come già spiegato varie volte la velocità del processore in termini di tempo

computazionale é un obiettivo primario : per questo oltre ad ottimizzare

l’architettura e l’hardware é molto importante rendere il chip facile da usare per

quanto riguarda il trattamento dei segnali di ingresso - uscita.

Il processore fuzzy verrà posto su una scheda madre e sincronizzato con un clock

esterno che si trova sulla scheda. La gestione della sincronizzazione dei segnali di

ingresso e uscita non é delegata a device esterni quali controllori o processori

dedicati ma viene gestita interamente dal chip fuzzy tramite alcuni segnali di

controllo appositamente progettati. Ecco una breve descrizione di questi segnali :

• il segnale Input_Ready, sincrono con il clock esterno, viene usato per

abilitare il ciclo di scrittura sul chip da parte di un device esterno che lo

pilota. Questo segnale é un bit di uscita del processore fuzzy che si porta al

livello logico 1 quando il chip é in grado di accettare un nuovo insieme di

dati in ingresso. Quindi Input_Ready si porta a livello logico 0 una volta

avvenuto il fetch degli ingressi, rimane a tale livello per 320 ns finché non é

terminato il processo di inferenza di tutte le 16 regole e poi si porta al livello

logico 1. In questo modo il device esterno può scrivere all’interno del

processore fuzzy, per mezzo di un segnale pilotato dall’esterno Load_Input,

solo quando l’uscita Input_Ready é attivata. Inoltre il device esterno deve

mantenere il nuovo set di dati ed il segnale di Load_Input per almeno due

periodi clock. Grazie a questo artificio il processore fuzzy può riconoscere il

ciclo di scrittura del device esterno e sincronizzare i dati in ingresso con il

clock che pilota tutta la scheda.

• Altri due segnali di uscita chiamati rispettivamente Output_Ready1 e

Output_Ready2 sono stati implementati per abilitare il device esterno a

salvare l’uscita una volta che questa é pronta. Poiché il processore fuzzy può

essere sincronizzato con un clock di 50 MHz e poiché il processo di divisione

può durare fino ad 80 ns questi due segnali sono sincronizzati rispettivamente

tre e cinque periodi dopo l’inizio della divisione. In questo modo se il clock

con cui viene pilotato il chip é di 50 MHz solo l’uscita Output_Ready2 ha

senso in quanto Output_Ready1 é attivato prima che il dato in uscita sia

valido. Se invece la frequenza di clock é inferiore può essere usata anche

l’uscita Output_Ready1. Inoltre questi due segnali possono essere considerati

sia nella fase di salita sia nella fase di discesa in quanto quando sono a livello

logico 0 non sono attivi mentre hanno una transizione di stato quando

diventano attivi. Con tutti questi accorgimenti si é tentato di raggiungere la

gestione della sincronizzazione dei segnali di I/O più flessibile possibile.

Nella fig. 3.11 é mostrata una possibile applicazione del processore fuzzy : il

chip può essere montato su una scheda pilotata direttamente dalla porta parallela

di un qualsiasi PC dal quale chiunque può caricare all’interno del processore un

sistema fuzzy (tramite opportuno software) e farlo lavorare. Il PC carica il primo

81

device esterno 1 con i dati desiderati dall’utente e, fatto ciò, il processore fuzzy

può cominciare a lavorare alla propria velocità.

Fig. 3.11: Implementazione del processore fuzzy su scheda.

3.10 Test del chip HEPE96

Una volta che il chip é stato realizzato dalla fonderia in numero di 20 pezzi

rimane solo una cosa da fare : il test di ogni chip su una scheda apposita. In

pratica grazie ad una apparecchiatura progettata appositamente per testare i

circuiti integrati, un ASIC Tester LV500 della Tektronics, vengono forniti agli

ingressi i valori voluti e vengono studiate le uscite per verificare l’accordo con i

risultati delle simulazioni software.

Il lavoro di test di un chip si compone di due parti : la prima, che é di tipo

pratico, richiede l’allestimento della scheda su cui verrà inserito il chip. Il

processore, che si trova all’interno di un package di tipo JLCC a 84 piedini, viene

inserito all’interno di uno zoccolo a 84 pin. Ognuno di questi pin risulta collegato

attraverso la scheda ad una serie di contatti esterni contraddistinti da una lettera e

un numero. I contatti corrispondenti all’alimentazione e alla massa del chip

vengono collegati esternamente all’alimentazione e alla massa della scheda

mentre il segnale in ingresso a tutti gli altri contatti viene fornito direttamente

dall’ASIC Tester.

La seconda parte consiste nella programmazione del software della macchina in

modo da fornire in ingresso i dati desiderati con i relativi giusti template.

Purtroppo il software che gestisce l’ASIC Tester non é direttamente

interfacciabile con Cadence e quindi occorre scrivere tutti gli ingressi voluti a

mano e ciò può richiedere molto tempo visto che per un efficace test i vettori

d’ingresso sono molti. Ciononostante il Tester é una macchina molto potente che

permette di testare qualsiasi chip fino alla frequenza massima di lavoro di 50

MHz e permette di fornire gli ingressi con il template esatto pensato dal

progettista. Questo vuole dire che se il clock funziona a 50 MHz e cioé con un

82

periodo di 20 ns l’ASIC Tester é in grado di variare gli ingressi all’interno di

questo periodo con una risoluzione di 2 ns.

Per ora sono state effettuate due simulazioni sul processore HEPE96: nella prima

per cominciare con un numero basso di vettori d’ingresso si é usato il chip nella

configurazione a due ingressi mentre nella seconda si é passati alla

configurazione vera e propria di lavoro con 4 ingressi utilizzati. I template

utilizzati sono stati esattamente quelli pensati a priori con Verilog e Veritime ed é

stato interessante iniziare la simulazione del chip partendo da una frequenza di

lavoro bassa (qualche MHz) per poi arrivare un pò alla volta fino alla frequenza

vera e propria di 50 MHz. Con l’ASIC Tester si potrebbe provare anche ad

aumentare la frequenza di lavoro oltre il valore stimato dai simulatori software

per verificare se, nella realtà (e quindi non nel caso peggiore possibile come

sempre stimato da Verilog e Veritime) il chip possa andare ancora più veloce.

Rimane però il problema che il Tester non riesce a fornire gli ingressi con una

frequenza superiore a 50 MHz. Se però si osserva che l’unico ingresso che deve

variare alla frequenza massima é il clock mentre tutti gli altri variano con una

frequenza inferiore (ad esempio gli ingressi X0, X1, X2, X3 variano solo ogni 16

periodi di clock) basta fornire a parte un clock esterno ad una frequenza superiore

per potere testare il funzionamento del chip a questa velocità.

Una volta effettuati i primi test con successo occorre ripetere le stesse operazioni

per tutti i 20 pezzi forniti dalla ES2 per verificare l’assenza di errori di

fabbricazione e fare lavorare ogni singolo chip per diverse ore consecutivamente

per vedere se si surriscalda eccessivamente o no.

I risultati di test del chip HEPE96 sono stati ottimi : tutti e 20 i chip hanno

dimostrato di funzionare correttamente anche dopo ore di lavoro prolungato. Da

questi test sono stati poi desunti i template finali per tutti gli ingressi in ognuna

della fasi di lavoro del chip (carica delle varie memorie, carica dei punti

intervallo, fase di running vera e propria) che saranno poi riportati nel datasheet

funzionale del processore . La fig 3.12 riporta le temporizzazioni degli ingressi

nella fase di carica delle memorie, nella fase di clear e nella fase di running vera

e propria. Il progettista che comincerà la fase di progettazione della scheda madre

su cui dovrà poi lavorare permanentemente il chip non avrà bisogno di sapere

esattamente tutti i dettagli interni ma si accontenterà di conoscere l’esatta

temporizzazione esterna del chip per poi programmare accuratamente la

temporizzazione della scheda che lo pilota.

3.11 Il processore fuzzy HEPE97

Il processore fuzzy HEPE97 ha un’architettura simile a quella di HEPE96 ma si

distingue perché é dotato di 2 ingressi invece che 4 e risulta quindi molto più

piccolo e veloce. Le caratteristiche generali del chip sono riportate in fig. 3.14

insieme ad una vista del layout finale in fig. 3.13. Poiché si hanno due soli

ingressi con al massimo 8 insiemi fuzzy ciascuno le regole fuzzy che dovranno

essere memorizzate in una memoria interna sono soltanto 82 = 64 mentre il

numero di regole attive, con la solita ipotesi di una massima sovrapposizione

83

consentita fra insiemi fuzzy adiacenti di 2, si riduce a 22 = 4. Da questi primi

numeri si possono trarre due considerazioni : poiché devono essere memorizzate

CK

2ns

WE

RE SET

CLOCK

S E T _ R A M [2 :0 ]

12n s

R ESE T

12ns

20ns

X 0 [6 :0 ] X 1 [6 :0 ]

X 2 [6 :0 ] X 3 [6 :0 ]

c y cle = 4 0 n s

M E_LO A D

2 8 ns

c y c le = 4 0 n s

C LO C K

1ns 10ns

O U TPU T_R EA D Y _0

O U TPU T_R EA D Y _1

IN P U T _ R E A D Y

Z E TA O U T [6 :0 ]

O U T P U T D ATA

X 0 [6 :0 ] X 1 [6 :0 ]

X 2 [6 :0 ] X 3 [6 :0 ]

L O A D _ IN P U T

a lm en o 2 p e rio d i d i c lo c k

cy c le = 2 0 n s

Fig. 3.12: Temporizzazione degli ingressi del processore in tutte le fasi.

solo 64 regole la superficie occupata dalla Ramrule sarà molto piccola e di

conseguenza lo sarà anche l’area totale del chip che infatti risulta essere di soli

14 mm2; inoltre poiché si hanno solo 4 regole attive la frequenza con cui si

possono presentare nuovi valori in ingresso scende a soli 4 periodi di clock.

Considerando poi che il chip può essere pilotato con una frequenza massima di

84

62.5 MHz (periodo clock di 16 ns) anche in considerazione del fatto che essendo

molto piccolo le capacità parassite ed i relativi ritardi sono molto ridotti, un

nuovo set di dati può essere preso in ingresso ogni 64 ns e quindi con una

frequenza di 15.6 MHz. Inoltre alla frequenza di lavoro di 62.5 MHz il

processore fuzzy é capace di processare i dati alla notevole velocità di 62.5

MFLIPS, cioé 62.5 milioni di inferenze fuzzy al secondo. Viste queste

caratteristiche innovative di HEPE97 rispetto al processore precedente si é

pensato che fosse importante realizzare a parte anche questo chip nonostante le

sue funzionalità di base fossero già incluse nel precedente.

3.12 Caratteristiche principali di HEPE97

Le carattersitiche principali di HEPE97 sono le seguenti:

• 2 variabili in ingresso X0 e X1 codificate come numeri di 7 bit;

• 8 insiemi fuzzy per ogni ingresso;

• 64 regole totali di cui solo 4 attive;

• 4 bit per i gradi di verità di un antecedente e di una premessa, chiamati

rispettivamente α e θ;

• 2 metodi di inferenza : minimo e prodotto;

• 44 piedini di I/O.

Lo schema a blocchi del processore é riportato in fig. 3.13 : come si vede la

struttura generale é molto simile a quella del processore a 4 ingressi. Infatti la si

può dividere logicamente nelle solite tre parti :

1) blocco di fuzzificazione ed inferenza;

2) blocco della memoria delle regole Ramrule;

3) blocco di defuzzificazione.

La differenza sostanziale rispetto ad HEPE96 sta nella generazione dei valori di

α: in questo progetto infatti il calcolo degli α é affidato ad una doppia look-up

table indirizzata dal contenuto degli ingressi X0 e X1. I questo caso infatti la

memoria mantiene delle dimensioni accettabili, anzi di molto inferiori a quelle di

un generatore aritmetico di membership function: le dimensioni delle look-up

table Rammf_X0 e Rammf_X1 sono di circa 0.5 mm2 ciascuna contro i 2 mm2 di

un generatore aritmetico. Inoltre l’uso di una memoria possiede anche i pregi di

richiedere un unico periodo di clock per la generazione di α e di essere più

flessibile : infatti una look-up table può memorizzare funzioni di appartenenza di

forma qualsiasi (con il limite dato dalla risoluzione di α che é di 4 bit). Per il

resto il funzionamento logico di HEPE97 é molto simile al processore precedente

ed é qui di seguito riassunto.

I due ingressi X0 e X1 entrano contemporaneamente in ingresso al Selettore degli

intervalli e alle memorie Rammf_X0 e Rammf_X1.

Il Selettore degli intervalli seleziona i codici di 3 bit x e x+1 dei due insiemi

fuzzy coinvolti da X0 ed i codici y e y+1 per X1. Combinando a due a due questi

codici con le combinazioni (x,y), (x,y+1), (x+1,y) e (x+1,y+1) si ottengono gli

85

indirizzi a 6 bit delle 4 regole attive che si trovano nella memoria Ramrule. Una

parola di questa memoria é costituita da 9 bit di cui 2 individuano l’FRPC, cioé la

X0

X1

S eletto re

d i in te rva lli

7

R a m m f_ X 0

7

R am m f_ X 1

x 6 b it

x+ 1

y

y+ 1

2

α0

α1

α2

α3

R am ru le

M inim o

o

P ro d otto

b loc c o di d e fu zz ific az ion e ed in fe re nz a

Z

FR PC

Θ∗Ζ

ΣΘ∗Ζ

ΣΘ

D iv iso re

blo c co d i

d efuz zifica zion e

ze ta_ o ut

Fig. 3.13: Schema a blocchi del processore HEPE97.

presenza o meno di entrambe le variabili nella regola originale, e gli altri 7

individuano la funzione di appartenenza Z dell’uscita zeta_out.

Contemporaneamente dalla memoria Rammf_X0 vengono estratti i due valori α0

e α1 corrispondenti ai valori di appartenenza di X0 ai due insiemi fuzzy

interessati e così i valori α2 e α3 per l’ingresso X1. Questi α vengono processati

due alla volta con le combinazioni (α0, α2), (α0, α3), (α1, α2) e (α1, α3) nello

stesso ordine con cui sono stati generati gli indirizzi delle regole corrispondenti

in base al valore del corrispondente FRPC: così se nella prima regola questo

codice vale 01 α0 viene posto ad 1111 per non influenzare le operazioni di

minimo e di prodotto. Così facendo in quattro periodi di clock si avranno il

valore θ e l’uscita corrispondente Z pronti per entrare in ingresso al blocco di

defuzzificazione dove verrà eseguita la solita formula di Sugeno di ordine 0 fino

ad ottenere il valore in uscita zeta_out.

Nel prossimo capitolo viene data una descrizione dettagliata del procedimento da

seguire per passare da una descrizione logica come quella data in questo capitolo

ad una descrizione accurata di ogni blocco fisico che compone il chip fino alla

progettazione del layout finale.

86

Fig. 3.13: Vista del layout finale di HEPE97 (la scala é in µm).

CARATTERISTICHE DI

PROGETTO

Numero di ingressi

2

Fuzzy set per ingresso

<= 8

Numero di uscite

1

ro

N di fuzzy set per uscita

128

ro

N di bit per ingresso

7

ro

N di bit per grado di verità

4

ro

N totale di regole

64

ro

N di regole attive

4

Metodo di inferenza 1

MIN

Metodo di inferenza 2

PROD

Frequenza di clock (MHz)

<= 62.5

Input set rate (ns)

>= 64

CARATTERISTICHE DEL

LAYOUT

Tecnologia usata

0.7 µm

2

Area totale (mm )

14

ro

N di transistor

38000

ro

N di standard cell

3500

ro

N di macrocelle

3

ro

N di pad di I/O

44

Larghezza della pista clock

3 µm

Larghezza della pista VDD

80 µm

Consumo in mA

<= 100

Consumo in mW

<= 430

Package

JLCC

<= 100

Temperatura di lavoro (°C)

Fig. 3.14: Tabella delle caratteristiche del processore a 2 ingressi.

87

88