1

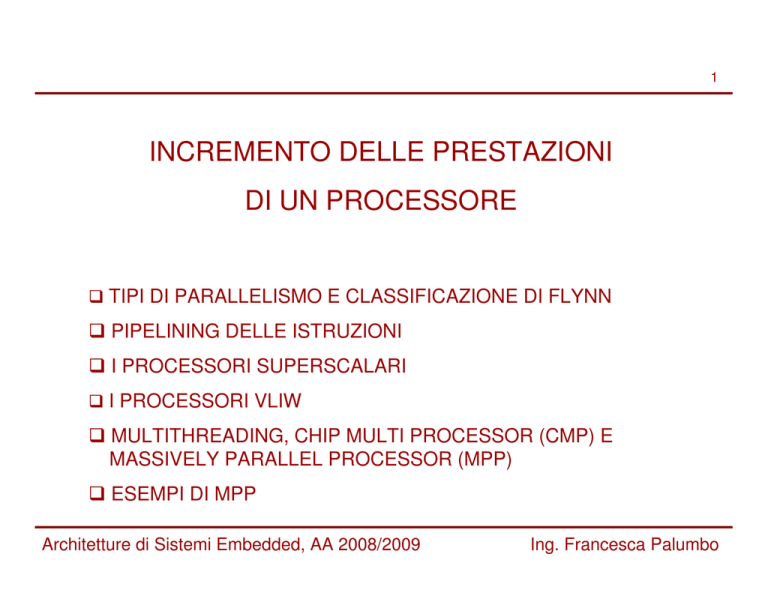

INCREMENTO DELLE PRESTAZIONI

DI UN PROCESSORE

TIPI DI PARALLELISMO E CLASSIFICAZIONE DI FLYNN

PIPELINING DELLE ISTRUZIONI

I PROCESSORI SUPERSCALARI

I PROCESSORI VLIW

MULTITHREADING, CHIP MULTI PROCESSOR (CMP) E

MASSIVELY PARALLEL PROCESSOR (MPP)

ESEMPI DI MPP

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

2

TIPI DI PARALLELISMO E

CLASSIFICAZIONE DI FLYNN

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

MOTIVAZIONI

3

E’ opinione diffusa che il trend che negli ultimi anni ha

portato alla crescita delle frequenze di funzionamento

per le tecnologie CMOS prima o poi dovrà arrestarsi al

raggiungimento dei limiti fisici di tale tecnologia, di

conseguenza al fine di continuare la minimizzazione

dei tempi di esecuzione di un codice su un processore

si dovranno cercare di percorrere altre strade.

Una paradigma progettuale volto a questo scopo è

quello che cerca di adattare l’architettura del

processore alle esigenze di parallelismo che

l’applicazione presenta, al fine di poter minimizzare il

tempo di esecuzione totale svolgendo più task

contemporaneamente.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

OLTRE L’ERA DEI CMOS

4

X-AXIS => More than

Moore: si cercano

nuove possibili strade

anche in termini di

materiali alternativi al

silicio

per

poter

ottenere performance

sempre maggiori.

Y-AXIS => More Moore: si continua a seguire la legge

di Moore secondo la quale il riscalamento delle

tecnologie è tale che ogni due anni raddoppia il

numero di gate integrabili su singolo chip.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

TIPI DI PARALLELISMO

5

PARALLELISMO

A LIVELLO

DI ISTRUZIONE:

throughput elevato,

bassa scalabilità

A LIVELLO

DI DATI:

application specific

Architetture di Sistemi Embedded, AA 2008/2009

A LIVELLO

DI THREAD:

sincronizzazione,

risoluzione delle

interdipendenze

Ing. Francesca Palumbo

TIPI DI PARALLELISMO: ILP

6

Il più comune tipo di parallelismo è il PARALLELISMO A

LIVELLO DI ISTRUZIONE (ILP: Instruction Level Parallelism).

L’ILP prevede l’esecuzione parallela di due o più istruzioni

“vicine” nel codice sequenziale da eseguire. Tali istruzioni

vengono eseguite in unità funzionali separate, omogenee (se

eseguono istruzioni dello stesso tipo) o eterogenee (se

eseguono istruzioni di tipo differente). E’ sfruttabile sia da

microprocessori general purpose che application specific.

Sfruttare il parallelismo a livello di istruzione garantisce al

sistema un throughput più elevato ma non è molto scalabile:

• limitazioni dovute a problemi strutturali (e.g. accesso in

memoria e relativi hazard strutturali);

• limitazioni dovute alla limitata parallelizzazione intrinseca del

codice (e.g. hazard sui dati e di controllo).

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

TIPI DI PARALLELISMO: DLP

7

Il PARALLELISMO A LIVELLO DI DATI (DLP: Data

Level Parallelism) prevede l’esecuzione parallela di

una medesima istruzione in contemporanea su più di

un dato.

E’ immediata la considerazione che un codice capace

di sfruttare un tale tipo di parallelismo è ben lungi

dall’essere un codice di tipo generico. Applicazioni che

si prestano intrinsecamente allo sfruttamento del DLP

sono quelle che hanno a che fare col calcolo vettoriale

(e.g. prodotti scalare per vettore) o col processing di

segnali audio-video (dove la medesima operazione

viene eseguita su uno stream di dati)

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

TIPI DI PARALLELISMO: TLP

(1)

8

Il PARALLELISMO A LIVELLO DI THREAD (TLP:

Thread Level Parallelism) prevede l’esecuzione

contemporanea di diversi blocchi di istruzioni, definiti

appunto thread.

Da non confondersi con il concetto di sistema

multi-threaded tipico dei sistemi operativi, che prevede

la gestione ed esecuzione di un codice su una unica

CPU, sulla quale però i thread non vengono eseguiti

contemporaneamente ma alternativamente attraverso

strategie di scheduling a divisione di tempo.

In questo contesto il TLP è inteso invece come

esecuzione dei thread contemporanea su unità di

esecuzione differenti.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

TIPI DI PARALLELISMO: TLP

(2)

9

Problemi tipici legati allo sfruttamento del TLP sono la

sincronizzazione fra thread e la risoluzione delle

interdipendenze tra di essi.

Il thread A potrebbe necessitare di un dato non ancora

disponibile perché risultato dell’esecuzione del thread

B non ancora iniziato (problema di interdipendenza)

oppure il thread A potrebbe dover modificare dato con

una frequenza più elevata rispetto a quella dei thread

B C e D che condividono tale dato con A (problema di

sincronizzazione).

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

LA CLASSIFICAZIONE DI FLYNN

10

Nel 1966 Michael J. Flynn propose una classificazione dei sistemi

di calcolo basata sulla possibilità di gestire contemporaneamente

diversi flussi di istruzioni e sulla possibilità di far lavorare

contemporaneamente ciascuna istruzione su dati differenti.

CLASSIFICAZIONE

SINGLE

INSTRUCTION

SINGLE

DATA

(SISD)

SINGLE

INSTRUCTION

MULTIPLE

DATA

(SIMD)

MULTIPLE

INSTRUCTION

SINGLE

DATA

(MISD)

Architetture di Sistemi Embedded, AA 2008/2009

MULTIPLE

INSTRUCTION

MULTIPLE

DATA

(MIMD)

Ing. Francesca Palumbo

SISD

11

Le macchine di questo tipo non sfruttano alcuna forma

di parallelismo e rientrano nel paradigma classico di

esecuzione sequenziale delle istruzioni, ove ogni

istruzione è caricata dalla memoria, decodificata, ed

eseguita sui soli dati componenti il proprio set di

operandi.

Il processore MIPS nella versione sequenziale nonpipelined è un esempio di calcolatore SISD.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

SIMD

12

Calcolatori di questo tipo sono in grado di eseguire la

medesima istruzione su un intero set o vettore di dati.

Ovviamente il tipo di parallelismo che viene supportato

è il DLP.

L’unità di controllo è tipicamente centralizzata al fine di

avere N unità sincronizzate operanti in parallelo su N

dati ma rispondenti ad una unica istruzione

memorizzata nel PC. L’approccio funzionale,

relativamente al singolo flusso, è simile all’approccio

usato nelle macchine SISD in quanto ogni unità

funzionale ha i propri registri di indirizzamento dedicati

per poter accedere a dati diversi ed essere in grado di

gestirli.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

MIMD

(1)

13

I calcolatori annoverabili in questa categoria sono

composti da diverse unità computazionali, le quali

possono eseguire flussi di elaborazione diversi su set

di dati diversi. Le varie unità computazionali possono

essere dello stesso tipo (MIMD omogenei) o di tipo

diverso (MIMD eterogenei).

La caratteristica principale di questo tipo di calcolatori

è che sono pensati per essere scalabili: l’hardware è

progettato per essere venduto con un numero di

processori variabile e la scalabilità del software è tale

da permettere ad un calcolatore MIMD di funzionare

anche se il processore i-esimo di N disponibili smette

di farlo.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

MIMD

(2)

14

Calcolatori di questo tipo ben si prestano a sfruttare al

meglio il TLP avendo a disposizione più unità

computazionali sulle quali eseguire in parallelo del

codice, ma ogni unità computazionale poi può a sua

volta sfruttare gli altri tipi di parallelismo per cercare di

migliorare ulteriormente le sue prestazioni intrinseche.

I problemi tipici di questo tipo di architetture sono

legati alla condivisione dei dati (scelta fra memoria

condivisa o memoria distribuita) e al coordinamento fra

i diversi processori.

E’ chiaro che sfruttare il TLP implica anche un

overhead di comunicazione e il dover scegliere

opportunamente fra le infrastrutture di comunicazione

esistenti in letteratura (bus o network on chip).

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

RIASSUMENDO…

Architetture di Sistemi Embedded, AA 2008/2009

15

Ing. Francesca Palumbo

16

PIPELINING DELLE ISTRUZIONI

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

TEMPO MEDIO PER ISTRUZIONE (TMI)

17

Il tempo medio per istruzione (TMI) rappresenta

l’intervallo di tempo medio necessario per l’esecuzione

di una singola istruzione, ed è calcolabile come:

TMI = CPI × CC

dove:

CPI è il Clock Per Instruction: ovvero il numero medio

di cicli di clock necessari per eseguire un’istruzione

CC è il Clock Cycle: ovvero la durata di un colpo di

clock

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

TMI E VALUTAZIONE DELLE PRESTAZIONI

18

Nella seguente tabella è riportata una stima dei fattori che

condizionano il TMI per diverse architetture

CPI=1

CC elevato

CPI è ottimo ma CC è

condizionato dall’esecuzione della

istruzione più lenta (LOAD)

Microarchitettura

CPI=5

Multiciclo (5 cicli per

CC migliore

istruzione)

CPI è condizionato dal numero di

fasi in cui viene scomposta

l’esecuzione dell’istruzione ma il

CC

è

migliore

perché

condizionato dall’esecuzione della

fase più lenta (nel caso migliore

1/5 del precedente)

Microarchitettura a

singolo ciclo

Micoarchitettura

Pipelined

CPI≈1

CC ≈ precedente

Architetture di Sistemi Embedded, AA 2008/2009

CPI ≈1 perché si tende ad avere

un throughput di quasi una

istruzione per colpo di clock e il

CC come nel caso precedente è

condizionato dall’esecuzione della

fase più lenta

Ing. Francesca Palumbo

PIPELINING DELLE ISTRUZIONI

19

In una microarchitettura di tipo pipelined le unità funzionali di

base, necessarie all’esecuzione di una istruzione macchina,

vengono organizzate in “stadi” i quali sono utilizzati in sequenza

al fine di completare una singola esecuzione.

Ogni istruzione ha una latenza di completamento pari al numero

di stadi che deve attraversare per essere terminata ma un

throughput nel caso migliore tendente all’unità.

Le architetture pipelined si pongono l’obiettivo di migliorare le

prestazioni del processore sfruttando l’intrinseco parallelismo

presente in un flusso di istruzioni sequenziale, favorendo

l’overlapping dell’esecuzione di istruzioni differenti a patto che

non siano interdipendenti e/o vogliano sfruttare le stesse unità

funzionali.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

IL CICLO DI ESECUZIONE DELLE ISTRUZIONI NELLE

ARCHITETTURE SEQUENZIALI

20

Nella microarchitettura sequenziale del MIPS in

generale l’esecuzione delle istruzioni è divisibile in 5

fasi:

FETCH-DECODE-EXECUTE-MEMORY-WRITE BACK

Le istruzioni di salto condizionato sono quelle a

latenza inferiore (3 colpi di clock) infatti terminano

nella fase di EXECUTE, quelle di store necessitano di

4 colpi di clock mentre quelle di load e le istruzioni di

tipo logico-aritmetico necessitano di attraversare tutte

le 5 fasi.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

MICROARCHITETTURA NON-PIPELINED - LATENZA

21

Supponiamo di avere una microarchitettura con le

seguenti caratteristiche:

ISTRUZ.

FE.

DEC.

EXE.

MEM.

W.B.

Load

20 ps

5 ps

10 ps

20 ps

5 ps

Store

20 ps

5 ps

10 ps

20 ps

--

Salto

20 ps

5 ps

10 ps

--

--

Aritmetico Logica

20 ps

5 ps

10 ps

--

5 ps

E il seguente codice assembly:

lw $1,100($0)

lw $2,104($0)

Latenza Effettiva:

(2*60+40+55) ps = 215 ps

add $3,$2,$1

sw $3,200($0)

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

MICROARCHITETTURA PIPELINED – LATENZA (1)

22

In una microarchitettura di tipo pipelined, dove gli stadi

di pipe corrispondono esattamente alle fasi di

esecuzione di una istruzione, il flusso di esecuzione

del precedente codice assembly sarebbe il seguente:

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

MICROARCHITETTURA PIPELINED – LATENZA (2)

23

La durata del colpo di clock in una microarchitettura

pipelined corrisponde più o meno alla latenza più

lunga fra le fasi di esecuzione di una istruzione, in

quanto è condizionato dalla sezione di datapath più

critica.

Il codice assembly visto in precedenza viene

processato in 8*20ps=160ps; contro i 215ps calcolati

nel caso non-pipelined.

E’ importante sottolineare che il miglioramento delle

prestazioni di un processore ottenibile tramite il

pipelining delle istruzioni comporta semplicemente

modifiche architetturali, ma è totalmente trasparente al

programmatore.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

LIMITI DELLA AL MIGLIORAMENTO DELLE PRESTAZIONI

OTTENIBILI

(1)

24

La pipeline non aiuta a migliorare la latency intrinseca

della singola istruzione, che rimane di 5 colpi di clock

come nelle microarchitetture sequenziali, ma il

throughput. Quest’ultimo risulta essere limitato dal

tempo di esecuzione della fase più lenta (il clock non è

sceso sotto i 20 ps).

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

LIMITI DELLA AL MIGLIORAMENTO DELLE PRESTAZIONI

OTTENIBILI

(2)

25

Sebbene

l’incremento

potenziale

delle

prestazioni

della

microarchitettura corrisponda al numero di stadi di pipelining introdotti,

il valore di latenza ottenuto non è pari a 215ps/5=43 ps. Per capirne la

ragione bisogna considerare il tempo necessario a riempire e svuotare

la pipe (in questo esempio solo per 2 colpi di clock su 8 la pipe risulta

essere a regime) ed inoltre il fatto che solo nel caso in cui gli stadi di

pipeline fossero identici l’incremento sarebbe esattamente:

SpeedUp =

TimePerInstructionNonPipelined

NumberOfStages

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

LIMITI DELLA AL MIGLIORAMENTO DELLE PRESTAZIONI

OTTENIBILI

(3)

26

In aggiunta a questi limiti c’è da considerare anche

che le prestazioni delle architetture pipelined possono

essere drasticamente ridotte a causa del manifestarsi

di hazards ed eccezioni.

L’effetto degli hazards è quello di interdire l’esecuzione

della prossima istruzione prevista dalla sequenza

nello slot assegnatogli. Conseguenza è che la pipeline

viene stallata, per un numero di colpi di clock tale da

risolvere la condizione critica che ha ingenerato

l’hazard e questo ovviamente peggiora le prestazioni

teoriche ottenibili.

1

SpeedUp =

× PipeDepth

1 + PipeStallCyclesPerInstructions

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

LIMITI DELLA AL MIGLIORAMENTO DELLE PRESTAZIONI

OTTENIBILI

(4)

27

Tipi di hazards:

Hazard Strutturali: si verificano a causa di conflitti

per l’accesso alla medesima unità funzionale, se l’unità

funzionale in questione non è in grado di soddisfare la

combinazione di istruzioni corrente;

Hazard legati ai Dati: l’istruzione corrente dipende

dal risultato della precedente non ancora conclusa;

Hazard legati al Controllo: generati dalla

parallelizzazione di codice contenente salti, condizionati

o meno.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

HAZARD STRUTTURALI

28

Supponiamo che due differenti istruzioni richiedano

nello stesso momento l’accesso ad una stessa risorsa,

le possibili soluzioni sono due:

Il compilatore potrebbe preventivamente occuparsi di

spostare le due istruzioni ad una distanza tale l’una

dall’altra che non si crei conflitto (non sempre

percorribile perché si potrebbe dover modificare l’intero

flusso);

Resource Splitting e/o Resource Replication (eg. Un

processore potrebbe disporre di un register file a una

sola porta di scrittura, ma ci sono situazioni che

richiedono due scritture simultanee e se la porta di

scrittura non viene duplicata si creerebbe un hazard

strutturale).

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

HAZARD LEGATI AI DATI

Esempio:

add

sub

and

or

xor

29

$1,$2,$3;

$4,$1,$5;

$6,$1,$7;

$8,$1,$9;

$10,$1,$11;

Tutte le istruzioni dopo la add utilizzano come operando il suo risultato,

che verrà memorizzato in $1 nello stadio di pipeline equivalente alla

fase di WRITE BACK. Gli operandi però vengono caricati nel register

file nella fase di DECODE e quindi a meno di precauzioni in tal senso

la sub e la and avranno accesso ad un valore non ancora aggiornato.

La soluzione delle dipendenze a livello di dato è diversa a seconda che

si abbia a che fare con “false dipendenze” (e.g. WaW il compilatore si

occupa semplicemente di fare il Renaming dei registri) o “vere

dipendenze” (e.g. RaW, la soluzione va trovata sia a livello hw, per

esempio si usa il data forwarding, che a livello di compilazione tramite il

re-ordering delle istruzioni).

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

HAZARD LEGATI AL CONTROLLO

30

Gli hazard relativi al controllo possono dipendere sia

dai salti condizionati che da quelli incondizionati.

Nel caso incondizionato a parte soluzioni hw basate

sull’anticipo del calcolo dell’indirizzo di destinazione

non si può far molto.

Per quelli condizionati anticipando via hw il calcolo

dell’indirizzo e il test di salto si possono ridurre da 3 a

1 le bubble da inserire e in più si possono anche

utilizzare tecniche di Branch Prediction. Sempre a

livello di compilazione esiste anche un’altra tecnica,

denominata Branch Hoisting, secondo la quale il

compilatore sposta ove possibile l’istruzione di salto

tre istruzioni più in alto.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

DALLA MICROARCHITETTURA SEQUENZIALE A QUELLA

PIPELINED – L’ESEMPIO DEL MIPS

(1)

31

Nel caso del MIPS le 5 fasi di esecuzione delle

istruzioni rispecchiano a pieno la struttura interna del

datapath.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

DALLA MICROARCHITETTURA SEQUENZIALE A QUELLA

PIPELINED – L’ESEMPIO DEL MIPS

(2)

32

Di conseguenza il passaggio alla microarchitettura

pipelined è immediato

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

DALLA MICROARCHITETTURA SEQUENZIALE A QUELLA

PIPELINED – L’ESEMPIO DEL MIPS

(3)

33

Il datapath delle due precedenti microarchitetture è praticamente

lo stesso e questo rende chiaro il motivo per cui il percorso

critico, e di conseguenza la durata del ciclo di clock, nel caso

multiciclo sequenziale e in quello pipelined sia pressoché lo

stesso.

Evidentemente se CC non è cambiato la velocità di accesso alla

memoria nel caso pipelined deve essere proporzionalmente

incrementata.

Il register file viene utilizzato sia nello stadio di DECODE che

nello stadio di WRITE BACK, nel caso peggiore nello stesso

colpo di clock potrebbero essere effettuate due letture e una

scrittura. Per evitare conflitti a livello di dati, il register file è

progettato in modo da gestire la scrittura nella prima metà del

ciclo di clock e la lettura nella seconda metà.

I valori passati da uno stadio di pipe al successivo vengono

memorizzati in registri temporanei, noti come pipeline registers,

posti fra uno stadio e l’altro.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

DALLA MICROARCHITETTURA SEQUENZIALE A QUELLA

PIPELINED – L’ESEMPIO DEL MIPS

(4)

34

Dal punto di vista del controllo le modifiche da fare

sono diverse, infatti nel caso pipelined non si ha a che

fare con una semplice macchina a stati classica.

I bit di controllo vengono generati una volta per tutte in

funzione dell’opcode durante la fase di DECODE e poi

vengono propagati, colpo di clock per colpo di clock,

da uno stadio di pipe al successivo attraverso i

pipeline registers.

Ogni stadio di pipe per controllare le proprie unità

funzionali sfrutta parte dei bit di controllo e propaga gli

altri senza alterarli.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

35

I PROCESSORI SUPERSCALARI

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

PREMESSA …

36

Nelle architetture scalari e pipelined date diverse

classi di istruzioni (e.g. accesso alla memoria,

operazioni aritmetico/logiche in virgola fissa,

operazioni aritmetiche in virgola mobile) è possibile

distinguere diversi flussi di operazioni.

Da qui l’evoluzione di queste architetture verso CPU in

cui a ogni flusso corrisponde una diversa pipeline, a

valle della lettura e decodifica delle istruzioni.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

REQUISITI

37

In tali architetture è possibile l’implementazione del ILP, a patto di:

• poter effettuare la lettura di più istruzioni simultaneamente, se

possibile, con predizione delle istruzioni di salto condizionato per

effettuare letture oltre l’istruzione di salto;

• poter decodificare più istruzioni simultaneamente disponendo di un di

controllo in grado di verificare che non esistano dipendenze sia fra le

istruzioni lette che fra loro e quelle in esecuzione sulle varie pipeline;

• avere dei metodi che consentono di lanciare (issuing) più istruzioni in

parallelo e più unità funzionali di tipo pipelined e gerarchie di memoria

capaci di rispondere contemporaneamente a più riferimenti;

• avere a disposizione dei metodi per comunicare valori di dati

mediante istruzioni load e store e interfacce di memoria che

consentano di gestire prestazioni a volte imprevedibili delle gerarchie

di memoria

• disporre di un eventuale logica di riordino delle istruzioni (commitment

in ordine delle istruzioni) nel caso di flussi a latenza differente (e

quindi pipeline di lunghezza diversa) per preservare la semantica

originale del codice.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

CARATTERISTICHE

(1)

38

La caratteristica fondamentale delle architetture

superscalari è che l’identificazione del potenziale

parallelismo

e

la

conseguente

gestione

dell’esecuzione delle istruzioni in parallelo non viene

compiuta a tempo di compilazione (come invece

avviene per i processori VLIW) ma dinamicamente a

tempo di esecuzione dall’unità di controllo.

Esattamente come nel caso delle architetture pipelined

l’implementazione dell’ILP in queste architetture è

completamente trasparente al programmatore.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

CARATTERISTICHE

(2)

39

Le prestazioni delle architetture superscalari sono

fortemente dipendenti dal compilatore: nonostante la

gestione dinamica del parallelismo il compilatore ha il

compito di ristrutturare il codice (riordino delle

istruzioni e register renaming) per sfruttare al meglio il

parallelismo intrinseco del programma, in quanto più

unità funzionali debbono essere in grado di operare in

parallelo.

In aggiunta è necessario disporre di una banda di

memoria adeguata per istruzioni e dati per poter

consentire l’esecuzione del programma alla velocità

richiesta.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

CONCETTO GENERALE

40

Il codice oggetto è statico, la sequenza di istruzioni eseguite invece

rappresenta il flusso dinamico. Se le istruzioni, come avviene per i

superscalari sono prelevate in ordine dalla memoria vien da se che

l’esecuzione parallela è semplicemente responsabilità del controllo.

CPI inferiore all’unità – idealmente, se n è il numero di istruzioni

che possono essere simultaneamente lette, decodificate ed

eseguite, si raggiunge CPI =1/n;

La banda della cache (= numero di istruzioni trasferite da cache a

CPU in una sola operazione di lettura) deve essere n.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

GESTIONE HAZARD

41

Gli hazard diventano penalizzanti in questo tipo di architettura,

soprattutto quelli di controllo (meno risolvibili lato compilazione).

Tecniche speculative sono largamente in uso in architetture di

questo tipo: quando si incontra salto si effettua predizione sul

risultato del salto e si legge in modo speculativo l’istruzione che

si prevede sarà eseguita dopo e di conseguenza un nuovo

blocco di istruzioni entra a fare parte della finestra di esecuzione.

Se la predizione era corretta toglierò etichetta di “speculazione”

alle istruzioni lette e potrò aggiornare lo stato della macchina, se

invece era sbagliata devo “tornare indietro” garantendo che lo

stato non sia modificato erroneamente.

Le istruzioni della finestra di esecuzione sono analizzate per

scoprire le dipendenze sui dati prima di iniziare la loro

esecuzione.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

SCHEDULE DI ESECUZIONE PARALLELA

(1)

42

Risolte le dipendenze vere e artificiali, le istruzioni sono avviate

all’esecuzione in parallelo.

L’unità di controllo crea uno schedule di esecuzione parallela

che garantisce il soddisfacimento dei vincoli di dipendenza e

disponibilità di risorse hardware.

Le istruzioni possono terminare in ordine diverso dal

programma:

• causa parallelismo e/o diversa latenza delle varie unità

funzionali

• non posso aggiornare subito il register file e la memoria al

termine di una istruzione

• mantengo in memoria temporanea i risultati (accessibile da

eventuali istruzioni dipendenti) fino alla fase di committing o

retiring dell’istruzione.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

SCHEDULE DI ESECUZIONE PARALLELA

(2)

43

Il fetch include la predizione dei salti e crea il flusso di

istruzioni dinamiche.

Le istruzioni vengono esaminate per identificare se sia

possibile rimuovere le dipendenze artificiali fra i dati

(per es con renaming registri) e avviate alla finestra di

esecuzione.

Nella finestra l’ordine non è più sequenziale, ma legato

alle dipendenze vere e alle risorse hardware

disponibili.

Dopo l’esecuzione è come se le istruzioni venissero

logicamente riordinate mano a mano che possono

essere “committed” e i loro risultati usati per

aggiornare lo stato del processore

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

ARCHITETTURE SUPERSCALARI

(2)

44

Vengono aggiunti da 4 a 7 bit a ogni

istruzione RISC (e.g. la classe di istruzione,

le

risorse

richieste,

il

pre-calcolo

dell’indirizzo obiettivo del salto )

FINESTRA DI ESECUZIONE

(ISSUE WINDOW)

load/store => 5 stadi

aritmetico/logiche in virgola

fissa => 3 stadi

aritmetiche in virgola

mobile => 8 stadi

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

FLUSSO DI ESECUZIONE DELLE ISTRUZIONI

(1)

45

LETTURA ISTRUZIONI

• La predecodica sposta parte del compito di decodifica nella

fase di caricamento dalla RAM (o dalla cache di secondo livello)

alla I-cache; si distinguono alcune istruzioni o classi di

istruzioni per adottare tecniche di speculazione intelligente per i

salti.

• La cache istruzioni è una memoria piccola e veloce che

contiene le istruzioni più recenti.

• Ad ogni ciclo un numero di istruzioni pari, nel caso migliore, a

quelle eseguibili in parallelo vengono lette contemporaneamente.

Alcune architetture superscalari hanno a disposizione anche

dell’hardware dedicato per il branch prediction per consentire la

predizione dell’esito dei salti condizionali ed effettuare letture

oltre l’istruzione di salto.

• Nel “buffer istruzioni” si registra un certo numero di istruzioni

lette; utilizzando questa “riserva” la CPU può continuare il

proprio lavoro anche quando la lettura delle istruzioni è

bloccata (ad esempio, per un trasferimento da cache) o

limitata.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

FLUSSO DI ESECUZIONE DELLE ISTRUZIONI

(2)

46

DECODIFICA ISTRUZIONI

• Durante la decodifica vengono identificate le “vere” dipendenze

(RAW) e risolte le “false” (WAW e WAR).

• La issue window si occupa del dispatching (“distribuzione”)

delle istruzioni verso le unità funzionali opportune.

• Se presenti, le reservation station (stazioni di prenotazione)

sono dei buffer che hanno il compito di conservare operandi e

operazione fino a che l’unità funzionale non è in grado di

eseguirla. Questi buffer che servono a disaccoppiare la fase di

issue e il controllo delle vere dipendenze.

• In assenza di reservation station ad ogni ciclo, le istruzioni nella

“issue window” (che contiene le istruzioni lette e decodificate

ma non ancora lanciate in esecuzione) vengono controllate

riguardo alle dipendenze rispetto a tutte le istruzioni nella

finestra di esecuzione nonché entro la finestra di issue stessa.

Se sono presenti le reservation station invece nessun controllo

viene effettuato e le istruzioni decodificate vengono inviate alle

reservation station.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

FLUSSO DI ESECUZIONE DELLE ISTRUZIONI

(3)

47

DECODIFICA ISTRUZIONI (cont.)

• L’unità di smistamento invia ciascuna istruzione, con gli

operandi, alla reservation station opportuna e inserisce un

riferimento a tale istruzione nel re-order buffer interno alla

“re-order and commit unit”.

• Una istruzione non può essere considerata se non c’è spazio

sia nella reservation station , sia nel re-order buffer

• Lo spazio per mantenere i risultati si esaurisce rapidamente:

i processori hanno registri interni replicati (rename buffers) usati

per memorizzare i risultati in attesa che l’unità di consegna dia il

permesso per scrivere i registri effettivi;

i registri replicati, assegnati dall’unità di decodifica, riducono la

criticità sui registri

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

FLUSSO DI ESECUZIONE DELLE ISTRUZIONI

(4)

48

ESECUZIONE ISTRUZIONI

• Quando una unità funzionale è pronta a ricevere una

nuova istruzione la reservation station associata viene

controllata al fine di trovare una istruzione eleggibile per

l’esecuzione. Se ce ne fossero più di una disponibile si

ricorre a politiche di dispatching per selezionarne una e

inviarla in esecuzione.

• L’esecuzione delle istruzioni ha inizio in parallelo in base

alla disponibilità dei dati e non dell’ordine delle istruzioni

(out of order execution).

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

FLUSSO DI ESECUZIONE DELLE ISTRUZIONI

(5)

49

COMMITMENT

• Una volta completate le istruzioni, i risultati vengono scritti nella

“commit unit”, in modo tale che le istruzioni vengano

logicamente riordinate cosicché lo stato della CPU sia

aggiornato (committment phase) in base all’ordine corretto

delle istruzioni e dall’esterno si abbia sempre la sensazione di

un esecuzione “in ordine”.

• Il fatto che le istruzioni possono terminare in ordine diverso

rispetto a come sarebbero terminate su un processore scalare

o pipelined, a causa del re-ordering iniziale delle istruzioni

operato dal compilatore e/o a causa della diversa latenza delle

varie pipeline poste in parallelo, comporta la non aggiornabilità

immediata del register file e della memoria. Necessità di una

memoria temporanea per i risultati dell’istruzione corrente

(accessibile da eventuali istruzioni dipendenti) fino alla fase di

commitment.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

CRITICITA’

50

Un problema grosso per architetture di questo tipo è quello di

identificare (e ritrovare) uno stato preciso del processore.

Soluzioni:

salvo lo stato della macchina in particolari punti di controllo

(checkpoints) in un history buffer, aggiornato durante

l’esecuzione delle istruzioni. Quando un’istruzione viene

finalizzata si cancella la “storia” che non è più necessaria.

separo lo stato fisico da quello logico; lo stato fisico si

aggiorna non appena l’operazione viene completata, quello

logico viene aggiornato solo in ordine sequenziale, mano a

mano che le varie speculazioni hanno raggiunto la loro

verifica. Si usa il re-order buffer; per finalizzare un’istruzione,

il suo risultato viene tolto dal reorder buffer e portato nel

registro destinazione, liberando spazio nel re-order buffer

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

LIMITAZIONI

51

Più le pipeline dedicate sono profonde e sbilanciate in

termini di latenza le une rispetto alle altre più critico è il

compito del compilatore e maggiori sono le esigenze

di memorizzazione pre-committment dei risultati delle

istruzioni, relativamente alle pipeline a latenza

inferiore.

Le prestazioni delle architetture superscalari così

come quelle pipelined aumentano il throughput di

picco di un processore ma sono comunque limitate da

dipendenze a livello di dati e salti condizionati

esattamente come nel caso delle architetture scalari,

vista la necessità per il processore di dovere attendere

per dipendenze non risolte o un salto non previsto

correttamente.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

52

I PROCESSORI VLIW

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

VLIW

53

VLIW sta per Very Long Instruction Word.

Anche i processori VLIW sfruttano il parallelismo a livello di

istruzione ma, a differenza dei processori superscalari,

sono dotati di CPU a scheduling statico: le istruzioni

eseguibili simultaneamente (in parallelo) sono identificate

dal compilatore e assemblate in pacchetti (istruzioni lunghe

o bundle) che poi sono letti, decodificati ed eseguiti dalla

CPU.

Il vantaggio che questo tipo di approccio introduce risiede

nella considerazione che nei processori superscalari l’unità

controllo occupa il 30-35% dello spazio della CPU; quindi

affidare al compilatore il compito di ottimizzare lo

scheduling delle istruzioni, aiuta a ridurre la complessità

dell’unità di controllo e libera conseguentemente area sul

chip.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

LE ISTRUZIONI

(1)

54

L’istruzione “lunga” viene indicata come “bundle” ed è

proporzionale, in lunghezza, al numero di unità funzionali in

grado di eseguire le operazioni in parallelo.

In una bundle vengono impacchettate insieme più “sillabe”

distinte, che rappresentano le istruzioni macchina

elementari, ognuna con i propri operandi.

Le sillabe sono eseguibili in parallelo, mentre l’ordine di

esecuzione delle bundle è rigorosamente sequenziale.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

LE ISTRUZIONI

(1)

55

Il compilatore vede una “finestra di programma” molto

più grande di quella visibile al hardware di un

processore superscalare, quindi ha più tempo per

analizzarla.

NON ha conoscenza dei singoli eventi dinamici (es.

salti fatti o no) – a volte ha informazioni statistiche.

La selezione delle sillabe che andranno a comporre un

bundle e l’ordine di esecuzione dei bundle vengono

generati in fase di compilazione a partire dal

programma statico, al più basandosi su informazioni

ottenute da profiling del codice precedentemente

ottenute.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

GENERALITA’

56

Ogni bundle viene letto in un solo ciclo di lettura,

quindi la banda disponibile deve essere adeguata

all’ampiezza del bundle. Anche la decodifica viene

operata bunble per bundle in un ciclo. Le singole

sillabe, componenti il bundle, vengono avviate in

parallelo per l’esecuzione ognuna a una unità di

esecuzione (tipicamente pipelined) capace di

eseguirla.

Tutte le unità funzionali possono accedere a un banco

di registri condiviso (che quindi – supponendo che il

bundle contenga n sillabe – dovrà ammettere 2n porte

di lettura e n di scrittura).

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

UN PO’ DI STORIA…

57

Prime VLIW: anni ’80 (mini-supercomputer).

Filosofia adottata poi per elaboratori speciali (DSP –

dedicati all’elaborazione di segnale e immagine).

Oggi usate soprattutto (ma non solo!) per sistemi

embedded, grazie al simultaneo sviluppo delle

tecnologie del silicio e della compilazione ottimizzante.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

SCHEMA A BLOCCHI GENERALE – VLIW A 4 “VIE” (1)

Architetture di Sistemi Embedded, AA 2008/2009

58

Ing. Francesca Palumbo

SCHEMA A BLOCCHI GENERALE – VLIW A 4 “VIE” (2)

59

• 4 “lane” o “vie”, cioè 4 unità funzionali aritmetico/logiche sono

collegate ad un unico register file dotato di 4 porte di scrittura

e 8 di lettura.

• A ogni sillaba viene associata una lane nel datapath della CPU,

lungo il quale la sillaba viene eseguita.

• Ogni lane ha un accesso dedicato al RF.

• Una sola lane ha la possibilità di accedere alla cache dati, il

che significa che in un bundle di 4 sillabe una sola

sillaba potrà essere una operazione di accesso alla memoria.

• Non è detto che se ho una bundle di 4 sillabe si abbiano

esattamente 4 lane, potrebbero essercene di più ma per

qualche ragione non essere sfruttate.

• La BYPASS LOGIC serve a ridurre la latenza visibile di alcune

operazioni, ed è in pratica equivalente alla logica di forwarding

che viene utilizzata dal MIPS pipelined per ridurre il numero di

stalli dovuti alle dipendenze fra dati.

• L’area di interconnessione è elevata.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

SCHEMA DI FUNZIONAMENTO

60

Il compilatore:

• identifica 4 operazioni mutuamente indipendenti, per

comporre le sillabe di un bundle;

• si occupa, ove possibile, di risolvere i conflitti relativi alle

risorse;

• associa ad ogni sillaba una lane, lungo la quale verrà

eseguita (il codice oggetto specifica, non solo quali

operazioni vengono eseguite in un’istruzione lunga, ma

anche su quali unità funzionali sono eseguite).

Conflitti di controllo: in un bundle può essere presente al

più una operazione che modifica il flusso del controllo

dell’esecuzione del programma (e.g. salto condizionato o

no, chiamata a funzione o ritorno da sottoprogramma).

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

I CLUSTER

61

Per poter essere in grado si

supportare efficientemente

applicazioni che presentino

intrinsecamente gradi di

parallelismo superiore, la

CPU viene organizzata in

“cluster”.

Ogni cluster sfrutta un

parallelismo limitato (e.g. 4

lane per cluster), ma nel

complesso

si

possono

ottenere prestazioni migliori.

Esiterà un banco di registri

dedicato per ogni cluster,

ma

è

necessario

dell’hardware aggiuntivo per

gestire la coerenza della

memoria.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

ESEMPIO

(1)

62

VLIW con parallelismo 4, un solo cluster, cinque unità

funzionali:

• FXU1 - compie le operazioni aritmetiche su interi;

• FXU2BR - compie le stesse operazioni di FXU1, oltre

a salti e a salti condizionati;

• FLU1 – unità aritmetica in virgola mobile;

• FLU2 – unità aritmetica in virgola mobile;

• LS - unità di load/store per l’accesso alla memoria

dati

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

ESEMPIO

(2)

63

Codifica assembly elementare:

add r1, r2, r3

sub r4, r2, r5

mul r6, r2, r3

and r1, r4, r1

or r2, r1, r3

add r7, r1, r6

IPOTESI:

• mul latenza 2, tutte le altre istruzioni latenza 1.

• esistono percorsi di forwarding come nella pipeline

MIPS elementare.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

ESEMPIO

(3)

64

SOLUZIONE 1:

tutte le operazioni sono rigorosamente vincolate alla

latenza della più lenta

latenza 2

il miglioramento delle prestazioni è limitato, come anche il

parallelismo estraibile.

Codice VLIW estratto:

add r1, r2, r3

sub r4, r2, r5

mul r6, r2, r3

and r1, r4, r1

or r2, r1, r3

add r7, r1, r6

i1 add r1, r2, r3; sub r4, r2, r5;nop; nop

i2 nop; nop; nop; nop

i3 mul r6, r2, r3; and r1, r4, r1; nop; nop

i4 nop; nop; nop; nop

i5 or r2, r1, r3; add r7, r1, r6; nop; nop

i6 nop; nop; nop; nop

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

ESEMPIO

(4)

65

SOLUZIONE 2:

le operazioni in uno stesso bundle sono vincolate alla

latenza della sillaba più lenta, se tutte le sillabe sono più

veloci, si sfrutta il forwarding in modo da ridurre la latenza

dell’intero bundle, mantenendolo comunque tutto sincrono.

Codice VLIW estratto:

add r1, r2, r3

sub r4, r2, r5

mul r6, r2, r3

and r1, r4, r1

or r2, r1, r3

add r7, r1, r6

i1 add r1, r2, r3; sub r4, r2, r5;nop; nop

i2 mul r6, r2, r3; nop; nop; nop

i4 nop; nop; nop; nop

i3 and r1, r4, r1; nop; nop; nop

i4 or r2, r1, r3; add r7, r1, r6; nop; nop

Il secondo bundle richiede comunque l’introduzione di una

bolla per supportare la latenza della mul.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

PRO E CONTRO

(1)

66

A LIVELLO ARCHITETTURALE:

La microarchitettura di un processore VLIW è più semplice di

una CPU superscalare con uguale parallelismo, e

tendenzialmente si possono raggiungere frequenze di

funzionamento superiori (considerato che il ciclo di clock ora è

determinato dai percorsi critici del datapath e non dall’unità di

controllo che è notevolmente più semplice) .

A LIVELLO DI COMPILAZIONE:

Il compilatore deve avere una conoscenza dei dettagli della

microarchitettura unitamente ad alcuni parametri tecnologici (e.g.

la latenza e throughput delle unità funzionali) al fine di poter

efficientemente comporre i bundle. Questo fatto riduce la

portabilità del codice oggetto anche fra successive generazioni

della stessa famiglia di processori VLIW, in quanto potrebbe

venire a mancare la compatibilità binaria.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

PRO E CONTRO

(2)

67

Per risolvere i problemi di compatibilità binaria una soluzione

diffusa è quella che utilizza i “software binary translation”:

software dedicati per la conversione dinamica, al momento

dell’esecuzione, delle istruzioni appartenenti ad un instruction

set in equivalenti istruzioni dell’instruction set nativo.

Volendo mantenere l’esecuzione in-ordine, non è possibile

ammettere che sillabe diverse di uno stesso bundle giungano al

Write Back in istanti diversi (si potrebbero generare conflitti per

l’accesso al Register File, hazard di tipo WAR e WAW non

risolte dal compilatore…).

Conseguentemente se il parallelismo non è elevato, le istruzioni

contengono un numero elevato di sillabe nop e l’immagine del

programma in memoria tende ad esplodere, anche perché

nonostante le sofisticate tecniche di analisi, generazione di

codice e scheduling utilizzate dai compilatori VLIW, è possibile

che non sempre il compilatore sia in grado di garantire ad ogni

colpo di clock l’utilizzo di ogni unità funzionale.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

PRO E CONTRO

(3)

68

Se l’applicazione non presenta un grado di parallelismo

adeguato a quello messo a disposizione, il numero di NOP

potrebbe risultare elevato, causando un utilizzo poco efficiente

della memoria. Per questo motivo i processori VLIW utilizzano

tecniche di compressione dell’immagine dell’applicazione in

memoria, permettendo di evitare, in fase di compilazione,

l’introduzione di NOP, per poi generarli via hardware durante la

fase di issue delle istruzioni.

Nella pratica in memoria i bundle sono “impaccati” in modo da

contenere solo sillabe significative (nessuna NOP) e dei codici

separatori vengono utilizzati per indicare quali sillabe

appartengono a un bundle e quali al bundle successivo. L’unità

di controllo poi, scompone il bundle “impaccato” nella sequenza

di bundle eseguibili.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

69

MULTITHREADING,

CHIP MULTI PROCESSOR (CMP)

E MASSIVELY PARALLEL PROCESSOR (MPP)

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

MULTITHREADING A GRANA FINE E GRANA GROSSA

70

GRANA FINE:

La CPU commuta da un thread all’altro ad ogni istruzione.

L’esecuzione di diversi thread risulta essere interallacciata

(nel caso di stallo, il thread che dovrebbe essere eseguito

salta il suo turno di esecuzione). La CPU deve essere in

grado di cambiare thread a ogni ciclo di clock, quindi per

evitare inefficienze sono richieste duplicazioni pesanti

dell’hardware disponibile.

GRANA GREZZA:

La CPU commuta da un thread a un altro solo in

corrispondenza di stalli lunghi (e.g. cache miss). I thread in

questione condividono molte risorse del sistema (e.g.

registri architetturali) per questo la commutazione da un

thread all’altro richiede diversi cicli di clock per poter

effettuare il salvataggio del contesto.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

SIMULTANEOUS MULTITHREADING (SMT)

71

L’obiettivo di questa classe di architetture è quello di

utilizzare le risorse messe a disposizione da un processore

superscalare, per sfruttare simultaneamente ILP e TLP.

Il motivo fondamentale risiede nella considerazione che

molto spesso una CPU ha a disposizione più risorse

funzionali di quante un singolo thread possa effettivamente

sfruttare. Unitamente a ciò, grazie alle tecniche di register

renaming e allo scheduling dinamico, è possibile pensare

di eseguire più istruzioni indipendenti sulla stessa CPU.

Se le istruzioni che vengono lanciate in parallelo

appartengono a thread diversi allora si possono anche

limitare le problematiche relative alle dipendenze fra dati.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

RIASSUMENDO …

Architetture di Sistemi Embedded, AA 2008/2009

72

Ing. Francesca Palumbo

CHIP MULTI PROCESSOR (CMP)

(1)

73

I Chip MultiProcessor (CMP) rappresentano un approccio

alternativo a quello dei processori SMT per la gestione del

TLP. In questo caso l’architettura del processore è

composta dalla replicazione di diverse celle di calcolo

identiche connesse poi le une con le altre (tipicamente a

formare una griglia).

La caratteristica fondamentale di queste architetture, da cui

prendono anche il nome, è il fatto che la potenza

computazionale e la conseguente complessità di ogni

elemento della griglia di processori è paragonabile a quella

di una classica architettura superscalare (o VLIW visto che

commercialmente sono più diffusi).

Ogni cella è in grado di eseguire uno o più thread ed

interagirà con le altre mediante un layer di comunicazione

adeguato alle esigenze di banda che una architettura di

questo tipo richiede.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

CHIP MULTI PROCESSOR (CMP)

(2)

74

La differenza fondamentale fra un architettura SMT e

un architettura CMP risiede nel fatto che nei CMP le

diverse unità funzionali sono indipendenti le une dalle

altre e non condividono alcun tipo di logica di

esecuzione delle istruzioni.

Risultato di questa diversità è una maggiore scalabilità

intrinseca di architetture di questo tipo.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

MASSIVELY PARALLEL PROCESSOR (MPP)

75

Nel caso di architetture che prevedano l’integrazione all’interno

dello stesso chip di un numero elevato di celle elementari di

calcolo (in letteratura si parla di almeno 64 unità), il modello

architetturale prende il nome di Massively Parallel Processor

(MPP).

Tipico esempio di MPP sono le architetture di tipo “tyled-based”.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

76

ESEMPI DI MPP

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

TREND COMMERCIALE

Architetture di Sistemi Embedded, AA 2008/2009

77

Ing. Francesca Palumbo

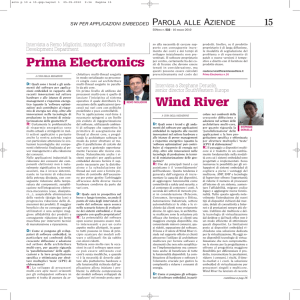

TILERA - TILE64 Processor Block Diagram

A Complete System on a Chip

DDR2

DDR2Memory

MemoryController

Controller00

78

DDR2

DDR2Memory

MemoryController

Controller11

XAUI

XAUI

MAC

MAC

PHY

PHY00

PCIe

PCIe00

MAC

MAC

PHY

PHY

PROCESSOR

CACHE

L2 CACHE

Reg File

P2

P1

P0

Serdes

Serdes

Serdes

Serdes

UART,

UART,HPI

HPI

JTAG,

JTAG,I2C,

I2C,

SPI

SPI

GbE

GbE00

Flexible

FlexibleIO

IO

GbE

GbE11

L1I

L1D

ITLB

DTLB

2D DMA

MDN

TDN

UDN

SWITCH

IDN

STN

Flexible

FlexibleIO

IO

PCIe

PCIe11

MAC

MAC

PHY

PHY

XAUI

XAUI

MAC

MAC

PHY

PHY11

Serdes

Serdes

Serdes

Serdes

DDR2

DDR2Memory

MemoryController

Controller33

DDR2

DDR2Memory

MemoryController

Controller22

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

2- Full-Featured General Purpose Cores

79

2D Mesh Peer-to-peer tile networks

Processor

Homogeneous cores

3-way VLIW CPU, 64-bit instruction

size

…

Memory

L1 cache: 8KB I, 8KB D, 1 cycle

latency

L2 cache: 64KB unified, 7 cycle latency

Off-chip main memory, ~70 cycle

latency

Cache integrated 2D DMA engine

…

5 independent networks (One

dynamic)

PROCESSOR

CACHE

Reg

File

L2 CACHE

P2

P1

Architetture di Sistemi Embedded, AA 2008/2009

L1D

ITLB

DTLB

2D DMA

static, four

IDN – System and I/O

MDN – Cache misses, DMA, other memory

TDN – Tile to tile memory access

UDN, STN – User-level streaming and

scalar transfer

P0

L1I

SWITCH

MDN

TDN

UDN

IDN

STN

Ing. Francesca Palumbo

PicoArray™ (1)

80

PicoArray is an example of heterogeneous massively parallel

processor.

Every computation-intensive cell is a 3-way VLIW RISC

processor.

Interconnection switches are configurable at compile- time in

order to implement a time-division multiplexing scheme on the

different communication streams.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

PicoArray™ (2)

81

Programmers have to:

write threads code in C or ASM language

specify data-dependencies between each

couple of those threads

specify bandwith requirements of each thread

The compiler will translate the code and invoke a

placement tool which in turn generates the

configuration bits for the Interconnection Network

relying on the programmers directives.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

The AM2000 Family - AMBRIC ™

82

First goal : creation of a MPPA

easy to be programmed.

Development of a programming

model easy for the programmer

and

then

conceive

an

architecture optimized for it.

Structural Object Programming

Model (SOPM) : an application

is a workflow and its blocks

(basic Objects) are executed in

parallel each one on a different

core.

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

83

MATERIALE

DI

RIFERIMENTO

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo

84

TIPI DI PARALLELISMO E CLASSIFICAZIONE DI FLYNN:

Patterson, Hennessy; “Struttura e Progettazione dei Calcolatori:

l’interfaccia hardware e software”: capitolo 9 – I processori paralleli

PIPELINING DELLE ISTRUZIONI:

Patterson, Hennessy; “Computer Architecture, A Quantitative

Approach”: appendice A - Pipelining: Basic and Intermediate

Concepts

CMP E MPP:

Patterson, Hennessy; “Struttura e Progettazione dei Calcolatori:

l’interfaccia hardware e software”: capitolo 9 – I processori paralleli

ESEMPI DI MPP:

http://www.picochip.com/products_and_technology/picoarray_archite

cture

http://www.tilera.com/products/TILE64.php

Architetture di Sistemi Embedded, AA 2008/2009

Ing. Francesca Palumbo