MULTIVIBRATORI CON PORTE LOGICHE

MULTIVIBRATORE

Si dice multivibratore un circuito che può avere solo due possibili stati dell’uscita. Tali stati

possono essere di due tipi: stato stabile, stato quasi stabile.

− Stato stabile: il circuito rimane in questo stato finché non si interviene dall’esterno forzando

l’uscita a cambiare stato.

− Stato quasi stabile: il circuito rimane in questo stato per un tempo prestabilito per poi passare

nell’altro stato.

A secondo del tipo di stati del circuito, i multivibratori si distinguono in:

− multivibratore astabile: ha due stati entrambi quasi stabili; pertanto, commuta continuamente

da uno all’altro ad intervalli di tempo costanti: viene utilizzato per generare segnali a due livelli,

tipo onda quadra (generatore d’onda quadra e di clock).

− multivibratore monostabile: ha uno stato stabile ed uno quasi stabile; il circuito rimane nello

stato stabile finché, mediante un impulso esterno, viene costretto a commutare nell’altro stato,

che mantiene per un tempo prestabilito per poi commutare nello stato stabile in cui rimane fino

al successivo impulso esterno: viene utilizzato per generare impulsi singoli di durata prestabilita

(generatore d’impulso).

− multivibratore bistabile: ha due stati entrambi stabili; pertanto, può commutare da uno stato

all’altro solo se si interviene dall’esterno: tipici i latch e i filp-flop.

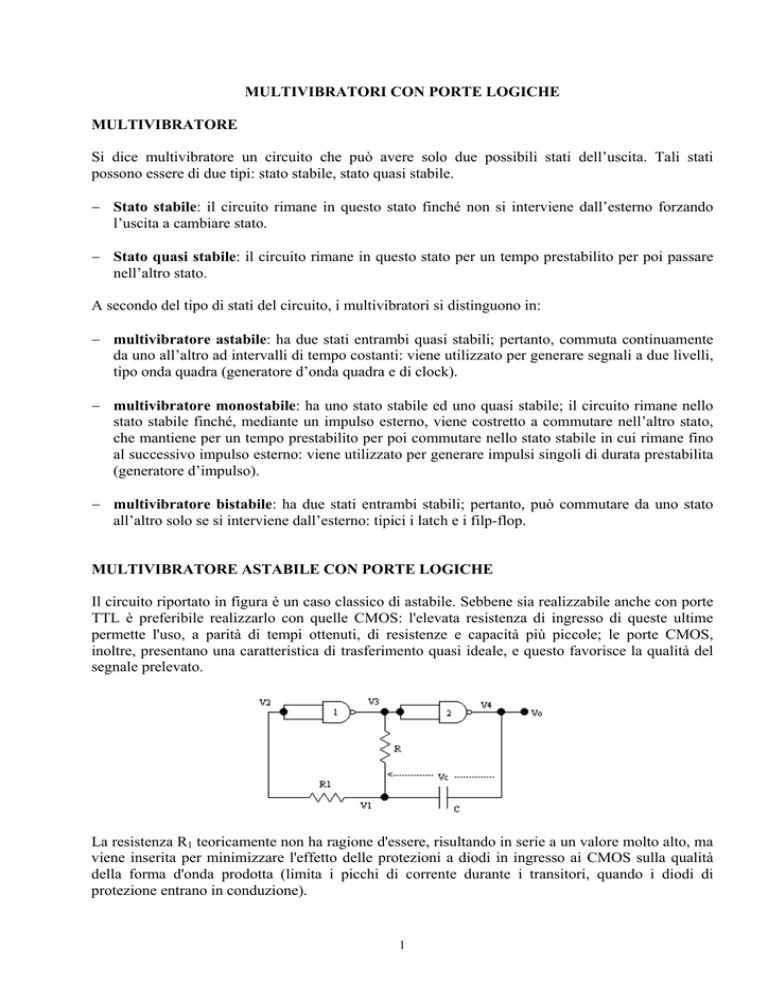

MULTIVIBRATORE ASTABILE CON PORTE LOGICHE

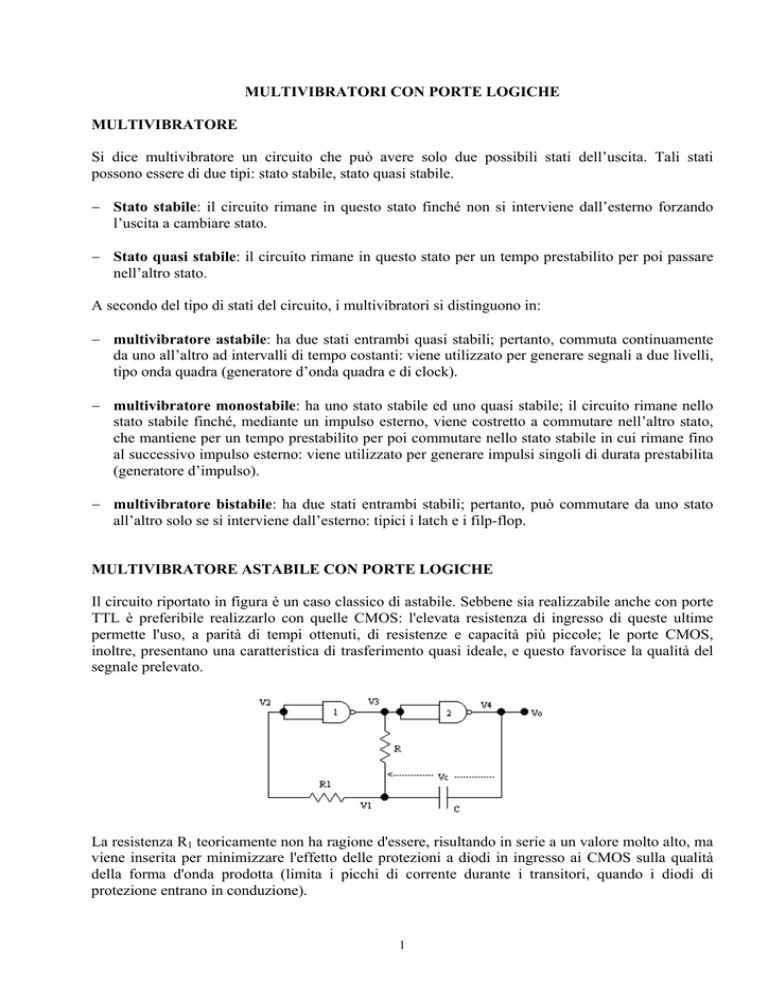

Il circuito riportato in figura è un caso classico di astabile. Sebbene sia realizzabile anche con porte

TTL è preferibile realizzarlo con quelle CMOS: l'elevata resistenza di ingresso di queste ultime

permette l'uso, a parità di tempi ottenuti, di resistenze e capacità più piccole; le porte CMOS,

inoltre, presentano una caratteristica di trasferimento quasi ideale, e questo favorisce la qualità del

segnale prelevato.

La resistenza R1 teoricamente non ha ragione d'essere, risultando in serie a un valore molto alto, ma

viene inserita per minimizzare l'effetto delle protezioni a diodi in ingresso ai CMOS sulla qualità

della forma d'onda prodotta (limita i picchi di corrente durante i transitori, quando i diodi di

protezione entrano in conduzione).

1

Sia in uscita al NOT 1 che al 2 è possibile prelevare un segnale quadro, anche se, per limiti

costruttivi dei componenti, quello in 1 risulta, spesso troppo deformato.

Nell’analisi del comportamento di un multivibratore astabile conviene fissare l’attenzione su tre

istanti successivi:

− istante immediatamente precedente la commutazione;

− istante della commutazione;

− istante successivo alla commutazione.

Inoltre, al fine di comprendere le dinamiche di carica e di scarica del condensatore, conviene

schematizzare l’ingresso e l’uscita delle porte mediante circuiti equivalenti, riportati in figura.

VCC

VCC

Ro2

T2

VCC

T2

Vo

Vo

Vi

T1

T1

Ro1

Uscita

Uscita approssimata

Ingresso

Poiché le resistenze R01 e R02 sono molto piccole e trascurabili rispetto alla resistenza R, nel circuito

equivalente d’uscita possono essere eliminate semplificando la risoluzione del circuito.

Le due porte logiche hanno sempre stato d’uscita negato l’una rispetto all’altra. Pertanto, si hanno

due schematizzazioni di funzionamento del circuito: NOT 1 uscita bassa e NOT 2 uscita alta (figura

a); NOT 1 uscita alta e NOT 2 uscita bassa (figura b).

VCC

V3

V2

V4

1

R1

2

V1

VCC

VCC

VCC

V3

V2

V4

1

Vo

2

R

R

i

i

VC

R1

Figura a

V1

Figura b

2

Vo

VC

Nel grafico sono riportate le forme d’onda nei vari punti del circuito, e precisamente:

−

−

−

−

v1 tensione di una armatura del condensatore riferita alla massa;

v2 tensione d’ingresso della NOT 1;

v3 tensione d’uscita della NOT 1 e tensione d’ingresso della NOT 2;

v4 = vo tensione d’uscita della NOT 2 (che è anche la tensione d’uscita del circuito) e tensione

sull’altra armatura del condensatore riferita alla massa;

− vc = v4 – v1 differenza di potenziale ai capi del condensatore.

3VCC/2

V1

VCC/2

t

-VCC/2

VCC+0,7

V2

VCC

VCC/2

-0,7

t

V3

VCC

T1

0

VCC

T2

t1

VCC/2

t

t2

t

V 4 = Vo

T1

0

t2

T2

t1

V C = V1 – V 4

t

-VCC/2

3

Determinazione del semiperiodo T1

Istante immediatamente precedente la commutazione

VCC

; poiché l’ingresso

2

della NOT 1 non assorbe praticamente corrente, non si ha alcuna caduta di tensione sulla resistenza

V

V

R1; pertanto v1 = v 2 <≈ CC , v 3 = v CC , v 4 = 0 , v C = v1 − v 4 <≈ CC (Figura b).

2

2

A t < ≈ 0 v2, aumentando, sta per raggiungere la tensione di soglia VT =

Istante della commutazione

VCC

; istantaneamente, v3

2

commuta a livello basso (0V) e v4 commuta a livello alto (VCC) (Figura a).

In questo istante (t = 0), la capacità C non può variare istantaneamente la tensione ai suoi capi

V ⎞

⎛

⎜ v C = CC ⎟ (il condensatore deve variare la sua tensione di -VCC), pertanto la variazione di

2 ⎠

⎝

V

V

tensione VCC viene trasferita su v1, che si porta a v1 = v C + v 4 = CC + VCC = 3 CC .

2

2

La tensione v2 (che era uguale a v1) non può, però, assumere tale valore perché, superando VCC,

entra in conduzione il diodo di protezione collegato verso VCC, limitando il valore della tensione v2

a VCC + 0,7V. Questo diodo rimane in conduzione fino a che v1 arriva la valore VCC, ossia quando

vc raggiunge il valore zero; da tale istante si ha di nuovo v2 = v1.

A t = 0 v2 uguaglia, e tende a superare, la tensione di soglia VT =

Istante successivo alla commutazione

VCC

, e tenderà a

2

caricarsi in verso opposto verso –VCC, con costante di tempo τ = RC (essendo R1 >>R).

La commutazione delle uscite avviene quando, dopo un tempo T1, ossia a t1, la tensione v1 = v 2 ,

V

diminuendo, uguaglia e tende a scendere sotto il valore di soglia VT = CC . In questo istante la

2

tensione sul condensatore vale:

Dall’istante t = 0 il condensatore inizia a scaricarsi, partendo dal valore v C =

v1 = v 2 = v C + v 4 = v C + VCC =

VCC

2

⇒ v C = −VCC +

VCC

V

= − CC

2

2

avendo preso come verso positivo di vc quello riportato nel circuito (vc è positivo quando v1 è

positivo rispetto massa).

L’equazione di carica del condensatore è:

v C ( t ) = Vf + (Vi − Vf ) ⋅ e

A t = t1 = T1

v C (t 1 ) = − VCC +

−

t

τ

−

3

⎛V

⎞ −

= − VCC + ⎜ CC + VCC ⎟ ⋅ e τ = −VCC + VCC ⋅ e τ

2

⎝ 2

⎠

t

T

− 1

V

3

VCC ⋅ e τ = − CC

2

2

4

T

⇒

t

T

− 1

3 − τ1 1

1

⋅e =

⇒ e τ =

⇒

2

2

3

⇒ −

T1

1

= ln

⇒ T1 = τ ln 3 ≅ 1,1RC

τ

3

Determinazione del semiperiodo T2

Istante immediatamente precedente la commutazione

VCC

; poiché l’ingresso

2

della NOT 1 non assorbe praticamente corrente, non si ha alcuna caduta di tensione sulla resistenza

V

V

R1; pertanto v1 = v 2 >≈ CC , v 3 = VCC , v 4 = 0VCC , v C = v1 − v 4 >≈ − CC (Figura a).

2

2

A t < ≈ t1 v2, diminuendo, sta per raggiungere la tensione di soglia VT =

Istante della commutazione

VCC

; istantaneamente, v3

2

commuta a livello alto (VCC) e v4 commuta a livello basso (0V) (Figura b).

In questo istante (t = t1), la capacità C non può variare istantaneamente la tensione ai suoi capi

V ⎞

⎛

⎜ v C = − CC ⎟ (il condensatore deve variare la sua tensione di +VCC), pertanto la variazione di

2 ⎠

⎝

V

V

tensione VCC viene trasferita su v1, che si porta a v1 = v C + v 4 = − CC + 0 = − CC .

2

2

La tensione v2 (che era uguale a v1) non può, però, assumere tale valore perché, diventando negativa

rispetto massa, entra in conduzione il diodo di protezione collegato verso massa, limitando il valore

della tensione v2 a -0,7V. Questo diodo rimane in conduzione fino a che v1 arriva la valore 0V,

ossia quando vc raggiunge il valore zero; da tale istante si ha di nuovo v2 = v1.

A t = t1 v2 uguaglia, e tende a scendere sotto la tensione di soglia VT =

Istante successivo alla commutazione

VCC

, e tenderà a

2

caricarsi in verso opposto verso +VCC, con costante di tempo τ = RC (essendo R1 >>R).

La nuova commutazione delle uscite avviene quando, dopo un tempo T2, ossia a t2, la tensione

V

v1 = v 2 , aumentando, uguaglia e tende a superare il valore di soglia VT = CC . In questo istante la

2

tensione sul condensatore vale:

Dall’istante t = t1 il condensatore inizia a scaricarsi, partendo dal valore v C = −

v1 = v 2 = v C + v 4 = v C + 0 =

VCC

2

⇒ vC =

VCC

2

avendo preso come verso positivo di vc quello riportato nel circuito (vc è positivo quando v1 è

positivo rispetto massa).

L’equazione di carica del condensatore è:

v C ( t ) = Vf + (Vi − Vf ) ⋅ e

−

t − t1

τ

⎛ V

⎞ −

= VCC + ⎜ − CC − VCC ⎟ ⋅ e

2

⎝

⎠

5

t − t1

τ

−

3

= VCC − VCC ⋅ e

2

t − t1

τ

A t = t2 (t2 – t1 = T2)

v C (t 2 ) = VCC

⇒ −

T

− 2

V

3

− VCC ⋅ e τ = CC

2

2

T

T

− 2

3 − τ2 1

1

⋅e

=

⇒ e τ =

⇒

2

2

3

⇒

T1

1

= ln

⇒ T1 = τ ln 3 ≅ 1,1RC

τ

3

E il ciclo si ripete generando su v3 e v4 due onde quadre in opposizione di fase. Il periodo vale:

T = T1 + T2 = 2,2τ = 2,2RC

Si consiglia di porre R1 = l0R, almeno, per evitare che possa produrre effetto sulla frequenza,

alterando la costante di tempo.

Usando dispositivi della serie 4xxxB, se si vogliono ottenere buoni risultati si consigliano valori per

R compresi tra 10kΩ e lMΩ, e per la capacità non sotto i 100pF; sono inoltre consigliabili

dispositivi di tipo buffer, specie alle frequenze più alte (alcuni MHz come massimo); con dispositivi

HC e HCT il limite di frequenza più elevato permette l'uso anche di capacità più piccole e non è

necessario l'uso di porte buffer. Se si rinuncia alla resistenza R1 i risultati risultano mediamente

meno buoni (minore simmetria nel segnale e maggiore dipendenza della frequenza dalla tensione di

alimentazione), ma molto dipende dal tipo di IC scelto e, a parità di sigla, dalla marca dello stesso;

quindi la scelta tra le due soluzioni potrà essere meglio valutata caso per caso sperimentalmente.

Se si rinuncia a R1, l'intervento delle protezioni modifica il periodo e quindi la frequenza del

segnale nel seguente modo:

1

T = 1,4RC ⇒ f = 0,72

RC

Se si usano porte TTL R deve essere minore 1,5kΩ e R1 = 0. per i semiperiodi si ha:

T1 = 1,6RC

T2 = 0,56RC

6

T = 2,16RC

MONOSTABILE A PORTE LOGICHE (GENERATORE DI RITARDO)

Spesso, nel comando dei circuiti, si dispone di segnali elettrici o meccanici (trasformati in elettrici

da opportuni trasduttori) di durata troppo breve per consentire ai circuiti stessi di adeguarsi al

segnale di comando.

Per ovviare a questo inconveniente, vengono realizzati circuiti che variano lo stato elettrico della

propria uscita in seguito ad un impulso d’ingresso e mantengono lo stato commutato per un tempo

variabile in funzione delle condizioni di progetto.

Questi circuiti vengono detti multivibratori monostabili o generatori di ritardo. Il termine

monostabile deriva dal fatto che, in assenza di segnali applicati all’ingresso, questi dispositivi hanno

un livello stabile di segnale d’uscita. Allorché viene fornito un comando, lo stato dell’uscita

commuta e si mantiene a livello commutato per un periodo prestabilito, al termine del quale si

ripristina lo stato precedente stabile.

In figura è riportato lo schema di un circuito monostabile realizzato con porte CMOS.

L’uscita della porta NOR ha stato logico 1 se e solo se entrambi gli ingressi A e B hanno stato

logico 0; qualunque altra combinazione degli ingressi A e B porta l’uscita allo stato logico 1.

pertanto, lo stato stabile deve essere associato a ingressi entrambi a livello basso.

Stato stabile: A = B = 0; VA = VB = 0; VD = VCC; VE = VCC; VC = 0; Vo = VB = 0.

⎧A = 0 ⇒ VA = 0

⎧A = 1 ⇒ VA = VCC

Stato quasi stabile: A = B = 1 = VCC ⎨

; ⎨

;

⎩B = 1 ⇒ VB = VCC ⎩B = 0 ⇒ VB = 0

VD = 0; VE = VC; Vo = VB = VCC.

Circuito equivalente dell’uscita della NOR e dell’ingresso della NOT nello stato stabile.

7

Con VA = 0, la sola condizione stabile compatibile col circuito presenta uscita bassa, Vo = 0, che

fissa a livello basso anche l’altro ingresso della NOR, VB = Vo = 0. In tale caso, l’uscita della NOR

sarà a livello alto, VD = VCC. Poiché una porta CMOS non assorbe praticamente corrente

all’ingresso, non circolerà corrente neanche nella resistenza R e l’ingresso della NOT si troverà a

VE = VCC: livello alto d’ingresso che porta l’uscita a livello basso, Vo = VB = 0. Il condensatore,

avendo le sue armature alla stessa tensione VCC, risulta scarico, VC = 0.

Applicando all’ingresso A, nell’istante t = 0, un breve impulso di ampiezza VCC e durata To, si avrà:

⎧VA (0 ) = VCC

⎨

⎩VB (0 ) = 0

⇒ VD (0 ) = 0

Circuito equivalente dell’uscita della NOR e dell’ingresso della NOT nello stato quasi stabile.

Poiché la tensione ai capi del condensatore C non può cambiare istantaneamente, la stessa

variazione di tensione subita da VD dovrà risultare per VE: ∆VD (0) = ∆VE (0) = −VCC . Infatti,

essendo il condensatore inizialmente scarico, si troverà con i terminali allo stesso potenziale e

l’ingresso della NOT si porterà da VCC a 0: VE (0 ) = VD (0 ) = 0 , situazione che porta l’uscita della

NOT a livello alto: Vo (0) = VB (0) = VCC .

⎧VA (0 ) = VCC

,

⎨

⎩VB (0 ) = VCC

Il circuito si è portato nello stato quasi stabile:

e cessato l’impulso (dopo che Vo è passato allo stato alto)

⎧VA (0 ) = 0

⎨

⎩VB (0 ) = VCC

⇒ VD (0 ) = 0 e V0 (0 ) = VCC .

Negli istanti successivi il condensatore si carica, attraverso R, verso VCC. Quando, durante la carica,

V

raggiunge, dopo un tempo T, la tensione di soglia VT = CC dell’invertitore, l’uscita della NOT

2

torna a livello basso Vo (T ) = VB (T ) = 0 .

La porta NOR, avendo entrambi gli ingressi allo stato basso, commuta la sua uscita a livello alto:

⎧VA (T ) = 0

⇒ VD (T ) = VCC

⎨

⎩VB (T ) = 0

8

e VC (T ) =

VCC

2

Circuito equivalente dell’uscita della NOR e dell’ingresso della NOT in tale situazione.

Poiché la tensione ai capi del condensatore C non può cambiare istantaneamente, la stessa

variazione di tensione subita da VD dovrà risultare per VE: ∆VD (T ) = ∆VE (T ) = VCC . Quindi,

VE (T ) = ∆VE (T ) + VC (T ) = VCC +

VCC 3

= VCC ,

2

2

poiché la tensione all’ingresso della porta NOT supera VCC, entra in funzione la limitazione della

tensione d’ingresso che limita la tensione a VCC + 0,7V, e si avrà la rapida scarica del condensatore

da VT a zero, ripristinando le condizioni dello stato stabile.

I diagrammi temporali sono riportati di seguito.

VA

VCC

VD

To

t

VCC

∆V= VCC

t

VE

VCC +VCC/2

∆V= VCC

VCC

VCC/2

Vo

Tr

t

t=T

t

VCC

T

t=0

9

Determinazione di T

Il condensatore, a partire dall’istante t = 0, si carica con costante di tempo τ = RC da VC(0) = 0

verso VCC, con equazione

v C ( t ) = Vf + (Vi − Vf ) ⋅ e

−

t

τ

= VCC − VCC ⋅ e

−

t

τ

t

− ⎞

⎛

= VCC ⎜⎜1 − e τ ⎟⎟

⎝

⎠

VCC

, si ha la

2

commutazione dell’uscita e viene interrotta la carica. Per calcolare T si impone, nell’equazione di

carica di C, che al tempo t = T, la tensione sul condensatore raggiunga la tensione di soglia VT

dell’ingresso della NOT:

Quando la tensione sulla capacità arriva, dopo un tempo T, (t = T), a v C (T ) = VT =

v C (T ) = VCC − VCC ⋅ e

−

T

τ

=

VCC

2

⇒ e

−

T

τ

=

1

T

1

⇒ − = ln

⇒ T = τ ln 2 = 0,693RC

2

τ

2

Si deve osservare che, qualora l'impulso di trigger sia di durata maggiore di quello in uscita,

quest'ultimo non subisce comunque variazioni: cambia invece la durata dell'impulso VA che,

anziché durare quanto l'impulso di uscita, dura quanto quello in ingresso (come evidenziato dai

seguenti diagrammi vettoriali).

VA

VCC

To

VD

t

VCC

t

VE

VCC +VCC/2

VCC

VCC/2

t

Vo

VCC

T

t=0

t=T

t

Si osservi infine che in questi circuiti! poiché la soglia di commutazione VT è soggetta a notevoli

variazioni, rispetto al valore teorico, sia per tolleranze costruttive che in relazione alla tensione di

10

alimentazione e al costruttore, la durata dell'impulso può presentare, rispetto al valore teorico,

differenze comprese tra il -50% e il +70% (può essere opportuno usare come R un trimmer da tarare

sperimentalmente).

V

Le variazioni della tensione di soglia nell’intorno di CC è pari a ±40% di VT; per cui la durata

2

dell’impulso può subire una notevole variazione. Il costruttore garantisce che il valore della

tensione di soglia è sicuramente compreso tra 0,3VDD e 0,7VDD. In corrispondenza di tali valori

limite calcoliamo la durata massima e minima che può avere l’impulso.

Esprimiamo la durata dell’impulso in funzione della tensione di soglia VT.

v C (T ) = VCC − VCC ⋅ e

⇒ −

−

T

τ

= VT

V − VT

T

= ln CC

τ

VCC

⇒ e

−

T

τ

=

⇒ T = τ ln

VCC − VT

VCC

⇒

VCC

VCC − VT

Calcolo di TM

VCC

deve assumere il minimo valore possibile

VCC − VT

in modo da produrre un impulso di durata massima. La frazione avrà valore massimo quando VT

assume il suo valore massimo di 0,7VCC:

In questo caso il denominatore della frazione

TM = τ ln

∆T% =

VCC

VCC

1

= τ ln

= 1,2τ = 1,73T

− 0,7VCC

0,3

∆TM

T −T

1,2 − 0,693

⋅ 100 = M

⋅ 100 =

⋅ 100 = +73,16%

T

0,693

T

Calcolo di Tm

VCC

deve assumere il massimo valore possibile

VCC − VT

in modo da produrre un impulso di durata minima. La frazione avrà valore minimo quando VT

assume il suo valore minimo di 0,3VCC:

In questo caso il denominatore della frazione

Tm = τ ln

∆T% =

VCC

VCC

1

= τ ln

= 0,357 τ = 0,51T

− 0,3VCC

0,7

∆Tm

T −T

0,357 − 0,693

⋅ 100 = m

⋅ 100 =

⋅ 100 = −48%

T

0,693

T

Il valore che si ottiene è sicuramente compreso tra 0,51T ≤ durata impulso ≤ 1,73T.

11

Durata To dell’impulso d’ingresso

Qualora non sia trascurabile il ritardo di propagazione delle porte logiche, la tensione VD commuta,

anziché nell’istante t = 0, in quello t = tp e così pure la tensione VE. nell’ipotesi che anche il ritardo

di propagazione dell’invertitore sia tp, la tensione VB = Vo commuta dopo un tempo 2tp rispetto

all’istante nel quale è stato applicato l’impulso. Poiché la tensione VD rimane a livello basso solo se

uno degli ingressi è a livello alto, ne segue che la tensione Vo deve commutare prima che termini

l’impulso. Pertanto, la durata minima dell’impulso deve essere superiore a 2tp.

Volendo realizzare un monostabile con impulso di trigger negativo si possono usare due NAND,

come in figura.

VA

VCC

VD

To

t

VCC

t

VCC

VE

VCC/2

Tr

t

-VCC/2

Vo

VCC

T

t=0

t=T

12

t

IL CIRCUITO INTEGRATO 4047B

Il circuito integrato CD4047BE è un integrato CMOS che viene utilizzato per realizzare

multivibratori astabili e monostabili. Il diagramma delle connessioni è il seguente:

C

1

R

2

RC

3

ASTABILE

4

ASTABILE

5

– TRIGGER

6

C

D

4

0

4

7

B

E

7

GND

14

VCC

13

OSC OUT

12

RETRIGGER

11

Q

10

Q

9

EXT RESET

8

+ TRIGGER

Una capacità esterna (tra i piedini 1 e 3) e una resistenza esterna (tra i piedini 2 e 3) determinano la

durata dell’impulso nel funzionamento monostabile, e la frequenza dell’uscita nel funzionamento

astabile.

Il funzionamento astabile si ottiene mettendo a livello alto l’ingresso ASTABILE o a livello basso

l’ingresso ASTABILE . La frequenza d’uscita (con un duty cycle del 50%) alle uscite Q e Q è

determinata dei componenti esterni (R e C) di temporizzazione. Una frequenza doppia di quella su

Q è disponibile all’uscita oscillatore (OSC OUT); ma non è garantito un duty cycle del 50%.

Il funzionamento monostabile si ottiene quando il dispositivo è triggerato da una transizione da

basso ad alto sull’ingresso +TRIGGER o da una transizione da alto a basso sull’ingresso –

TRTIGGER. Il dispositivo può essere retriggerato applicando una transizione da basso ad alto

contemporaneamente sugli ingressi +TRIGGER e RETRIGGER.

Un livello alto sull’ingresso RESET resetta l’uscita Q a livello basso e l’uscita Q a livello altro.

Tabella di funzionamento

Funzione

Connessione dei terminali

A GND

Impulso

A VCC

d’ingresso

Multivibratore astabile

Oscillazione libera

Uscita dritta

Uscita negata

Multivibratore monostabile

Positive edge triggered

Negative edge triggered

Retriggerabile

Contatore esterno (Nota 1)

Impulso

d’uscita

Periodo tipico

d’uscita o durata

dell’impulso

TA (10, 11) = 4,4RC

4, 5, 6,

14

4, 6, 14

6, 14

7, 8, 9, 12

7, 8, 9, 12

5, 7, 8, 9, 12

5

4

10, 11, 13

10, 11, 13

10, 11, 13

4, 14

4, 8, 14

4, 14

14

5, 6, 7, 9, 12

5, 7, 9, 12

5, 6, 7, 9

5, 6, 7, 8, 9, 12

8

6

8, 12

Figura 1

10, 11

10, 11

10, 11

Figura 1

TA (13) = 2,2RC

TM (10, 11) = 2,48RC

Figura 1

Nota 1. Resistenza esterna tra i terminali 2 e 3. capacità esterna tra i terminali 1 e 3.

ASTABILE

Impulso

d’ingresso

4

10

Q

out

N counter

NOT

TEXT

clock

reset

13

TEXT = ( N − 1)TA + (TM + TA / 2 )

Il circuito astabile, con oscillazione libera, e il seguente:

R

RP

C

+VCC

14

2

3

1

11

Q

fCK/2

13

OSC OUT

fCK

D = 0,5

6

CD4047BE

5

4

7

8

9

12

10

fCK/2

Q

D = 0,5

Funzionamento da monostabile: è possibile lavorare con un trigger che agisce sul fronte di salita

(positive edge trigger) o sul fronte di discesa (negative edge trigger); si ha anche la possibilità di

retriggerare l'impulso in uscita, cioè di allungarne la durata, applicando un impulso positivo al pin

12.

Un'ultima possibilità d'uso nel modo monostabile si ha tramite un contatore esterno che permette di

ottenere impulsi di durata molto lunga (external countdown).

Nel funzionamento monostabile il segnale va prelevato dai pin l0 e 11. Si noti anche la presenza di

un ingresso di reset attivo alto che permette di interrompere anticipatamente un ciclo di

temporizzazione o di impedirne l'inizio.

La figura a si riferisce al monostabile con trigger positivo, la figura b a quello con frigger negativo.

R

C

3

2

+VCC

1

4

14

10

8

Q

to

Figura a

CD4047BE

11

5

6

7

9

12

Q

to = 2,48RC

R

C

3

2

+VCC

1

4

8 14

10

Q

to

6

CD4047BE

Figura b

11

5

7

9

14

12

Q

to = 2,48RC

Per un dimensionamento corretto si consiglia di usare un valore di R compreso tra l0kΩ e 1MΩ e

per C valori > 100pF nel funzionamento astabile, e > 1000pF nel funzionamento monostabile.

Le relazioni di progetto sono:

-

configurazione astabile

T = 2,2RC (OSC OUT) ; C ≥ 100pF e 10KΩ ≤ R ≤ 1MΩ

-

configurazione monostabile

T = 2,48RC

;

C ≥ 1ηF e 10KΩ ≤ R ≤ 1MΩ

i condensatori devono essere di tipo non polare (elettrolitici o al tantalio).

15