caricato da

common.user5530

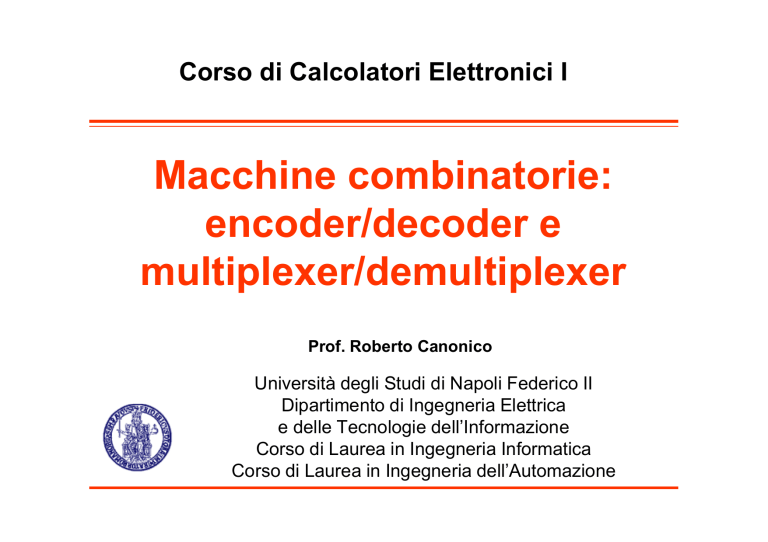

Macchine Combinatorie: Encoder/Decoder e MUX/DEMUX

Corso di Calcolatori Elettronici I Macchine combinatorie: encoder/decoder e multiplexer/demultiplexer Prof. Roberto Canonico Università degli Studi di Napoli Federico II Dipartimento di Ingegneria Elettrica e delle Tecnologie dell’Informazione Corso di Laurea in Ingegneria Informatica Corso di Laurea in Ingegneria dell’Automazione Decodificatore (decoder) 1 su m • Un decodificatore è una macchina che riceve in ingresso una parola codice (C) su n bit e presenta in uscita la sua rappresentazione decodificata (linee U0, … UN-1) su m=2n bit Co U0 Cn-1 Um-1 Decoder 1 su 4 U0 = B . A Esempio: decoder 1:4 U1 = B. A B A U0 U1 U2 U3 1 2 3 4 0 0 1 1 0 1 0 1 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1 U2 = B . A U3 = B . A A B Composizione modulare di decoder: decoder 4:16 con decoder 2:4 DEC 2:4 1 C D A B U0 DEC U1 2:4 U2 U3 DEC 2:4 DEC 2:4 DEC 2:4 U0 U1 U2 U3 U0 U1 U2 U3 U0 U1 U2 U3 U0 U1 U2 U3 U0 U1 U2 U3 U4 U5 U6 U7 U8 U9 U10 U11 U12 U13 U14 U15 Encoder o codificatore • Un codificatore riceve in ingresso una rappresentazione decodificata (linee x0, … xm-1) e fornisce in uscita una rappresentazione con un codice a lunghezza fissa di n bit • L’uscita è la parola codice associata a xi x0 se xi=1 zo ed α=1 (abilitazione) • Vincolo su ingressi: xi⋅ xj = 0 per i≠j zm-1 xN-1 α Codificatore a 4 ingressi da: G. Bucci. Calcolatori Elettronici – Architettura e organizzazione. © McGraw-Hill, 2009 Codificatore 8-4-2-1 • • • • z3= x8+x9 z2= x4+x5+ x6+x7 z1= x2+x3+ x6+x7 z0= x1+x3+ x5+x7+x9 C O D IC E D E C IM cifra 0 1 2 3 4 5 6 7 8 9 8 -4 -2 -1 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 Arbitro di priorità Un codificatore può essere preceduto da una “rete a priorità” che, in caso di più ingressi contemporaneamente alti, filtra quello con priorità assegnata maggiore • Rete a priorità – n ingressi Xi – n uscite corrispondenti Fi, che rappresentano gli ingressi del codificatore – fra gli ingressi è definita una priorità, ad esempio: • per fissare le idee «Xi è prioritario su Xj se i < j» – L'uscita Yi è alta se e solo se Xi è alto e tutti gli altri ingressi prioritari su Xi sono bassi. F1 = X 1 F2 = X 2 X 1 KK Fn = X n X n −1 K X 1 Arbitro di priorità a 4 ingressi da: G. Bucci. Calcolatori Elettronici – Architettura e organizzazione. © McGraw-Hill, 2009 Multiplexer lineare • Un Multiplexer lineare (ML) è una macchina con: – n ingressi-dati (A0,…,An-1) – n segnali binari di selezione (α0,…, α n-1), dei quali al più uno è attivo – una uscita-dati B, che assume • valore Ai se è attivo α i • neutro se nessuna delle selezioni è attiva A0 B MUXL An-1 • utilizzata quando più linee devono essere convogliate verso un’unica linea di uscita (bus) α0 αn-1 Multiplexer binario • Se i dati Ai e B sono semplici bit si parla di multiplexer binario A0 B MUXL An-1 α0 αn-1 Multiplexer binario - realizzazioni • B = A0 α0 + A1α1 + ... + An-1αn-1 n=4 – Realizzazione I • Con porte AND e OR – Realizzazione II • Con porte 3-state A 0 0 1 1 S 0 1 0 1 – S=1, restituisce il valore di A – S=0, restituisce un’alta Uscita impedenza (apre il circuito) z 0 z 1 Multiplexer (indirizzabile) • Multiplexer Lineare i cui segnali di abilitazione sono collegati con le uscite di un decodificatore A0 MUXL B AN-1 α0 αN-1 C Demultiplexer lineare • Un Demultiplexer Lineare è una macchina con: – 1 ingresso-dati B – n segnali binari di selezione (α0,…, αn-1), dei quali al più uno è attivo – n uscite-dati (A0,…,An-1), B con • Ai=B se è attivo αi • neutro se nessuna delle selezioni è attiva A0 DMUXL A n-1 α0 αn-1 Demultiplexer (indirizzabile) • Demultiplexer Lineare i cui segnali di abilitazione sono collegati con le uscite di un decodificatore A0 B DEMUX AN-1 α0 αN-1 C Muxl/Dmuxl: un esempio • Supponiamo di avere un “centralino telefonico” in cui n utenti sorgente vogliono parlare con m utenti destinazione – vincolo: l’utente di destinazione abilitato deve sentire solo l’utente sorgente abilitato A0 A1 B0 B1 … MUXL DMUXL … An-1 Bm-1 … 0 1 0.. 0 … 0 0 0..0 1 Linee di sel. Linee di sel. utente sorgente utente destinaz. L’utente A1 è abilitato a parlare con l’utente Bm-1