Elettronica II

Corso di Laurea in Informatica

Crema, 22 maggio 2002

Memorie a semiconduttore (1)

Stefano Gregori

Department of Electrical Engineering

The University of Texas at Dallas

P.O. Box 830688

Richardson, Texas 75083

E-mail: [email protected]

Stefano Gregori

Memorie a semiconduttore

Crema, 22-5-2002

1

Argomenti

introduzione

circuiti di memoria elementari: latch, flip-flop, registri

memorie a semiconduttore

struttura e funzionamento delle memorie

Stefano Gregori

Memorie a semiconduttore

Crema, 22-5-2002

2

Memorizzare l’informazione

1 bit

1 byte = 8 bit

1 bit: una singola unità binaria d'informazione

1 byte: un carattere dell'alfabeto

10 byte: una parola

100 byte: un messaggio SMS (short message service)

1 kbyte = 210 byte

2 kilobyte: una pagina dattiloscritta

50 kilobyte: un racconto

100 kilobyte: un'immagine

1 Mbyte = 220 byte

1 megabyte: un libro (senza immagini)

10 megabyte: una tesi di laurea con immagini e grafici

100 megabyte: il contenuto di un CD audio (74,5 minuti di musica)

650 megabyte: il contenuto di un CD-ROM

1 Gbyte = 230 byte

2 gigabyte: un film compresso in formato MPEG

17 gigabyte: il contenuto di un DVD-ROM

50 gigabyte: il contenuto di una libreria

500 gigabyte: il contenuto di un grosso sito FTP (file transfer protocol)

1 Tbyte = 240 byte

1 terabyte: tutte le lastre a raggi X di un grosso ospedale

10 terabyte: il contenuto della più grande biblioteca del mondo

1 Pbyte = 250 byte

8 petabyte: tutte le informazioni disponibili sul world-wide web

200 petabyte: tutto ciò che è stampato nel mondo

1 Ebyte = 260 byte

8 exabyte: tutte le informazioni memorizzate in un anno nel mondo

71 exabyte: il totale dell'informazione archiviata nel mondo

(escluse le duplicazioni)

Stefano Gregori

Ogni anno sono memorizzati 8

miliardi di miliardi di byte di nuovi

dati.

Memorizzare un’informazione

significa trasmetterla attraverso il

tempo (serve un supporto per

registrarla, un codice di

rappresentazione e una codifica di

messaggio).

I supporti più usati sono:

carta

pellicole fotografiche

supporti magnetici

supporti ottici

memorie a semiconduttore

Memorie a semiconduttore

Crema, 22-5-2002

3

La funzione di memoria

In ogni sistema per l’elaborazione dell’informazione è

necessario memorizzare dei dati (risultati di elaborazioni

intermedie, dati dell’utente, impostazioni, valori di

calibrazione, …).

I dati possono essere memorizzati in formato analogico o

in formato digitale, per periodi di tempo molto brevi o

molto lunghi.

I circuiti elettronici digitali che svolgono la funzione di

memoria sono chiamati reti sequenziali.

L’elevata potenza di calcolo dei moderni sistemi

elettronici dipende dalla disponibilità di memorie veloci,

poco ingombranti ed economiche come le memorie a

semiconduttore.

Stefano Gregori

Memorie a semiconduttore

Crema, 22-5-2002

4

Modello di rete sequenziale

Le reti sequenziali sono caratterizzate dalla presenza di

anelli. Una rete con k anelli ha al massimo 2k possibili stati

interni (i valori assunti da y1, …, yk). Le uscite dipendono non

solo dagli ingressi x1, …, xn, ma anche dallo stato interno.

R

x1

xn

y1

yk

C

z1

zm

y'1

y'k

Nel funzionamento del circuito

giocano un ruolo essenziale i

ritardi dz1, …, dzm, dy1, …, dyk, con

cui si formano le uscite in funzione

degli ingressi applicati al tempo t.

zi(t + dzi) = fzi(x1(t), …, xn(t), y1(t), …, yk(t))

yj'(t + dzj) = fyj(x1(t), …, xn(t), y1(t), …, yk(t))

1 ≤ i ≤ m, 1 ≤ j ≤ k

Stefano Gregori

Memorie a semiconduttore

Crema, 22-5-2002

5

Circuiti bistabili

I circuiti bistabili (detti anche latch o flip-flop) sono le reti

sequenziali con la minima capacità di memoria. Hanno due

stati, quindi un solo anello e sono utilizzati per memorizzare

un bit.

Il latch più semplice

y

è formato da due

inverter.

y

z

y'

Stefano Gregori

il latch ha 3 stati stazionari:

2 stati stabili ( )

1 stato metastabile ( )

y'

Memorie a semiconduttore

Crema, 22-5-2002

6

Circuiti bistabili

caratteristica di trasferimento

ad anello aperto del latch

Stefano Gregori

Memorie a semiconduttore

Crema, 22-5-2002

7

Punti di lavoro del latch

Per verificare la stabilità degli stati stazionari si può studiare come evolve

lo stato del circuito. Per semplificare lo studio si può considerare un

comportamento tempo-discreto.

yiniziale = 0,499

yiniziale = 0,501

se yiniziale < 0,5 il circuito raggiunge

lo stato stabile a tensione bassa

se yiniziale > 0,5 il circuito raggiunge

lo stato stabile a tensione alta

Stefano Gregori

Memorie a semiconduttore

Crema, 22-5-2002

8

Punti di lavoro del latch

yiniziale = 0,02

lo stato stabile a tensione bassa è

raggiunto anche partendo da

tensioni inferiori (analogamente lo

stato stabile a tensione alta)

Stefano Gregori

yiniziale = 0,5

lo stato y = 0,5 è uno stato

stazionario metastabile: uno

spostamento comunque piccolo fa

evolvere il circuito verso uno stato

stabile

Memorie a semiconduttore

Crema, 22-5-2002

9

Punti di lavoro del latch

per decidere se uno stato stazionario y0 sia o meno stabile si può

studiare come evolvono piccole variazioni del tipo δn = yn+1 - yn

linearizzando la funzione di trasferimento

yn+1 = α (yn - y0) + y0

si ha che

δn = yn+1 - yn = α (yn - y0) + y0 - yn = (α - 1) (yn - y0)

δn+1 = (α - 1) (yn+1 - y0) = α (α - 1) (yn - y0)

quindi

δn+1 = α δn

ne segue che lo stato è stabile se α < 1

(in generale lo stato è stabile se la derivata della funzione di

trasferimento nel punto considerato è minore di 1)

Stefano Gregori

Memorie a semiconduttore

Crema, 22-5-2002

10

D latch

-Q

D

CLK

Q

Il D latch (o flip-flop delay) è costituito da due inverter e un

multiplexer a due ingressi.

D è il dato in ingresso, CLK è il segnale di clock in ingresso,

Q e -Q sono le uscite.

Stefano Gregori

Memorie a semiconduttore

Crema, 22-5-2002

11

D latch

D latch realizzato con porte NAND.

Q

CLK

D

y'

D

0

1

0

y

y

1

0

1

CLK

Stefano Gregori

Memorie a semiconduttore

Crema, 22-5-2002

12

Flip-flop set reset

z

R

S

y'

C

y

S

0

1

0

y

1

1

0

-

R

y'

Flip-flop set reset realizzato con porte NOR.

R

y'

Q

S

y

Stefano Gregori

Memorie a semiconduttore

Crema, 22-5-2002

13

Flip-flop set reset

Flip-flop set reset realizzato interconnettendo due porte

NOR in tecnologia CMOS con carico a svuotamento.

VDD

Q

S

Stefano Gregori

VDD

Q

R

Memorie a semiconduttore

Crema, 22-5-2002

14

D register

Il D register è costituito da due D latch, il primo chiamato

master e il secondo chiamato slave.

D

-QM

Q

CLK

Stefano Gregori

Memorie a semiconduttore

Crema, 22-5-2002

15

Flip-flop delay master slave

Schema logico di un flip-flop delay master slave

implementato con porte NOR.

CLK

S

Q

CLK

CLK

CLK

Q

D

CLK

CLK

CLK

CLK

R

Stefano Gregori

Memorie a semiconduttore

Crema, 22-5-2002

16

Flip-flop a valvole

flip-flop a valvole elettroniche

(circuito di Eccles-Jordan)

flip-flop a valvole elettroniche

autopolarizzato

da:

W. C. Elmore, M. Sands, Electronics, Experimental

Techniques, McGraw-Hill 1949

da:

J. Millman, H. Taub, Pulse and Digital Circuits,

McGraw-Hill 1956

Stefano Gregori

Memorie a semiconduttore

Crema, 22-5-2002

17

Flip-flop a BJT

flip-flop a transistori bipolari

da:

D. Dewitt, A. L. Rossoff, Transistor Electronics,

McGraw-Hill 1957

Stefano Gregori

Memorie a semiconduttore

Crema, 22-5-2002

18

Memorie a semiconduttore

1) MEMORIE AD ACCESSO CASUALE

memorie a lettura e scrittura (RAM), volatili:

RAM statiche e RAM dinamiche

memorie prevalentemente a sola lettura (ROM),

non volatili: ROM, PROM, EPROM, E²PROM,

Flash

2) MEMORIE AD ACCESSO SERIALE (SAM)

3) MEMORIE INDIRIZZABILI PER CONTENUTO (CAM)

Stefano Gregori

Memorie a semiconduttore

Crema, 22-5-2002

19

Memorie a semiconduttore

memorie ad

accesso casuale

RAM

dinamiche

ROM

statiche

Flash

Stefano Gregori

PROM

EPROM

memorie

volatili

memorie

non volatili

fusibili

E²PROM

Memorie a semiconduttore

Crema, 22-5-2002

20

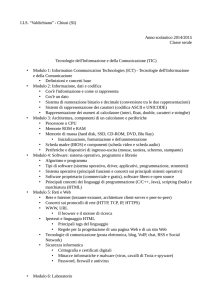

Memorie a semiconduttore

Divisione del mercato delle memorie a semiconduttore

in tecnologia CMOS

DRAM

68%

altre 2,0%

EPROM 0,8%

ROM 3,3%

EEPROM 4,2%

Flash 9,1%

SRAM 12%

Stefano Gregori

Memorie a semiconduttore

Crema, 22-5-2002

21

Caratteristiche

Memoria

EEPROM

riscrivibilità

non

volatilità

FLASH

DRAM

Stefano Gregori

alta

densità

ROM

Caratteristiche

FLASH

basso costo, alta densità; bassa

potenza, elevata affidabilità

ROM

Read-Only Memory

tecnologia matura, altissima

densità, affidabilità, basso costo;

adatte per grandi produzioni con

codice stabile

SRAM

Static Random-Access Memory

massima velocità, elevata

potenza, bassa densità; la bassa

densità fa crescere i prezzi

EPROM

Electrically Programmable ReadOnly Memory

alta densità; devono essere

esposte a radiazione ultravioletta

per la cancellazione

E²PROM

Electrically Erasable

Programmable Read-Only

Memory

cancellabili elettricamente per

byte; bassa affidabilità, alto

costo, bassa densità

DRAM

Dynamic Random Access

Memory

alta densità, basso costo, alta

velocità, alta potenza

Memorie a semiconduttore

Crema, 22-5-2002

22

Decodificatore

n bit

s0

word 0

word 0

s1

word 1

s2

word 2

a0

a1

cella

a2

ak−1

word 1

decodificatore

m word

n bit

word 2

cella

sm−2

word m−2

sm−1

word m−1

word m−1

input-output

(n bit)

input-output

(n bit)

Se a m word corrispondessero

m segnali di selezione, i segnali

di selezione sarebbero troppi.

Stefano Gregori

word m−2

Il decodificatore riduce il numero

dei segnali di selezione a

k = log2m

Memorie a semiconduttore

Crema, 22-5-2002

23

Decodificatore

2k linee

indirizzo

decodificatore

k bit

b0

b1

b2

esempio: k = 3

w0

w1

w2

w3

può essere realizzato con

2k porte AND a k ingressi

w4

w5

w6

w7

Stefano Gregori

Memorie a semiconduttore

Crema, 22-5-2002

24

Organizzazione

2D

indirizzo

decodificatore

k bit

indirizzo

di riga

linea dati

(bit line)

decodificatore di riga

k/2 bit

1D

linea di indirizzamento

(word line)

I/O

decodificatore di colonna

k/2 bit

indirizzo

di colonna

I/O

complessità decodificatore P = k·2k (k ingressi, 2k uscite)

complessità celle C = 2k (un interruttore per ogni cella)

P+C = (k+1) 2k

ad esempio con k=16, 2k=65536, P+C ≈ 106

Stefano Gregori

complessità decodificatori P = k·2k/2

complessità celle C = 2k+k/2

P+C = k·2k/2+2k+k/2

ad esempio con k=16, 2k=65536, P+C ≈7·104

Memorie a semiconduttore

Crema, 22-5-2002

25

Organizzazione a matrice

matrice di memoria

bit line

decodificatore di riga

(k−c) bit

word line

c bit

indirizzo

MAR

k bit

cella di memoria

decodificatore di colonna

sense amplifier e driver

MBR

n bit

input-output

Stefano Gregori

Memorie a semiconduttore

Crema, 22-5-2002

26

Organizzazione gerarchica

indirizzo

di riga

indirizzo

di colonna

indirizzo

di blocco

bus dati

sense amplifier

e driver

I/O

Vantaggi:

minore lunghezza delle linee di interconnessione all’interno dei blocchi

riduzione della potenza attivando un solo blocco

Stefano Gregori

Memorie a semiconduttore

Crema, 22-5-2002

27

Temporizzazione

ciclo di lettura

lettura

tempo di accesso

in lettura

ciclo di scrittura

scrittura

tempo di accesso

in scrittura

dato valido

dati

dato letto

buffer in

decodifica

Stefano Gregori

buffer out buffer in

decodifica

lettura

dato valido

dato scritto

scrittura

Memorie a semiconduttore

Crema, 22-5-2002

28

Temporizzazione

TEMPO D’ACCESSO: tempo che intercorre da

quando è scritto l’indirizzo a quando è disponibile il

dato

TEMPO DI CICLO: tempo che intercorre tra due

letture successive

indirizzi

tempo di ciclo

dati in uscita

tempo d’accesso

Stefano Gregori

Memorie a semiconduttore

Crema, 22-5-2002

29