Claudio Fratto

Laboratorio Sistemi

Esercitazione N°1

08-10-2007

LABORATORIO DI SISTEMI

ALUNNO: Fratto Claudio

CLASSE: IV B Informatico

ESERCITAZIONE N°: 1

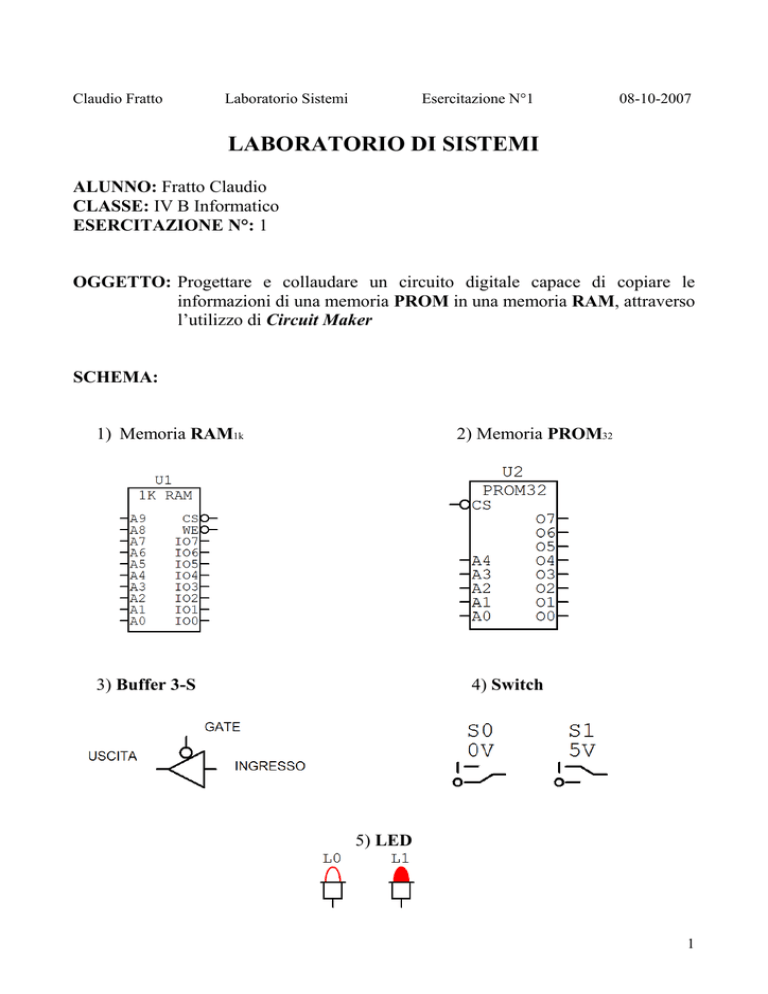

OGGETTO: Progettare e collaudare un circuito digitale capace di copiare le

informazioni di una memoria PROM in una memoria RAM, attraverso

l’utilizzo di Circuit Maker

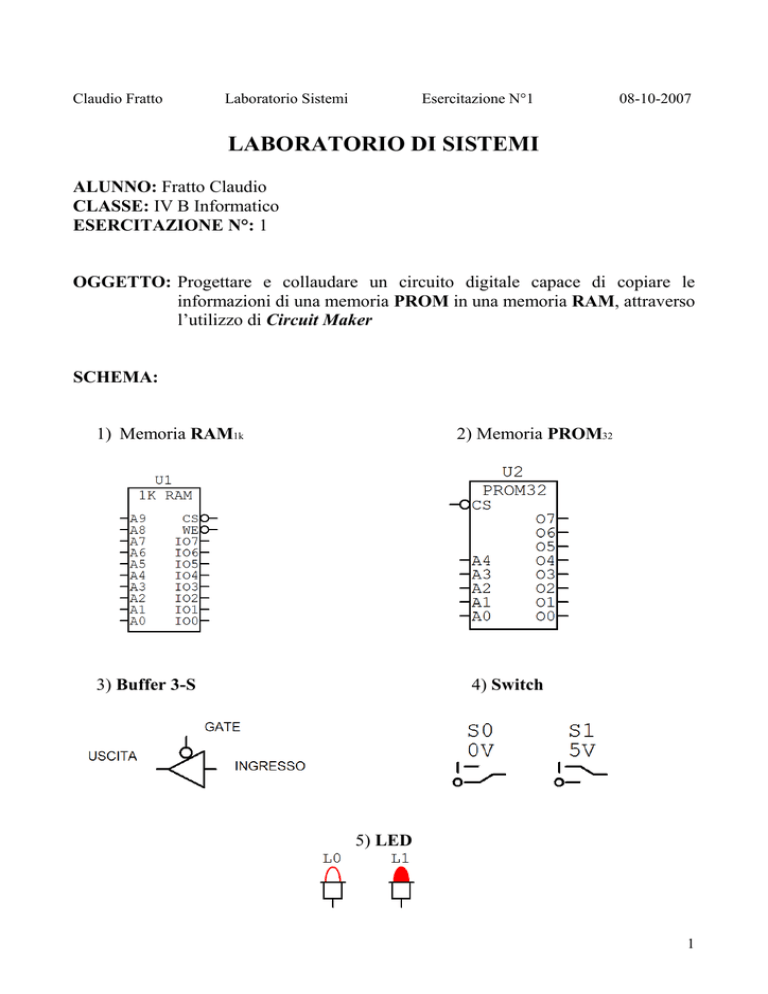

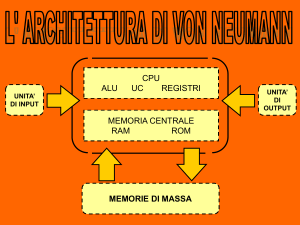

SCHEMA:

2) Memoria PROM32

1) Memoria RAM1k

3) Buffer 3-S

4) Switch

5) LED

1

Claudio Fratto

Laboratorio Sistemi

Esercitazione N°1

08-10-2007

6) Schema elettrico

2

Claudio Fratto

Laboratorio Sistemi

Esercitazione N°1

08-10-2007

RELAZIONE

L’esperienza effettuata in laboratorio si è articolata in due fasi:

1) la prima fase consisteva nel progettare e realizzare un circuito digitale capace di copiare il

contenuto di ogni singola locazione di memoria di un dispositivo PROM nelle rispettive

locazioni di memoria di un dispositivo RAM;

2) la seconda fase consisteva nel collaudare, per verificarne il corretto funzionamento, il

circuito progettato e realizzato nella prima fase.

•

TEORIA SULLE MEMORIE:

Le memorie sono dei dispositivi capaci di immagazzinare delle grandi quantità di dati in

formato digitale. Esse sono costituite da strutture, chiamate locazioni (ognuna delle quali è

contraddistinta da un proprio indirizzo sottoforma di un numero binario), che possono

contenere un numero finito di celle di memoria, ognuna delle quali è in grado di

memorizzare un singolo BIT (Binary digIT). Generalmente, nelle memorie che sono

attualmente in commercio, sono presenti delle locazioni che contengono 8 celle di memoria;

ogni singola locazione ci permette, quindi, di memorizzare un “parola”, cioè un’unità

informativa elementare (1 Byte).

Sulle memorie possono essere effettuate due operazioni, che sono di fondamentale

importanza per il loro utilizzo:

1) l’operazione di scrittura, cioè quella operazione che ci consente di memorizzare un

determinato dato in una determinata locazione di memoria;

2) l’operazione di lettura, cioè quella operazione che ci consente di recuperare, e quindi di

porle in uscita, le informazioni contenute in determinate locazioni.

Le memorie differiscono l’una dall’altra per la loro architettura, cioè differiscono nel modo

di accedere, tramite un indirizzo, ad una locazione di memoria. Per questo motivo esse

vengono classificate in:

a) memorie ad accesso sequenziale;

b) memorie ad accesso diretto;

c) memorie ad accesso ad indirizzo implicito.

Memorie Ad Accesso Sequenziale

Si ha una memoria ad accesso sequenziale, quando sia l’operazione di lettura che quella di

scrittura agiscono su un singolo dato alla volta. Nella fase di lettura viene messo in uscita il

dato contenuto nella locazione di memoria corrispondente all’indirizzo successivo a quello

dell’ultima locazione alla quale si ha avuto accesso; nella fase di scrittura l’informazione

viene immagazzinata nella locazione corrispondente all’indirizzo successivo a quello

dell’ultima locazione alla quale si ha avuto accesso.

Memorie Ad Accesso Diretto

Si ha una memoria ad accesso diretto, quando è possibile prelevare o immettere dati in

diverse locazioni di memoria, senza tener conto dell’indirizzo dell’ultima locazione alla

quale si ha avuto accesso. Questo tipo di memorie sono anche chiamate memoria ad

accesso casuale, perché esse non sono in grado di prevedere il futuro indirizzo a cui l’utente

vorrà accedere o per leggere o per scrivere.

3

Claudio Fratto

Laboratorio Sistemi

Esercitazione N°1

08-10-2007

Memorie Ad Accesso Ad Indirizzo Implicito

Si ha una memoria ad accesso ad indirizzo implicito, quando l’accesso viene effettuato

sempre alla stessa locazione di memoria; ciò fa si che soltanto una locazione di memoria sia

in collegamento con l’esterno. In questo tipo di memorie, nella fase di scrittura il dato

immesso dall’utente viene memorizzato nella locazione alla quale si può avere accesso;

contemporaneamente a questa operazione il dato contenuto nella locazione stessa viene fatto

scorrere, quindi memorizzato, nella locazione immediatamente successiva; nella fase di

lettura l’informazione viene prelevata dalla locazione alla quale si può avere accesso che,

una volta effettuata la lettura, viene occupata dall’informazione contenuta nella locazione di

memoria più prossima.

LE MEMORIE AD ACCESSO CASUALE

Le memorie ad accesso casuale si dividono, in base alle operazioni che si possono effettuare

con esse, in due categorie:

1) le memorie di sola lettura: ROM (Read Only Memory);

2) le memorie di lettura \ scrittura: RAM (Random Access Memory).

Nelle memorie di sola lettura, le informazioni sono inserite direttamente nella fase di

realizzazione del dispositivo. Esistono tuttavia dei dispositivi, appartenenti a questa

categoria di memorie, che possono essere programmati direttamente dall’utente. Questi

dispositivi vengono chiamati PROM (Programmable Read Only Memory).

Una caratteristica delle memorie di sola lettura è quella che le informazioni, una volta

scritte, non possono essere più rimosse. Esistono, in ogni modo, dei dispositivi ROM i cui

dati possono essere rimossi; questo tipo di memorie possono essere quindi riprogrammate.

Due memorie riprogrammabili sono:

a) le memorie EPROM (Erasable Programmable Read Only Memory), la cui fase di

cancellazione avviene proiettando, sulla superficie di silicio del dispositivo, raggi

ultravioletti. Una caratteristica di questo genere di memoria è quella che, per essere

riprogrammate, devono essere rimosse dalla scheda sulla quale si trovano;

b) le memorie EEPROM (Erasable Electrically Programmable Read Only Memory), la

cui fase di cancellazione avviene attraverso l’utilizzo di impulsi di tensione di valore e

durata prestabiliti. Questo genere di memorie possono essere riprogrammate

direttamente sulla scheda sulla quale si trovano.

Nelle memorie di lettura \ scrittura è possibile accedere ad una qualsiasi locazione, sempre

utilizzando un indirizzo binario, o per prelevare un dato (lettura) o per memorizzarne uno

(scrittura). La caratteristica di questo tipo di dispositivi è quella che, in fase di scrittura, il

nuovo dato che si va a memorizzare, si va a sovrascrivere a quello già presente nella

locazione.

4

Claudio Fratto

•

Laboratorio Sistemi

Esercitazione N°1

08-10-2007

MEMORIE E DISPOSITIVI UTILIZZATI NELL’ESPERIENZA

Le memorie utilizzate nell’esperienza sono state:

1) una memoria PROM 32 composta da:

a) un bus indirizzi ( cioè l’insieme delle linee sulle quali bisogna porre l’indirizzo,

sottoforma di numero binario, della locazione di memoria alla quale si vuole

accedere) formato da cinque pin (N° locazioni = 2^N° pin => 2^5 = 32 locazioni

disponibili);

b) un pin rappresentante il Chip Select (CS), cioè quel chip in grado di abilitare o

meno tutto il dispositivo;

c) un bus dati (cioè l’insieme delle linee sulle quali viaggiano, in binario, le

informazioni) formato da otto pin (N° massimo che la memoria poteva contenere

= 1111 1111(2) = 255(10) = FF(16));

2) una memoria RAM 1k formata da:

a) un bus indirizzi formato da dieci pin (N° locazioni = 2^10 = 1024 locazioni

disponibili);

b) un pin rappresentante il Chip Select (CS);

c) un bus dati formato da otto pin;

d) un bus di controllo (cioè l’insieme delle linee che permettono di regolare il

trasferimento dei dati) formato dal pin WE (Write Enable). Esso, secondo il suo

stato, consente di stabilire il tipo di operazione che si vuole effettuare sulla

memoria: se il suo stato è a livello basso, si abilita l’operazione di scrittura; se il

suo stato è a livello alto, si abilita l’operazione di lettura.

I dispositivi utilizzati nell’esperienza sono stati:

1) nove switch, cioè degli interruttori logici che ci consento di stabilire lo stato logico di un

pin; essi possono assumere due livelli logici: il livello alto (1), che corrisponde ad una

tensione pari a 5V, ed il livello basso (0), che corrisponde ad una tensione pari a 0V;

2) otto LED, cioè dei dispositivi capaci di convertire degli impulsi elettrici in impulsi

luminosi. Ognuno di essi, quando ricevono in ingresso un dato a livello alto, si

accendono; quando ricevono in ingresso un dato a livello basso, rimangono spenti;

3) otto Buffer 3-State, cioè dei dispositivi in grado di scollegare virtualmente alcune linee

di collegamento.

Il buffer 3-S è un sistema digitale che in uscita, oltre ai due livelli logici consueti (0 e 1),

può assumere un terzo stato: lo stato di alta impedenza. Esso è costituito da un ingresso,

da un’uscita e da un gate, che funziona in logica negativa. Se il gate è attivo,

l’informazione presente in ingresso è la stessa di quella presente in uscita; se il gate è

disattivato, il dispositivo si scollega virtualmente dal circuito facendo si che il dato in

ingresso non agisca più sull’uscita.

Sono stati utilizzati questi tipi di dispositivi per non far andare in conflitto l’uscita della

memoria PROM con l’ingresso \ uscita della memoria RAM.

5

Claudio Fratto

•

Laboratorio Sistemi

Esercitazione N°1

08-10-2007

FASE 1: PROGETTAZIONE E REALIZZAZIONE

Nella fase di progettazione si è valutato a priori le memorie ed i dispositivi da utilizzare per

arrivare a compimento dell’oggetto dell’esperienza. Una volta terminata la fase di

progettazione si è stati in grado di passare alla fase di realizzazione al PC, attraverso il

software di simulazione Circuit Maker. Per fare ciò si è messo sul banco di lavoro virtuale

tutto ciò che serviva per realizzare il circuito, prelevando ogni memoria ed ogni dispositivo

da una lista messa a disposizione dal software. Dopo quest’operazione, si è potuto

programmare la memoria PROM memorizzando un dato, sottoforma di numero binario, ad

ogni sua locazione di memoria.

In seguito si è collegato:

1) cinque switch ai rispettivi pin del bus indirizzi sia della PROM che della RAM (ES.

switch A0 ai pin A0 delle due memorie; switch A1 ai pin A1 delle due memorie; ecc.);

2) uno switch ai restanti pin del bus indirizzi della memoria RAM, inizializzandoli a 0;

3) uno switch al Chip Select della PROM;

4) uno switch al Chip Select della RAM;

5) uno switch al pin WE della memoria RAM;

6) le otto uscite della memoria PROM agli otto ingressi dei buffer 3-S (ES. pin O0

all’ingresso di B0; pin O1 all’ingresso di B1; ecc.);

7) le otto uscite dei buffer 3-S alle otto uscite della memoria RAM (ES. uscita di B0 al pin

I00; uscita B1 al pin I01; ecc);

8) gli otto gate dei buffer 3-S al WE;

9) le otto uscite della memoria RAM agli otto LED (ES. pin I00 a L0; pin I01a L1; ecc.).

Osservazione sul Buffer 3-S:

si è collegato il buffer 3-S in questo modo perché: se si impostava lo switch del WE allo

stato 1 (abilitando l’operazione di lettura della RAM) le linee di collegamento tra le uscite

delle due memorie dovevano essere disabilitate (per consentire ai LED di non essere

dipendenti dallo stato dei pin della PROM ma solo dallo stato dei pin della RAM). Per far

sì che ciò accadesse il gate del buffer 3-S doveva risultare disabilitato, ovvero doveva essere

allo stato 1.

Una volta finiti i collegamenti si è potuti passare alla fase di simulazione del circuito per

collaudarlo e verificare quindi il suo corretto funzionamento.

•

FASE 2: SIMULAZIONE DEL CIRCUITO E COLLAUDO

Per effettuare il collaudo con Circuit Maker, si è dovuto impostare il tipo di simulazione che

si intendeva effettuare (Digital Simulation). Dopo avere impostato la simulazione, è stato

attivato il comando RUN SIMULATION; si è potuto, così, interagire con la grafica del

software fornendo, attraverso gli interruttori collegati ai bus indirizzi delle due memorie,

tutti gli indirizzi possibili per accedere a tutte le locazioni di memoria. Ogni volta che si

combinavano gli switch, per copiare l’informazione contenuta nella PROM (corrispondente

all’indirizzo fornito dagli interruttori) nella RAM (con il medesimo indirizzo) si è dovuto

abilitare la scrittura della memoria portando l’interruttore del WE allo stato 0.

Per verificare il corretto funzionamento della fase di scrittura, dopo aver abilitato la fase di

lettura del dispositivo RAM, ponendo l’interruttore del WE allo stato 1, si è andati a

comparare il numero binario presente sul bus dati della RAM (ricavandolo attraverso la

lettura dei LED), di tutte le locazioni di memoria del dispositivo stesso, con il numero

binario immesso, nelle rispettive locazioni di memoria, durante la fase di programmazione

della PROM. Da questo controllo si è arrivati alla conclusione che tutti i dati sono stati

copiati con successo.

6