Politecnico

di Milano

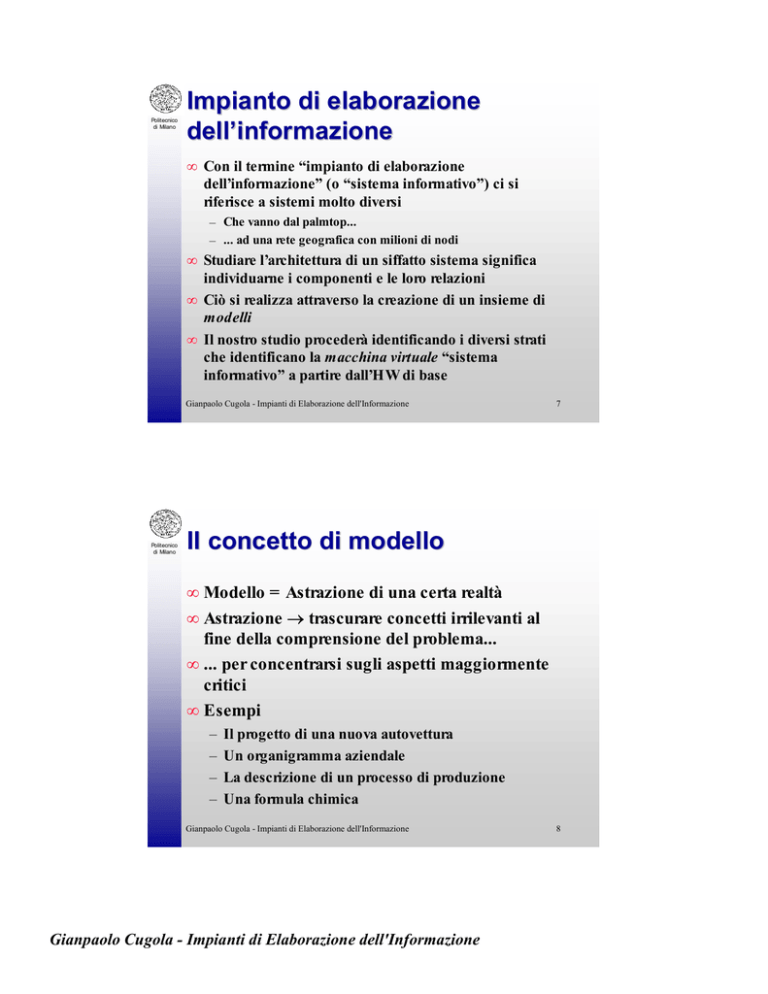

Impianto di elaborazione

dell’informazione

• Con il termine “impianto di elaborazione

dell’informazione” (o “sistema informativo”) ci si

riferisce a sistemi molto diversi

– Che vanno dal palmtop...

– ... ad una rete geografica con milioni di nodi

• Studiare l’architettura di un siffatto sistema significa

individuarne i componenti e le loro relazioni

• Ciò si realizza attraverso la creazione di un insieme di

modelli

• Il nostro studio procederà identificando i diversi strati

che identificano la macchina virtuale “sistema

informativo” a partire dall’HW di base

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Politecnico

di Milano

7

Il concetto di modello

• Modello = Astrazione di una certa realtà

• Astrazione → trascurare concetti irrilevanti al

fine della comprensione del problema...

• ... per concentrarsi sugli aspetti maggiormente

critici

• Esempi

–

–

–

–

Il progetto di una nuova autovettura

Un organigramma aziendale

La descrizione di un processo di produzione

Una formula chimica

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

8

Politecnico

di Milano

Il concetto di macchina virtuale

• Macchina virtuale = Esecutore “virtuale”

di algoritmi

• Con il termine “virtuale” si identifica la

caratteristica non reale

– N el qual caso si parla anche di “modello”

• O non “fisica” della macchina

• Esempi

– La macchina virtuale “Esecutore C”

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Politecnico

di Milano

9

Gli “strati” che compongono

un sistema informativo

Software applicativo

Software applicativo

Software di base (S.O.)

hardware

S.O. di rete + middleware

S.O.

hardware

S.O.

hardware

rete

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

hardware

10

Politecnico

di Milano

Tipologie di calcolatori - 1

• Esistono diversi tipi di calcolatori

– Handheld computer

• Di dimensioni molto limitate

• Usualmente privi di memorie di massa

– Personal computer

• Dotati di monitor e tastiera separati dall’unità

centrale

• Dotati di diversi dispositivi di memoria di massa

interni o esterni all’unità centrale

– N otebook

• Versione portatile del personal computer

• Usualmente dotata di caratteristiche inferiori in

termini di potenza di calcolo e memorizzazione

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Politecnico

di Milano

11

Tipologie di calcolatori - 2

– Workstation

• Versione “potente” dei personal computer

• Dotate di monitor di dimensioni superiori

• Per lo più orientate alle applicazioni grafiche

o di CAD

• Spesso condivise da più utenti (non

necessariamente in contemporanea)

– Mainframe

• Calcolatori di elevata potenza di calcolo e

memorizzazione

• Orientati all’elaborazione di dati per l’intera

azienda

• Condivisibili da più utenti in contemporanea

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

12

Politecnico

di Milano

Tipologie di S.O.

• N egli anni diversi S.O. hanno visto la luce

– I primi calcolatori non avevano un vero e proprio

S.O. ma solo un sottile strato di sw di base che

gestiva l’accesso all’hw

• Tipologie di S.O.

– Monoutente vs. multiutente

– Single tasking vs. multi tasking

• Principali S.O. oggi presenti sul mercato:

– DOS, Windows 9x, Windows N T, Unix (nei suoi

cento dialetti), OS/ 2, MacOS

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Politecnico

di Milano

13

Tipologie applicative

•

•

•

•

Applicazioni numeriche

Applicazioni gestionali

Applicazioni per l’automazione d’ufficio

Applicazioni telematiche

– Applicazioni di workgroup

• Applicazioni di automazione industriale

– CAD, CAM

• Applicazioni multimediali e di intrattenimento

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

14

Politecnico

di Milano

Architettura del calcolatore: il modello

di Von Neumann

• Tutte le diverse tipologie di calcolatori sono

accomunati dalla medesima architettura logica

• Schematizzata dal modello di Von N eumann

del calcolatore

Bus di sistema

Processore

(CPU)

Memoria

centrale

Interfaccia

delle

periferiche

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Politecnico

di Milano

15

Funzionamento della macchina di Von

Neumann

• Il processore estrae le istruzioni dalla memoria e le

esegue

– Le istruzioni possono comportare operazioni di manipolazione

dei dati

– Oppure operazioni di trasferimento dei dati

• I trasferimenti di dati attraverso elementi funzionali

diversi avvengono attraverso il bus di sistema

• Le fasi di elaborazione si susseguono in modo sincrono

rispetto ad un orologio di sistema

• Durante ogni intervallo di tempo l’unità di controllo

(parte del processore) stabilisce la funzione da svolgere

• L’intera macchina opera in maniera sequenziale

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

16

Politecnico

di Milano

Il processore: schema architetturale

Registro di stato

PC

A

Registro Istruz.

Corrente

B

ALU

segnali

di controllo

Ro

.....

Registro interr.

Rn

Registro dati

Unità di

controllo (UC)

Registro indirizzi

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Politecnico

di Milano

clock

17

Il processore: descrizione degli

elementi principali - 1

• Unità di controllo (UC) : decodifica le istruzioni e

controlla il funzionamento del sistema attraverso

opportuni segnali

• Unità aritmetico logica (ALU) : esegue le operazioni

aritmetiche

• Clock : sincronizza il funzionamento dei diversi

elementi

• Bus della CPU : collega i diversi elementi della CPU (da

non confondere con il bus di sistema)

• Program Counter (PC) : mantiene l’indirizzo della

prossima istruzione da eseguire

• Registro istruzione corrente : mantiene l’istruzione

attualmente in fase di esecuzione

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

18

Politecnico

di Milano

Il processore: descrizione degli

elementi principali - 2

• Registro delle interruzioni : indica l’avvenuta richiesta

di una interruzione

• Registro di stato : indica lo stato dell’ultima istruzione

eseguita dalla ALU

• Registro indirizzi : contiene l’indirizzo del prossimo

dato da leggere/ scrivere in memoria

• Registro dati : contiene l’ultimo dato letto o il prossimo

dato da scrivere in memoria

• Registri A e B : registri contenenti i dati su cui opera la

ALU

• Registri R0, ..., Rn : registri di uso generale

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Politecnico

di Milano

19

Il processore: funzionamento - 1

• L’esecuzione di un programma ha inizio con il

caricamento della locazione della prima istruzione nel

PC

• La UC manda un segnale di controllo affinché il

contenuto del PC sia spostato nel registro degli indirizzi

• Viene inviato un segnale di controllo (read) alla

memoria per effettuare la lettura del dato posto

all’indirizzo specificato nel registro indirizzi

• In conseguenza del passo precedente il dato viene reso

disponibile nel registro dati (la UC attende fino

all’arrivo del segnale MFC - memory function

completed)

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

20

Politecnico

di Milano

Il processore: funzionamento - 2

• La UC manda un segnale di controllo affinché il

contenuto del registro dati sia spostato nel

registro istruzione corrente

• La UC decodifica l’istruzione corrente

• La UC genera la sequenza di segnali di

controllo necessari ad eseguire l’istruzione

– Esempio:

caricamento di un dato presente in memoria nel

registro A

• Il valore del PC incrementato di 1 viene spostato nel registro

indirizzi

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Politecnico

di Milano

21

Il processore: funzionamento - 3

– Esempio (continua)

• Viene inviato un segnale di controllo (read) alla memoria

per effettuare la lettura del dato posto all’indirizzo

specificato nel registro indirizzi

• In conseguenza del passo precedente il dato viene reso

disponibile nel registro dati (la UC attende il segnale MFC)

• La UC manda un segnale di controllo affinché il contenuto

del registro dati sia spostato nel registro A

• Il PC viene incrementato al fine di puntare alla

prossima istruzione

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

22

Politecnico

di Milano

Il processore: tipologia di istruzioni

eseguibili

• Le istruzioni eseguite dal processore

possono essere classificate in tre

categorie principali:

– Istruzioni aritmetiche

• Somme, sottrazioni, moltiplicazioni, divisioni,

shift ecc.

– Istruzioni di salto condizionale

– Istruzioni di trasferimento dei dati

• Da un registro all’altro

• Da uno dei registri alla memoria o viceversa

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Politecnico

di Milano

23

Il processore: le interruzioni

• Al fine di gestire richieste provenienti dalle periferiche

può essere necessario interrompere la normale

esecuzione di un programma

• La periferica segnala sue particolari necessità attraverso

una interruzione

• Ad ogni passo di esecuzione la UC verifica lo stato del

registro delle interruzioni

• Se si è verificata una interruzione:

– Lo stato del processore (registri) viene salvato in memoria

– Viene attivata una speciale procedura di gestione delle

interruzioni

– Quando la procedura di gestione delle interruzioni termina lo

stato del processore viene ripristinato ed il programma viene

ripreso

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

24

Politecnico

di Milano

La memoria centrale - 1

• La memoria centrale è destinata ad accogliere dati e

programmi sui quali opera il calcolatore

• Concettualmente è composta da una sequenza di celle

ognuna delle quali contiene una parola (word )

– Ogni cella può essere acceduta direttamente (specificandone

l’indirizzo) per leggere o scrivere (in un unico passo) il valore

ivi contenuto

– Una parola è composta da un numero di bit che dipende dalla

macchina

• Esempio: Pentium: 32, 80286: 16, PowerPC: 32, Ultra SPARC: 64

– Le memorie in uso nei calcolatori moderni permettono

l’indirizzamento di un singolo byte oltre che di un’intera parola

(memorie byte-addressable)

• Un apposita linea di controllo del bus indica alla memoria se si

voglia accedere ad un’intera parola o ad un singolo byte

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Politecnico

di Milano

25

La memoria centrale - 2

• Il numero di bit che costituiscono l’indirizzo di un byte

all’interno della memoria è caratteristico del

microprocessore e identifica lo spazio di indirizzamento

del microprocessore

– Esempio: Pentium 32 bit

– Avendo a disposizione k bit è possibile indirizzare 2k byte

– Si ricorda che:

210 byte = 1 Kilo Byte

220 byte = 1 Mega Byte

230 byte = 1 Giga Byte

240 byte = 1 Tera Byte

• N ell’accesso ad una parola, il sistema di gestione delle

memorie byte-addressable considera solo i k-n bit più

significativi - dove n=sqrt(lungh. parola in byte)

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

26

Politecnico

di Milano

La memoria centrale - 3

• La memoria centrale si chiama usualmente ram o

memoria ad accesso casuale

– Viene cosi detta una memoria il cui tempo di accesso sia

indipendente dall’indirizzo della parola alla quale si vuole

accedere

– Si tratta di una memoria volatile

• Altri tipi di memoria presenti in un calcolatore sono le

rom

–

–

–

–

Hanno caratteristiche generali simili alle ram

Un tempo di accesso notevolmente maggiore

Si tratta di memorie permanenti

Sono tipicamente utilizzate per memorizzare quei dati e

programmi che servono al momento dell’accensione

dell’elaboratore, prima del caricamento del S.O.

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Politecnico

di Milano

27

Il bus di sistema

• Il bus di sistema collega tra loro i vari elementi del

calcolatore

• In ogni istante il bus è dedicato a collegare due unità,

una trasmette ed una riceve

– Il processore seleziona la connessione da attivare e indica

l’operazione da svolgere (bus mastering)

• Il bus è suddiviso in tre insiemi di linee:

– Bus dati

– Bus indirizzi

– Linee di controllo: trasportano informazioni relative alla

modalità di trasferimento e alla temporizzazione

• Esempio di uso del bus scrittura di un dato presente in

un registro del processore in memoria

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

28

Politecnico

di Milano

Bus sincroni e asincroni

• Bus sincrono:

– Le linee di controllo includono una linea di clock

– Periferica, memoria e processore operano sul bus in maniera

sincrona rispetto a tale “orologio” comune

• Durante ogni ciclo di bus può avvenire un singolo trasferimento

dati

• Bus asincrono

– Basato su handshake

– Le linee di controllo includono una linea ready ed una linea

accept

• La linea ready indica la richiesta di una operazione da parte

dell’unità master (processore) e viene tenuta a 1 fino al

completamento dell’operazione da parte dell’unità master

• La linea accept indica il completamento dell’operazione richiesta

da parte dell’unità slave e viene tenuta ad 1 fino a quando l’unità

slave non vede la transizione da 1 a 0 del segnale ready

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Politecnico

di Milano

29

L’interfaccia delle periferiche

• Concettualmente si occupa della gestione dello scambio

di dati tra processore e periferiche

• In generale contiene:

– Un registro dati della periferica (RDP)

– Un registro di comando della periferica (RCP)

– Un registro di stato

• Talvolta collegato al registro delle interruzioni del processore

• A seconda del processore, i registri delle periferiche

possono:

– Condividere lo spazio di indirizzi della memoria (memory

mapped I/ O)

– Adottare uno spazio di indirizzi distinti

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

30

Politecnico

di Milano

L’interfaccia delle periferiche:

schematizzazione grafica

Linee degli indirizzi

BUS

Linee dei dati

Linee di controllo

Decodificatore

degli indirizzi

Circuiti di

controllo

Registri dei dati

e di stato

Interfaccia di I/ O

Periferica

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Politecnico

di Milano

31

Interfacce standard

• E’ possibile avere una interfaccia diversa per ogni

periferica

– ma è più logico avere delle interfacce standard per periferiche

simili

• Esempi di interfacce standard:

–

–

–

–

–

–

–

Interfaccia seriale RS-232-C

Interfaccia PS2

Interfaccia USB (Universal Serial Bus)

Interfaccia parallela Centronix

Interfaccia ISA

Interfaccia SCSI

Interfaccia EIDE

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

32

Politecnico

di Milano

Gestione delle periferiche da parte del

processore - 1

• I moderni processori operano a velocità notevolmente

maggiori di ogni altra periferica

– Sorge la necessità di sincronizzare le operazioni di processore e

periferiche

• Due approcci possibili: a controllo di programma

(polling) o mediante interrupt

• La gestione a polling: un esempio di lettura da memoria

di massa

– Il processore invia sul bus il comando di lettura e si pone in

attesa che il dato sia disponibile sul registro dati della periferica

– Durante l’attesa il processore esegue un ciclo verificando il

valore del registro di stato della periferica

– Appena il dato è pronto il processore lo trasferisce dal registro

dati della periferica in uno dei suoi registri interni e da qui in

memoria

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Politecnico

di Milano

33

Gestione delle periferiche da

parte del processore - 2

• Difetti dell’approccio a polling

– Il processore resta impegnato in un ciclo in attesa del dato

• La gestione a interrupt: un esempio di lettura da

memoria di massa

– Il processore invia sul bus il comando di lettura e procede nelle

sue operazioni

– Quando il dato è disponibile la periferica “solleva” un

interruzione

– Il processore interrompe le sue operazioni, salva il proprio stato

ed esegue una opportuna routine di gestione delle interruzioni

(parte del S.O.)

– La routine di gestione delle interruzioni verifica che un dato è

disponibile sulla periferica e lo trasferisce dal registro dati della

periferica in uno dei registri interni del processore e da qui in

memoria

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

34

Politecnico

di Milano

Periferiche: memorie di massa

• Con il termine memoria di massa ci si riferisce ad un dispositivo di

memorizzazione permanente capace di contenere grosse quantità

di dati

• Esiste un numero grandissimo di dispositivi di tale tipo

• Possibili categorizzazioni

– Dispositivi ad accesso sequenziale o casuale

– Dispositivi in sola lettura (RO), in lettura e scrittura (RW) o WORM

(Write Once Read Many)

– Dispositivi magnetici, ottici o magneto-ottici

• Dimensioni tipiche delle principali memorie di massa odierne

–

–

–

–

–

FDD: 1.44 MB

CD: 650 MB

DVD: 4 GB

H ard-Disk: 4÷

÷30 GB

N astri: QIC80: 350 MB, DAT 4÷

÷20+ GB

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Politecnico

di Milano

35

Memorie di massa: HD - 1

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

36

Politecnico

di Milano

Memorie di massa: HD - 2

• Schema di memorizzazione

(creato in fase di formattazione

di basso livello)

– Ogni superficie è divisa in

tracce concentriche

• In ogni traccia i dati sono

memorizzati in maniera

sequenziale

– Ogni traccia è divisa in settori

– L’insieme delle tracce omologhe

poste sulle diverse facce è detto

cilindro

• Esempio: il disco IBM Deskstar

25GP

– 5 dischi, 10 testine, 15.302

cilindri (utente), 512 byte per

settore

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Politecnico

di Milano

37

Memorie di massa: HD - 3

• Caratteristiche prestazionali di un HD

– Tempo di posizionamento (seek time): il tempo necessario a

posizionare le testine sulla traccia richiesta

• N ell’ordine di 8-10 ms

– Tempo di latenza o di rotazione (latency time): il tempo

affinché il settore richiesto “passi” sotto la testina (dipende

dalla velocità di rotazione del disco)

• N ell’ordine di 2-4 ms

– Tempo di trasferimento: il tempo per trasferire i dati dal disco

alla memoria

• In genere trascurabile

– Tempo di accesso (la somma dei tre tempi precedenti)

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

38

Politecnico

di Milano

Memorie di massa: HD - 4

• Esempi:

– Il disco IBM Deskstar 25GP (EIDE)

• Caratteristiche costruttive: 25 GB disposti su 5 dischi (10

testine) suddivisi in 15.302 cilindri (utente) con 512 byte per

settore. 5400 rpm

• Caratteristiche prestazionali:

– Tempo di posizionamento: 9.0 ms (2.2 ms track-to-track)

– Tempo di latenza: 5.56 ms

– Il disco Seagate Cheetah ST118202LW (UW SCSI 2)

• Caratteristiche costruttive: 18 GB disposti su 12 dischi (24

testine) con 512 byte per settore. 10000 rpm

• Caratteristiche prestazionali:

– Tempo di posizionamento: 5.2 ms

– Tempo di latenza: 2.99 ms

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Politecnico

di Milano

39

Memorie di massa: gli array di

dischi

• Per aumentare le prestazioni dei sistemi a disco

è possibile raggruppare più dischi in un sistema

RAID (Redundant Array of Inexpensive Disks)

• Il sistema RAID suddivide ogni file in blocchi

registrati su dischi diversi per aumentare le

prestazioni (data striping)

• Il sistema RAID viene anche utilizzato per

incrementare l'affidabilità dei sistemi a disco

attraverso un meccanismo di ridondanza

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

40

Politecnico

di Milano

Periferiche: terminali

• Caratterizzati da una tastiera, un video e,

talvolta, un mouse o altri dispositivi di

puntamento simili

• N ei PC e nelle workstation tali dispositivi sono

integrati nello stesso calcolatore

• Video: caratteristiche salienti

–

–

–

–

Dimensione: misura della diagonale in pollici

Risoluzione: dimensione in pixel x pixel

Dot pitch: dimensione del singolo punto in mm

Frequenza di refresh ad una certa risoluzione:

misurata in hz

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Politecnico

di Milano

41

Periferiche: stampanti

• Permettono di stampare su carta i dati prodotti

al calcolatore

• Caratteristiche salienti:

– Velocità: in ppm

– Risoluzione: in punti per pollice (DPI)

• Principali tipi di stampanti:

–

–

–

–

A margherita (solo testo)

Ad aghi

A getto di inchiostro

Laser

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

42

Politecnico

di Milano

Estensioni alla macchina di

Von Neumann

• Uso di processori dedicati

• Uso di meccanismi di pipelining per

parallelizzare le attività all’interno del

singolo processore

• Uso di gerarchie di memorie

• Uso di canali di DMA per la gestione

dell’I/ O

• Uso di bus multipli

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Politecnico

di Milano

43

I processori dedicati

• All’interno di un moderno calcolatore esistono, in realtà,

numerosi processori che svolgono funzioni specifiche:

– Processori per la gestione dei canali di I/ O

– Processori grafici

• 2D e 3D

– Processori per la sintesi e l’acquisizione di suoni

• Taluni di questi processori possono essere anche molto

complessi

– Il chip grafico 3dfx III è composto da 8.2 milioni di transistor

(il Pentium II ne ha 7.5)

• I diversi processori operano sotto il controllo del

processore centrale con il quale “competono” per

l’accesso alla memoria e al bus

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

44

Politecnico

di Milano

Le pipeline - 1

• Il principio della catena di montaggio:

– Decomporre una attività complessa che si debba ripetere

sempre eguale in più attività semplici...

– ... e parallelizzare tali attività semplici

• Applicazioni ai processori:

– L’esecuzione di una istruzione può essere decomposta in un

certo numero di attività più semplici

– Da eseguire in parallelo per le diverse istruzioni che

compongono il programma

– Ogni stadio della pipeline esegue una di queste attività

elementari

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Politecnico

di Milano

45

Le pipeline - 2

• Il problema dei salti

– N el caso di salti condizionali non esiste un unica sequenza di

istruzioni

– Soluzione: la branch prediction

• Il problema della dipendenza dei valori

– L’esecuzione di un’istruzione può dipendere dal risultato della

precedente, ciò riduce la possibilità di eseguire le due istruzioni

in parallelo

– Soluzione: l’esecuzione fuori ordine

• Un esempio: il processore PowerPC 620

– Due pipeline distinte per operazioni intere e in virgola mobile

• Formate da 4 stadi la prima e 6 la seconda

– Fino ad un massimo di 4 istruzioni per ciclo di clock

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

46

Politecnico

di Milano

Le memorie cache

• Il problema:

– Le memorie non reggono più la velocità dei moderni processori

• Una memoria PC100 ha un tempo di accesso dell’ordine dei 7 ns,

insufficiente per processori moderni (500 Mhz)

– E’ possibile costruire memorie più veloci ma a costi molto alti

(memorie statiche)

• La soluzione:

– Una gerarchia di memorie via via meno veloci e più capienti

processore

cache interna

al processore (L1)

cache di secondo

livello (L2)

Memoria

principale

bus

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Politecnico

di Milano

47

Memoria cache: un esempio pratico

• Un caso pratico: un moderno PC con Pentium

II 400

– Cache L1:

• 32 Kb interna al processore

• Operante a piena frequenza (400 Mhz)

– Cache L2

• 512 Kb sulla scheda che ospita il processore

• Operante a frequenza pari alla metà del processore (200

Mhz)

– Memoria:

• 32-512 Mb sulla scheda madre

• Operante alla frequenza del bus esterno alla CPU (100 Mhz)

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

48

Politecnico

di Milano

I canali DMA - 1

• Problema:

eseguire le operazioni di I/ O sotto lo stretto controllo del

processore richiede risorse di calcolo

– Il processore deve richiedere il dato (singola parola) all’interfaccia

delle periferiche, attendere la disponibilità del dato, leggerlo e

spostarlo in memoria

– Il problema viene in parte risolto attraverso l’uso di interrupt, ma

ancora la lettura è svolta un dato per volta

• Soluzione:

i controllori DMA integrati nelle interfacce delle periferiche

– Il controllore DMA integrato nell’interfaccia si occupa di trasferire in

maniera autonoma i dati richiesti dal processore in memoria (a

blocchi)

– Il processore viene informato quando tutti i dati richiesti sono stati

trasferiti (attraverso un’interrupt)

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Politecnico

di Milano

49

I canali DMA - 2

• Effetto dell’uso del DMA

– Diversi dispositivi possono accedere

autonomamente al bus

• Il processore

• I controllori DMA

– Di conseguenza si possono manifestare dei

conflitti nell’uso del bus

– Tali conflitti vengono risolti attraverso un

meccanismo di arbitraggio del bus

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

50

Politecnico

di Milano

Le architetture a bus multipli

• I moderni calcolatori contengono spesso più bus

– Uno o più bus del processore (il caso del Pentium II)

– Uno o più bus al quale collegare schede di espansione (es. ISA,

PCI, AGP)

– Uno o più bus delle periferiche (Es. EIDE, SCSI, USB)

• I diversi bus operano spesso a frequenze diverse sotto il

controllo del processore

– Concettualmente si tratta sempre di un unico bus ma suddiviso

in più “tratti” operanti a velocità differente

• Opportuni processori di controllo (Es. chipset della

scheda madre) si occupano di gestire i passaggi di dati

tra i diversi bus

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Politecnico

di Milano

51

Un moderno PC x86: schema

architetturale

processore

cache L1

processore

video

scheda video

RAM

video

cache L2

RAM

bus AGP

bus esterno

bus PCI

bus ISA

controller dischi

(EIDE o SCSI)

controller

periferiche

scheda PCI

bus dischi

scheda ISA

H D1

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

...

H Dn

CD

52

Politecnico

di Milano

Una scheda madre socket 7

ZIF socket 7 batteria tampone

slot ISA

ROM BIOS

cache L2

chipset

slot PCI

slot AGP

bus fdd

slot

DIMM

slot

SIMM

presa

tastiera

alimentazione

bus EIDE

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Politecnico

di Milano

53

Una scheda madre slot 1

slot 1

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

54

Politecnico

di Milano

Una scheda madre dual slot 1

slot 1

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Politecnico

di Milano

55

Alcuni processori x86

Celeron 400

socket 370

Celeron 400

slot 1

PII 400

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

56

Politecnico

di Milano

Caratteristiche architetturali di

alcuni processori x86 - 1

•

Intel 486

•

8 registri interni a 32 bit

8 kbyte cache L1 unificata

1 istruzione per ciclo di clock

Clock interno: 33, 66 e 100 Mhz

Bus esterno 33 Mhz

1.2 - 1.8 (DX4) milioni di

transistor

– 1 - 0.8 micron

•

Intel Pentium MMX

–

–

–

–

–

–

8 registri interni a 32 bit

16+16 kbyte cache L1

2 istruzioni per ciclo di clock

Clock interno: fino a 300 Mhz

Bus esterno 66 Mhz

3.5 milioni di transistor (0.35 µ)

Intel Pentium II

registri interni a 32 bit

16+16 kbyte cache L1

3 istruzioni per ciclo di clock

Clock interno: fino a 450 Mhz

Cache L2 integrata nel package

(512 Kbyte operanti alla metà

della frequenza del clock interno)

– Bus esterno 100 Mhz

– 7.5 milioni di transistor (0.25 µ)

–

–

–

–

–

–

–

–

–

–

–

•

Intel Celeron “mendocino”

– Come sopra ma con 128 Kbyte di

cache L2 “on die” operanti a

piena frequenza...

– ... e bus esterno a 66 Mhz

– Disponibile in versione slot 1 o

socket 370

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Politecnico

di Milano

57

Caratteristiche architetturali di

alcuni processori x86 - 2

• Intel Pentium III

– Come Pentium II ma con

un set esteso di istruzione

(KN I)

– Annunciato anche in

tecnologia 0.18 µ e bus

esterno a 133 Mhz

• IBM PowerPC 750

–

–

–

–

–

–

• AMD K6-2

–

–

–

–

–

–

–

registri interni a 32 bit

32+32 kbyte cache L1

3 istruzioni per ciclo di clock

Clock interno: fino a 450 Mhz

Bus esterno 100 Mhz

9.300.000 transistor (0.25 µ)

Dispone di un set di istruzioni

supplementare (3DN ow!)

architettura RISC

registri interni a 32 bit

32+ 32 Kbyte cache L1

4 istruzioni per ciclo di clock

Clock interno fino a 400 Mhz

Bus cache L2 operante alla

metà della velocità del

processore (fino a 1 MB)

– 6.350.000 transistor (0.22 µ)

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

Gianpaolo Cugola - Impianti di Elaborazione dell'Informazione

58