Testo di riferimento:

appunti

Le memorie dinamiche

01.c

Classificazione

Organizzazione

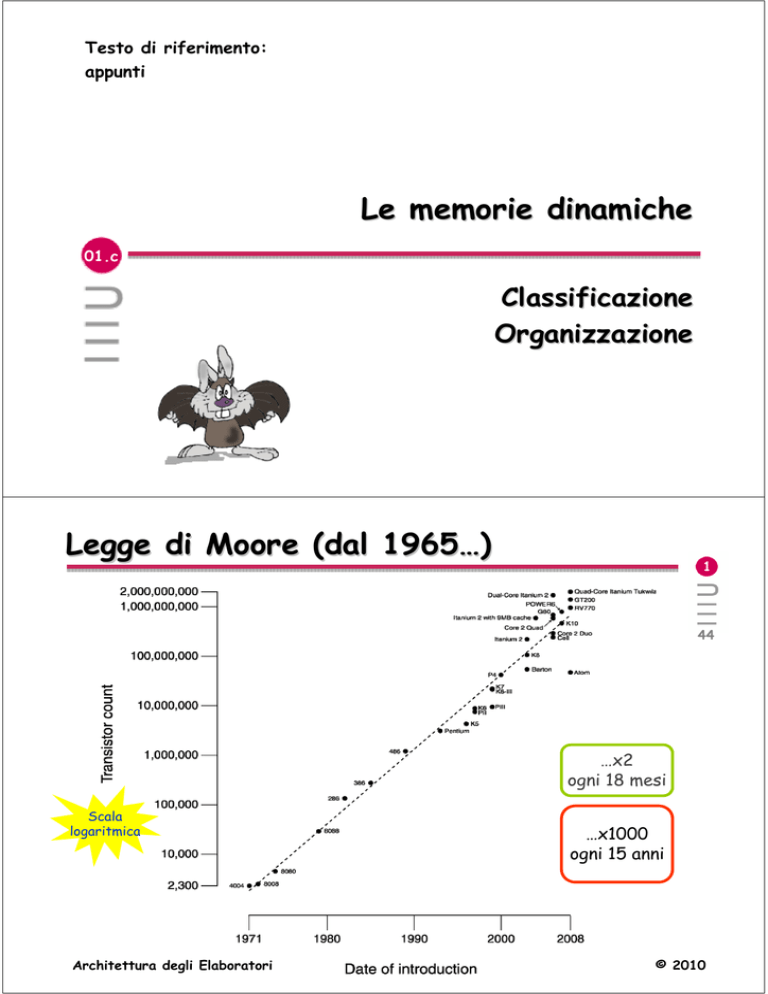

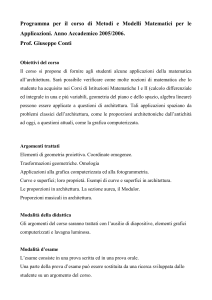

Legge di Moore (dal 1965…)

1

44

…x2

ogni 18 mesi

Scala

logaritmica

Architettura degli Elaboratori

…x1000

ogni 15 anni

© 2010

Legge di Moore per la cella DRAM?

2

Processor - DRAM Memory Gap

“Moore’s Law”

10000

CPU

Processor-Memory

Performance Gap:

(grows 50% / year)

100

Less’ Law?

DRAM

Year

04

20

02

20

00

20

98

19

96

19

94

19

92

19

90

19

88

19

86

19

84

19

82

19

80

1

19

Performance

44

µProc: 60%/yr. (2X/1.5yr)

1000000

DRAM: 9%/yr. (2X/10 yrs)

Architettura degli Elaboratori

© 2010

Come aumentare le prestazioni?

3

1. Aumentando il numero di bit per accesso (es.: con un

bus dati da 64 bit si trasferiscono 8 byte per volta)

● svantaggi: aumentano le dimensioni, aumenta la

corrente

44

2. Aumentando il grado di parallelismo interno delle

operazioni (es. memory interleaving: con più banchi di

memoria è possibile avviare un accesso ad un altro

banco, prima che sia completato l’accesso precedente)

3. Evitando di eseguire alcune delle operazioni (ad es. la

selezione di una riga già selezionata)

Architettura degli Elaboratori

© 2010

Classificazione delle DRAM

4

Interfaccia asincrona (DRAM “standard”):

● il processore deve attendere, in uno stato idle,

il completamento dell’operazione in memoria.

44

Interfaccia sincrona (SDRAM):

● le operazioni sono in sincronia con clock del bus;

con l'uso di opportuni latch si aumenta il parallelismo

con la CPU (bus oltre i 66MHz).

Interfaccia basata su protocollo (RDRAM):

● indirizzi e dati vengono trasmessi in parallelo

con modalità pipelined sul medesimo bus.

Architettura degli Elaboratori

Interfaccia asincrona (DRAM)

© 2010

5

In un’interfaccia asincrona il processore attende il

tempo necessario per il completamento di ciascuna

44

operazione (invio di RAS dopo che l’indirizzo di riga è

stabile; invio di CAS dopo che l’indirizzo di colonna è

stabile; successivo trasferimento del dato).

L’attivazione di RAS trasferisce, in appositi latch dati, il

contenuto di tutti i bit della riga selezionata.

Se un ciclo di clock inizia prima che sia trascorso il

tempo richiesto per l’operazione, occorre attendere

l’inizio del successivo ciclo di clock per poter iniziare

l’operazione successiva.

Tenendo presente questo vincolo, i tempi per il

trasferimento di un dato sono indicati in termini di

numero di cicli di clock.

Architettura degli Elaboratori

© 2010

Accesso per righe in una DRAM

6

4096 righe,

512 colonne,

dati da 8 bit.

44

indirizzo

di colonna

indirizzo

di riga

chip DRAM da 2 MB (16 Mbit)

la selezione di una riga rende accessibili 512 byte

Architettura degli Elaboratori

Logica negata (si presta al wired-or O.C.)

© 2010

7

44

Y = A1•B1 • A2•B2 • A3•B3

(De Morgan)

Y = A1•B1 + A2•B2 + A3•B3

Architettura degli Elaboratori

© 2010

Ciclo di lettura in una DRAM

T1

T2

T3

Clock

Indirizzo

T5

T6

T7

tc

riga

44

riga

colonna

1. Memorizza indirizzo di

riga; legge la riga e la RAS

memorizza nei latch dati

2. Memorizza indirizzo

di colonna

T4

8

ta

CAS

5. Trasferimento del dato

letto; fine del ciclo.

3. Refresh della riga

(ricopia nella riga

Dout

i bit dai latch dati) 4. Dato valido

dato

il ciclo di lettura tc (indicato anche con tRC) è di 6 periodi di clock;

il tempo di accesso ta (indicato anche con tRAC) è di 4 periodi (tc>ta);

con clock a 66 MHz (Tc=15ns) si avrebbe: tc = 90 ns, ta = 60 ns;

la velocità di una DRAM è spesso definita dal tempo di accesso ta.

© 2010

Architettura degli Elaboratori

Ciclo di refresh in una DRAM

T1

T2

T3

T4

9

T5

T6

44

Clock

Indirizzo

riga

RAS

1. Memorizza indirizzo di

riga; legge la riga e la

memorizza nei latch dati

2. Refresh della riga

(ricopia nella riga

i bit dai latch dati)

Architettura degli Elaboratori

© 2010

Ciclo di scrittura in una DRAM

T1

T2

T3

T4

10

T5

T6

Clock

Indirizzo

44

riga

colonna

riga

1. Memorizza indirizzo di

riga; legge la riga e la RAS

memorizza nei latch dati

2. Invio del dato

Din

3. Write Enable

WE

dato

2. Memorizza indirizzo di

colonna e modifica, nei CAS

latch dati, il bit da scrivere

4. RAS alto: ricopia, dai latch dati, la riga modificata

5. CAS alto: termina il ciclo di scrittura

Architettura degli Elaboratori

© 2010

Fast Page Mode (FPM) DRAM

11

È un esempio della strategia 3): sfrutta il fatto che accessi

consecutivi spesso interessano colonne successive della stessa riga.

RAS\ rimane attivo per un intero ciclo di riga (=“pagina”): basta

fornire l’indirizzo di riga una sola volta all’inizio dell’accesso.

44

Ogni ciclo di CAS\ include: impostazione dell’indirizzo di colonna,

attivazione di CAS\, attesa del dato in uscita, latch del dato,

refresh, disattivazione di CAS\ (necessaria per segnalare il

termine del ciclo).

Timing: indica il numero di cicli di clock necessari per il primo

accesso a un dato della riga, seguito da quelli per gli accessi ai dati

successivi nella medesima riga.

Valori tipici per FPM: 6-3-3-3 o 5-3-3-3 con celle da 70 ns o 60 ns

(bus a 66 MHz).

Architettura degli Elaboratori

© 2010

Fast Page Mode: temporizzazioni

tRCD

tPC

12

= RAS to CAS delay = 3 Tc

= page (CAS) cycle = 3 Tc

tPC

44

tPC

timing:

5-3-3-3

Tc

tRCD

tCAC

tRAC

clock

il primo dato della riga è disponibile

con un ritardo (tRAC) di 5 Tc dopo RAS\

i dati successivi sono

disponibili ogni 3 Tc

Architettura degli Elaboratori

FPM: temporizzazioni in dettaglio

© 2010

13

44

Architettura degli Elaboratori

© 2010

Extended Data Output (EDO) DRAM

14

Vengono aggiunti dei latch dati che mantengono

il dato appena letto, consentendo di anticipare

la disattivazione di CAS\ e l’invio dell’indirizzo

della colonna successiva.

Si può così ridurre il periodo tPC del segnale

CAS\ dopo il primo accesso: il segnale CAS\

rimane disattivato per il minimo intervallo di

tempo.

44

Timing: 5-2-2-2 o 5-3-3-3 con celle da 50..70 ns

(bus a 66 MHz)

© 2010

Architettura degli Elaboratori

EDO DRAM: temporizzazioni

15

44

tCAC

= column access time

Architettura degli Elaboratori

tPC

= page (CAS) cycle

© 2010

EDO DRAM: temporizzazione in dettaglio

16

44

Architettura degli Elaboratori

© 2010

SIMM (Single In-line Memory Module)

17

DRAM 4M x32 - 72 pin SIMM (Micron), chip 4Mx4

44

DRAM 8Mx32, chip 4Mx4 su entrambe le facce

Architettura degli Elaboratori

© 2010

SIMM - 2

4Mx32 DRAM - 72 pin SIMM (Micron)

18

44

Architettura degli Elaboratori

Evoluzione dei moduli SIMM

• 30 pin, DB da 8 bit (primi anni ’90)

● per fornire 16 bit alla volta (286, 386 SX)

occorrevano 2 moduli giustapposti

● per fornire 32 bit alla volta (386 DX)

occorrevano 4 moduli giustapposti

© 2010

19

44

• 72 pin, DB da 32 bit (metà anni 90)

● con l’avvento del Pentium e del bus PCI

● per fornire 64 bit alla volta (Pentium)

occorrevano 2 moduli giustapposti

Architettura degli Elaboratori

© 2010

Evoluzione dei moduli SIMM → DIMM

20

DIMM (Dual In-line Memory Module):

● una schedina su cui sono collocati i chip di memoria,

44

caratterizzata da un bus dati da 64 bit;

● i moduli DIMM hanno ormai sostituito i moduli SIMM

(Single In-Line Memory Module), nei quali il bus dati è

da 32 bit;

● nei moduli SIMM (72 pin), i contatti sulle 2 facce

della scheda sono uniti e formano un contatto unico;

nei DIMM (168 pin), i contatti opposti sono

elettricamente isolati e formano 2 contatti separati;

● le attuali DDR3 usano DIMM da 240 pin e DB da 128

bit

ECC (Error Correction Codes):

● un chip in più contenente bit aggiuntivi per consentire

la correzione di errori sui dati memorizzati.

Architettura degli Elaboratori

© 2010

Interfaccia sincrona (SDRAM)

21

Dopo l’accesso al primo dato di una riga, anziché attendere l’invio

degli indirizzi di colonna successivi, questi vengono generati

internamente alla DRAM con semplici incrementi (burst counter).

44

Le operazioni interne della DRAM sono strettamente regolate dal

clock, che è l’unico segnale di temporizzazione da fornire per i dati

della riga successivi al primo.

Più comandi possono essere accodati (pipelining): si ottengono così

prestazioni migliori e si possono usare bus a frequenze più elevate.

Il tempo per l’accesso al primo dato (SDRAM latency) è maggiore di

quello per i dati successivi della stessa riga (CAS latency).

SDRAM latency e CAS latency sono ancora espresse in numero di

cicli di clock: 5-1-1-1 (SDRAM Latency = 5, CAS Latency = 1).

La CAS latency è determinata dal column access time tCAC. Le

specifiche JEDEC prevedono valori di CAS latency pari a 1, 2, o 3.

Architettura degli Elaboratori

© 2010

JEDEC Synchronous DRAM (SDRAM)

22

JEDEC = Joint Electron Devices Engineering Council (1958)

Dal 1993 definisce i tipi base di DRAM sincrona.

44

Caratteristiche:

● interfaccia sincrona;

● architettura a banco multiplo: consente di avviare un accesso

ad un altro banco, prima che sia completato l’accesso

precedente (su un banco diverso);

● burst mode.

Una volta selezionata la riga, CS\, RAS\, CAS\, WE\ codificano

il comando da eseguire (sincronizzato dal clock).

Un registro “programmabile” di modo stabilisce:

● il tipo (sequential o interleaved) e le modalità di burst;

● la lunghezza del burst (1 bit, 2 bit, 4 bit, …);

● la CAS latency (1, 2 o 3).

Architettura degli Elaboratori

SDRAM: diagramma a blocchi

© 2010

23

44

Architettura degli Elaboratori

© 2010

SDRAM: esempio di architettura interna

SDRAM 4Mb (512 KB)

divisa internamente in

2 banchi 512x256x16

24

44

ind. di riga: 10 bit

(A9 seleziona banco,

A8..A0 → 512 righe)

ind. di colonna: 8 bit

(A7..A0 → 256 col)

Architettura degli Elaboratori

SDRAM: lettura SDRAM

© 2010

25

44

Architettura degli Elaboratori

© 2010

SDRAM: comando READ

26

44

Architettura degli Elaboratori

SDRAM: CAS latency

© 2010

27

44

Architettura degli Elaboratori

© 2010

CAS latency: determinazione

28

All’inizio di un ciclo di lettura burst viene impostato

l’indirizzo di riga e, nel successivo fronte di salita del

clock, vengono attivati i segnali RAS\ e CS\. Ciò avvia

il recupero dell’intera riga selezionata.

Trascorso un tempo pari a tRCD (RAS\ to CAS\ delay),

nel successivo fronte di salita del clock può essere

attivato CAS\.

44

Trascorso un ulteriore tempo pari a tCAC (column access

time), il primo dato è leggibile sulle linee d’uscita.

Perché tutto funzioni deve essere:

CASLatency * tCLK ≥ tCAC

Architettura degli Elaboratori

© 2010

SDRAM: evoluzione

29

SDR (Single Data Rate) SDRAM PC100

● Specifiche Intel per sistemi con bus a 100 MHz

● Timing 4-1-1-1

44

DDR (Double Data Rate) SDRAM

● L’output ha luogo su entrambi i fronti del clock

● Frequenze di clock fino a 200 MHz

DDR-2 SDRAM

● Aumenta la dimensione della minima unità di lettura/scrittura;

questo vincolo permette ottimizzazioni, con clock fino a 400 MHz.

DDR-3 SDRAM

● Ulteriore raddoppio della minima unità di lettura/scrittura, e

quindi della frequenza di clock (400÷800 MHz)

Enhanced SDRAM (ESDRAM)

● SDRAM con una porzione di cache statica on-chip

(fino a 200 MHz)

Architettura degli Elaboratori

© 2010

Caratteristiche delle DDR SDRAM

30

44

Architettura degli Elaboratori

Timing per SDRAM DDR-n

• misurati in periodi di system clock

• 4 valori

● tCL

CAS latency

tempo tra comando READ e

dato disponibile in uscita

● tRCD

RAS to CAS delay

tempo tra comando ACTIVE e

comando READ/WRITE

● tRP

Row Precharge

tempo tra comando PRECHARGE e

comando ACTIVE

● tRAS

Row Active time

tempo tra un comando ACTIVE e un

comando PRECHARGE

© 2010

31

44

es: DDR3 OCZ HPC1333 standard PC3-10600

(3/2008)

Clock 1.333 MHz

timing 6-5-5-20

Architettura degli Elaboratori

© 2010

32

44

Architettura degli Elaboratori

© 2010

33

44

Architettura degli Elaboratori

© 2010

Interfaccia basata sul protocollo

34

Indirizzi (row e col) e dati vengono trasmessi

in parallelo con modalità pipelined sul medesimo bus

(mentre nelle SDRAM gli indirizzi seguono percorsi

diversi da quelli dei dati).

44

RDRAM (Rambus DRAM), DRDRAM (Direct Rambus DRAM)

● Soluzione proprietaria (Rambus Inc.)

● Adotta un approccio diverso rispetto a DDR e DDR2:

anziché usare bus dati con molte linee, usa un bus

da 16 bit con una elettronica progettata in modo da

assicurare alte frequenze operative

● I dati sono trasferiti su entrambi i fronti del clock

(come DDR)

● Data rate fino a 1.6 GB/s (standard PC800) e 2.1 GB/s

(standard PC1066)

Architettura degli Elaboratori

© 2010

Principali produttori di DRAM – 3Q 2009

35

44

(ROK)

(ROK)

(J)

(USA)

(Taiwan)

(Taiwan)

(Taiwan)

(Taiwan)

(Taiwan)

I primi 4 produttori detengono più dell’80% del mercato!

Il mercato delle memorie DRAM è molto dinamico …

Architettura degli Elaboratori

© 2010

Principali produttori di DRAM – Q1 2008

36

44

• Nel 2007 è iniziato un sensibile calo delle entrate dovuto a sovrapproduzione

• Nel 2009 Qimonda (D) (ex Infineon) è fallita ed ha cessato la produzione, in

parte rilevata dalla rivale Micron.

© 2010

Architettura degli Elaboratori

Principali produttori di semiconduttori

Revenue

(million

$ USD)

2009/2008

changes

Market

share

USA

32 095

-5.0%

14.2%

South Korea

17 123

+1.3%

7.6%

10 640

-4.0%

4.7%

9 612

-13.2%

4.2%

8 400

-18.6%

3.7%

USA

6 475

0.0%

2.9%

Hynix

South Korea

5 940

-1.4%

2.6%

6

Renesas Technology

Japan

5 664

-19.3%

2.5%

9

12

AMD

USA

5 038

-7.6%

2.2%

10

7

Sony

Japan

4 670

-32.8%

2.1%

11

11

NEC

Japan

4 403

-24.4%

1.9%

12

10

Infineon

Germany

4 340

-27.1%

1.9%

13

14

Broadcom

USA

4 198

-9.6%

1.9%

14

16

Micron Technology

USA

3 995

-9.9%

1.8%

15

24

MediaTek

Taiwan

3 524

+21.7%

1.6%

16

19

Elpida Memory

Japan

3 498

-2.8%

1.5%

17

13

Freescale

USA

3 344

-32.7%

1.5%

18

15

Panasonic

Japan

3 330

-25.6%

1.5%

19

17

NXP

Netherlands

3 247

-19.9%

1.4%

20

18

Sharp

Japan

2 886

-20.0%

1.3%

Top 20

142 422

-10.7%

62.8%

All Other companies

84 313

-15.2%

37.2%

TOTAL

226 735

-12.4%

100.0%

Rank

2009

Rank

2008

Company

1

1

Intel Corporation

2

2

Samsung Electronics

3

3

Toshiba

Japan

4

4

Texas Instruments

USA

5

5

STMicroelectronics

France

6

8

Qualcomm

7

9

8

Architettura degli Elaboratori

Country of origin

Italy

37

44

© 2010

Sviluppo tecnologico

38

44

Architettura degli Elaboratori

© 2010

Sviluppo tecnologico nelle DRAM

39

TECNOLOGIA

(anno) ’90 ’95

’00

’05

09

(μm) 0.35 - 0.25 - 0.22 - 0.18 - 0.15 - 0.13 - 0.11 –(nm) 90 – 60 - 45

(wafer) 200mm

300mm

(chip) 4Mb 16Mb 64Mb 256M

1G

2G

4G

44

DENSITÀ DEI CHIP DRAM

64 Mb $2-3 | $0.25/Mbyte

128 Mb $3-5 |

256 Mb $4-7 (0.18-0.13 μm)

512 Mb in produzione, 0.13 - 0.11 μm

1 Gb

in produzione, 0.11 μm - 90 nm

4 Gb

30/1/09: SAMSUNG annuncia DDR3 DRAM chip da 4Gb (50nm)

Architettura degli Elaboratori

© 2010

Capacità dei chip di DRAM

40

1G

106 Kb

256M

44

105

64M

16M

104

4M

1M

103

256K

102

64K

16K

10

1977

1980

1983

1986

1989

1992

1995

1998

2001

Legge di Moore (x 4 ogni 3 anni)

2004

© 2010

Architettura degli Elaboratori

Capacità e Velocità dei chip di DRAM

DRAM:

Disk:

Capacity

4x in 3 years

4x in 3 years

Speed (latency)

2x in 10 years

2x in 10 years

DRAM

Year

Size

19801000:1! 64 Kb 2:1!

1983

256 Kb

1986

1 Mb

1989

4 Mb

1992

16 Mb

1995

64 Mb

Architettura degli Elaboratori

2007

41

44

Cycle Time

250 ns

220 ns

190 ns

165 ns

145 ns

120 ns

© 2010

Sviluppi futuri → memorie non volatili

42

Potranno sostituire le attuali NAND Flash, ma anche le DRAM:

• PRAM (PCRAM) (Phase Change RAM): sfruttano le proprietà 44

di una lega calcogenura (Ge2Sb2Te5), in grado di cambiare

fase (cristallina o amorfa) in modo controllato elettricamente;

• FRAM (FeRAM) (Ferroelettric RAM): usano uno strato di

materiale ferroelettrico il cui stato è controllabile da un

campo elettrico;

• MRAM (Magnetoresistive RAM): usano uno strato di

materiale ferromagnetico il cui stato è controllabile da un

campo magnetico;

• NRAM (Nano-RAM): sfruttano la proprietà dei nanotubi di

carbonio di cambiare posizione meccanica (toccarsi o non

toccarsi) in modo controllato elettricamente.

Architettura degli Elaboratori

Magnetoresistive RAM (MRAM)

© 2010

43

● Ancora allo stato sperimentale

44

● Per memorizzare i dati utilizzano la polarità di minuscoli

elementi magnetici, anziché la presenza o l’assenza di cariche

elettriche (come avviene nelle DRAM)

● Non volatili: i dati non scompaiono quando manca l’alimentazione

● Nel giugno 2003 IBM e Infineon hanno presentato un chip

MRAM da 128Kbit, costruito con tecnologia da 0.18 µm

● Con memoria MRAM non volatile un calcolatore potrebbe essere

avviato istantaneamente all’accensione, con il sistema operativo

già presente in memoria

● Le memorie dei primi calcolatori (1950-1960) erano costituite

da nuclei di ferrite (non volatili): forse le RAM future saranno

basate sullo stesso principio fisico, pur con dimensioni

decisamente più ridotte

Architettura degli Elaboratori

© 2010

MRAM (IBM)

44

44

Architettura degli Elaboratori

© 2010

Fine

01.c

Le memorie dinamiche