Architettura del Calcolatore

Appunti per la cl. IV sez. D a cura

del prof. Ing. Mario Catalano

1

Modello di Von Neumann

L’architettura del moderno microcomputer

ha radici che risalgono agli anni ‘40.

Il Matematico ungherese John Von

Neumann (1903-1957) ha sviluppato un

modello di computer che ancor oggi è

utilizzato per la descrizione degli

elaboratori

2

Il Von

modello

Neumann divise

l’hardware del computer

nelle seguenti parti:

CPU

Input

Output

Working Storage

(archiviazione

temporanea)

Permanent Storage

Applicando il modello di

Von Neumann al

personal computer

odierno otterremo uno

schema come in figura:

3

Il modello di Von Neumann

CPU

MEMORIA

CENTRALE

INTERFACCIA

I/O

PERIFERICHE

4

Architettura Studiata

Bus di controllo

DMA

Bus di indirizzi

ROM

RAM

Clock

CPU

Interrupt

BIOS

Bus di dati

Controller

dischi,

CD-ROM,etc.

Connettori

Periferiche

I/O

Bus di I/O

5

Cosa è un BUS?

È un mezzo di trasmissione pubblico dei dati

Fisicamente è composto da più connettori che collegano

fra loro più circuiti e permettono loro lo scambio di dati.

I dati possono essere trasmessi in modo seriale

(bastano pochi conduttori) o parallelo (serve un

conduttore per ciascun bit della parola)

Nei bus paralleli, spesso, i conduttori che trasmettono i

dati (linee dati) sono separati da quelli che trasmettono

gli indirizzi (linee indirizzi).

Sempre i segnali di controllo sono trasmessi su

connettori dedicati.

Il protocollo di trasmissione è definito da un circuito

detto Bus Controller

6

I componenti di un elaboratore: BUS

I bus all’interno del computer sono linee di trasmissione che

collegano le varie unità funzionali del computer

Si dividono in

Bus Interni (per es. Interni alla CPU)

Bus Esterni (solitamente standardizzati)

7

Circuiti di Temporizzazione (Clock)

T

tempo

Il megahertz (MHz) è l'unità di misura della frequenza alla quale

il processore funziona;

indica quanti milioni di oscillazioni al secondo (1 oscillazione al

secondo = 1 hertz [Hz]) sono generate dal clock.

f=1/T Hz.

8

Circuiti di Temporizzazione (Clock)

In generale il clock é prodotto da un

apposito circuito integrato, la cui

oscillazione é controllata da un cristallo di

quarzo.

Il cristallo di quarzo garantisce una elevata

stabilita nel tempo e con il variare della

temperatura ed una grande precisione nel

valore della frequenza prodotta, quanto

meno

possibile

influenzato

dalla

temperatura e dall' invecchiamento.

9

Circuiti di Temporizzazione (Clock)

Ogni area

processore

necessita di

generato in

principale.

del PC che contiene un

o

un

microcontrollore,

un clock, che puó essere

loco o dipendere dal clock

Giá a partire dalle CPU 80486, é diventato

comune avere per il processore un clock

piú elevato di quello generale del sistema.

10

CPU-Principi di Base

STRUTTURA DELLA ISTRUZIONE MACCHINA: Si tratta di

una stringa binaria che identifica il codice della operazione

da eseguire e le modalità per indirizzare gli operandi

FASI CPU: Ricerca (Fetch) e Esecuzione (Execute)

ESECUZIONE DI UNA ISTRUZIONE MACCHINA:

l’esecuzione di un’istruzione avviene con una sequenza di

microistruzioni a livello circuitale associate all'istruzione

(ciascuna determina il posizionamento dei segnali elettrici

in un ciclo di clock)

RISC: il set istruzioni è composto da poche istruzioni di

base, della stessa dimensione e con lo stesso tempo di

esecuzione

CISC: il set di istruzioni è composto da molte istruzioni di

dimensioni diverse e con tempi di esecuzione diversi 11

CPU-Memoria Cache

La memoria, a rigore, non dovrebbe far parte

dell'unità centrale ma attualmente una

tendenza che si va consolidando e quella di

fornire CPU che presentino al loro interno

banchi di memoria allo scopo di reperire

velocemente informazioni, senza dover

accedere alla memoria centrale.

Cache di Primo Livello L1 (alcune volte

anche la L2 e L3)

12

CPU-Registri Interni

Di numero e di caratteristica molto differenziate, i registri

interni di lavoro permettono all'unità centrale lo spostamento,

la manipolazione ed il deposito temporaneo dei dati senza

dover ricorrere alla memoria esterna.

I tipi di registri, le modalità di interconnessione e di

comunicazione fra i vari registi sono una caratteristica del

processore

Possiamo tuttavia individuare un set di registri essenziali per il

funzionamento di un qualunque processore, e che, dunque,

possono essere ritrovati in una qualunque architettura.

13

CPU-Registri Interni

Memory Address Register (MAR). E' il registro specializzato per

indirizzare la memoria. Durante l'esecuzione di un programma il MAR

contiene l'indirizzo della locazione di memoria centrale (esterna alla CPU)

alla quale si vuole accedere in quell'istante.

Program Counter (PC). E' il registro specializzato per contenere l'indirizzo

dell'istruzione che deve essere eseguita.

Memory Data Register (MDR). E' il registro da cui transitano tutti i dati

scambiati con la memoria esterna prima di venire smistati, in base al loro

significato, presso gli altri registri interni.

Instruction Register (IR). E' il registro che contiene la parte codice

operativo di un'istruzione, vale a dire quella sequenza di bit che

opportunamente decodificati determineranno le azioni che la CPU deve

14

eseguire.

CPU-Registri Interni

Accumulatore. E' il principale registro di calcolo dell'unità

centrale: contiene sempre uno degli operandi e il risultato

dell'operazione

Pointer Registers (PRs). Sono registi specializzati per contenere

indirizzi, solitamente di quei sotto programmi ricorrenti con particolare

frequenza. Alcuni di essi possono venire specializzati a funzioni

particolari.

Uno di essi è lo stack pointer, che indirizza la zona di RAM in cui è

stato costruito lo stack. Lo stack e' definita come una porzione di

memoria gestita secondo una politica LIFO (Last In First Out).

Risulta estremamente comodo per il salvataggio del program

15

counter in caso di interruzione (interrupt) o subroutine; CPU-Registri Interni

Status Register. Con registro di stato si intende un registro il cui

contenuto è costituito da un insieme di flag aventi un significato

individuale, anche se può essere manovrato ed elaborato in parallelo.

Il significato dei vari flags costituenti il registro può differire a seconda

del microprocessore, ma avremo sempre alcuni flags fondamentali:

CARRY. Viene manipolato dalle operazioni aritmetiche; viene

settato o resettato nel corso di un'istruzione di somma se si è

avuto o no un riporto.

OVERFLOW. Risente anch'esso dell'esito delle operazioni

aritmetiche; viene settato a uno se nel corso di una somma o

sottrazione si è avuto un trabocco della capacità dei registi.

16

CPU-Unità Aritmetico Logica ALU

Operazioni Aritmetiche: Somma in Complemento a 2

Operazioni Logiche: AND, OR e NOT

Operazioni sui Bit: Shift e Rotazione

Dati in Ingresso: il Contenuto dell'Accumulatore (sempre) e

dei registri interni della CPU (operandi residenti in memoria

centrale vengono appoggiati su registri temporanei)

Risultato dell'Operazione: Accumulatore

Uscite Collaterali: è fondamentale registrare alcune

condizioni di fine esecuzione delle operazioni di ALU al

fine di determinare se procedere con la successiva

istruzione in memoria o con un’altra opportunamente

specificata.

risultato zero, negativo, riporto, overflow ……

registro di stato 17

CPU-Instruction Decoder and Control

E' il cuore del processore

Riceve come dato in ingresso il codice operativo dell'istruzione

presente nell'instruction register (IR).

Questo codice può essere pensato come l'indirizzo di partenza

di un microprogramma interno che agisce a livello circuitale

minimo componendo insieme, in modo opportuno, gruppi di

microistruzioni.

Queste ultime consistono in definitiva nell'emissione di una

serie di segnali e stati logici di controllo che servono:

a predisporre la ALU a compiere una particolare funzione

aritmetico logica

a smistare attraverso i bus interni i contenuti dei registri

interessati

a svolgere i necessari test e gli eventuali scambi di dati con

18

l'esterno.

CPU-Instruction Decoder and Control

Esempio di Microprogramma associato all'istruzione di Somma del

contenuto dell'accumulatore con il contenuto del MDR.

Questa operazione può essere scomposta in sette passi elementari:

1. Trasferimento del contenuto dell'accumulatore sul bus dati interno

alla CPU.

2. Trasferimento del contenuto del bus dati nella ALU.

3. Trasferimento del contenuto del MDR sul bus dati interno alla CPU.

4. Trasferimento del contenuto del bus dati nella ALU.

5. Attivazione della logica di somma.

6. Trasferimento del contenuto della ALU (risultato della somma) sul

bus dati.

7. Trasferimento del contenuto della data bus nell'accumulatore (che

conterrà il risultato della somma).

19

CPU - Fasi di Fetch e Execute

In qualunque processore l'esecuzione di una generica

istruzione avviene in due fasi differenti:

la fase di ricerca (FETCH): consiste nel prelievo dalla

memoria centrale dell'istruzione

la fase di esecuzione (EXECUTE), caratterizzata dalla

decodifica

dell'istruzione

e

dall'attivazione

del

microprogramma ad essa associato.

20

CPU - Fasi di Fetch e Execute

Esempio: Supponiamo che l'istruzione sia di somma fra il

contenuto dell'accumulatore e il contenuto di una cella di

memoria il cui indirizzo sia dato direttamente dalla parte

operando dall'istruzione stessa.

Supponiamo cioè che la cella di memoria contenente

l'istruzione da eseguire sia strutturata come segue:

codice istruzione

indirizzo RAM del secondo operando

21

CPU - Fasi di Fetch e Execute

Fase di ricerca (FETCH):

1. Il contenuto del Program Counter (PC) è relativo

all’indirizzo di memoria che contiene l’istruzione.

2. Il contenuto del Program Counter è inviato al MAR

(Memory Address Register) per operare il prelevamento

dell'istruzione all'indirizzo di memoria contenuto nel MAR.

3. Il dato prelevato dalla memoria è riposto nel MDR (Memory

Data Register).

4. Il contenuto del MDR, ossia l’istruzione, è messa nel

Instruction Register per essere decodificata.

5. Il Program Counter viene incrementato per puntare

all'istruzione successiva. 22

CPU - Fasi di Fetch e Execute

Ha inizio a questo punto la fase di esecuzione (EXECUTE):

1. viene compreso che il secondo operando risiede in memoria

2. la parte dell’istruzione relativa all’indirizzo del secondo operando

viene trasferita nel MAR

3. L'effettivo operando, prelevato dalla memoria è posto nel MDR.

4. L’operando viene presentato ad un ingresso della ALU.

5. All'altro ingresso

dell'accumulatore.

dell’ALU

viene

presentato

il

contenuto

6. L'ALU, predisposta dall'Instruction Register ad eseguire la somma,

pone il suo risultato nell'accumulatore.

La fase di esecuzione è terminata ed il processore prosegue con la

fase di ricerca dell'istruzione successiva.

23

Esecuzione delle istruzioni

Ciclo Fetch–Decode–Execute

(leggi–decodifica–esegui)

1. Prendi l’istruzione corrente dalla memoria e mettila nel

registro istruzioni (IR).

2. Incrementa il program counter (PC) in modo che

contenga l’indirizzo dell’istruzione successiva.

3. Determina il tipo dell’istruzione corrente (decodifica).

4. Se l’istruzione usa una parola in memoria, determina dove

si trova.

5. Carica la parola, se necessario, in un registro della CPU.

6. Esegui l’istruzione.

7. Torna al punto 1 e inizia a eseguire l’istruzione successiva.

24

Ciclo Fetch–Decode–Execute

Fetch

Decode

Execute

25

Fetch dell’istruzione

0000

PO

CU

R0

R1

R2

R3

SR

0001

RAM

PC

IR

ALU

…..

0001

0001

ADD R3 R0 R1

0002

…

…

0005

…

0009

…

…

…

Address Bus

Data Bus

Control Bus

PC (Program Counter): indirizzo IR (Instruction Register):

di memoria della cella contenente

l’istruzione da eseguire

istruzione da eseguire dopo il fetch

26

Fetch dell’istruzione : IR ← M [PC]

RAM

CU

R0

R1

R2

R3

SR

0001

0000

PO

PC

IR

ALU

…..

0001

read!

0001

ADD R3 R0 R1

0002

…

…

0005

…

0009

…

…

…

Address Bus

Data Bus

Control Bus

PC (Program Counter): indirizzo IR (Instruction Register):

di memoria della cella contenente

l’istruzione da eseguire

istruzione da eseguire dopo il fetch

27

Fetch dell’istruzione

0001

R0

R1

R2

R3

SR

0002

ADD R3 R0 R1

0000

PO

CU

PC

IR

RAM

ALU

0002

0002

…

…..

…

0009

…

…

…

Address Bus

ADD R3 R0 R1

La CU incrementa automaticamente

il PC (PC ← PC +1)

…

0005

0001

read

ADD R3 R0 R1

Data Bus

Control Bus

IR (Instruction Register):

contiene l’istruzione da eseguire

dopo il fetch

28

Decodifica dell’istruzione

PO

CU

R0

R1

R2

R3

SR

0002

ADD R3 R0 R1

PC

IR

ALU

…..

L’istruzione dell’esempio non richiede altri accessi in memoria

La CU decodifica l’istruzione attraverso il codice operativo e

trasmette alla PO gli ordini per eseguire

l’operazione(microordini).

In assenza di interrupt o di salti sarà prelevato il contenuto

29

Esecuzione dell’istruzione

PO

CU

SR

0003

ADD R3 R0 R1

3

4

R0

R1

R2

R3

PC

IR

7

…..

ALU

La PO esegue l’operazione.

Le informazioni sullo stato dell’elaborazione

sono memorizzate in SR (Status Register):

flag Z (zero), V (overflow), N (negative), CY

(carry).

30

Un esempio : ADD 2, R1 (fetch 1)

Indirizzo della istruzione

memoria

Bus

controllo

000..01

40

Bus

indirizzo

Bus dati

40

M

A

R

M

D

R

IC

PC

PSW

Esegui

Parte controllo

Registro/i coinvolti

R0

R1

R2

...

R16

codifica

Operazione

ALU

Registri

generali

Esito

Processore

31

Un esempio : ADD 2, R1 (fetch 2)

Indirizzo della istruzione

memoria

Leggi!

41

40 000..01

IC

40

Bus

indirizzo

Bus dati

PC

PSW

Esegui

Parte controllo

Registro/i coinvolti

MAR

M

D

R

R0

R1

R2

...

R16

codifica

Operazione

ALU

Registri

generali

Esito

Processore

32

Un esempio : ADD 2, R1 (fetch 3)

memoria

41

40 000..01

Operazione

PC

PSW

Esegui

000110000100100001

IC

Parte controllo

Bus

indirizzo

Registro/i coinvolti

MAR

Bus dati

MDR

R0

R1

R2

...

R16

ALU

Registri

generali

Esito

Processore

33

Un esempio : ADD 2, R1 (dec)

memoria

41

40 000..01

PC

add

PSW

Esegui

000110000100100001

IC

Parte controllo

Bus

indirizzo

Registro/i coinvolti

MAR

Bus dati

MDR

R0

R1

R2

...

R16

ALU

Registri

generali

Esito

Processore

34

Un esempio : ADD 2, R1 (exe 1)

memoria

41

40 000..01

PC

add

PSW

Esegui

000110000100100001

IC

Parte controllo

Bus

indirizzo

Registro/i coinvolti

MAR

Bus dati

MDR

00010

R1

R2

...

R16

ALU

Registri

generali

Esito

Processore

35

Un esempio : ADD 2, R1 (exe 2)

memoria

41

40 000..01

PC

add

PSW

Esegui

000110000100100001

IC

Parte controllo

Bus

indirizzo

Registro/i coinvolti

MAR

Bus dati

MDR

00010

34

R2

...

R16

ALU

Registri

generali

Esito

Processore

36

Un esempio : ADD 2, R1 (exe 3)

memoria

41

40 000..01

PC

PSW

000110000100100001

IC

Parte controllo

Bus

indirizzo

Registro/i coinvolti

MAR

Bus dati

MDR

00010

36

R2

...

R16

ALU

Registri

generali

Esito

Processore

37

Processori

CISC

CISC (Complex Instruction Set Computer)

•

micro-programmazione: istruzioni ‘interpretate’ dal

micro-programma

•

istruzioni complesse che richiedono piu’ cicli di

clock per essere eseguite

•

formato variabile, molteplici tipi di istruzioni

•

molteplici modalita’ di indirizzamento della memoria

•

pochi registri

•

es.: Intel: per IBM, 8086, 286, 386, 486, Pentium e

Pentium PRO

38

Processori

RISC

RISC (Reduced Instruction Set Computer)

•

nessuna micro-programmazione: istruzioni

‘interpretate’ direttamente dall’HardWare

•

istruzioni semplici che richiedono un solo ciclo di

clock per essere eseguite

•

formato fisso, pochi tipi di istruzioni

•

pochi modalita’ di indirizzamento della memoria:

solo le istruzioni LOAD e STORE possono

accedere alla memoria

•

molti registri

39

Tecnologie di fabbricazione dei microprocessori.

Il Packaging: il contenitore in cui è

incapsulato il chip della CPU deve avere

ottime caratteristiche meccaniche e

termiche; si usano ceramiche

particolari.

La Piedinatura: l’aumento della

memoria indirizzabile, del parallelismo di

trasferimento con la memoria centrale,

delle funzionalità avanzate hanno

determinato un crescente numero di

punti esterni di connessione (pin).

40

Tecnologie di fabbricazione dei

microprocessori.

Il Raffreddamento: le sempre maggiori

potenze impegnate richiedono ventole

montate su CPU e su chassis più potenti e

controlli automatici di temperatura

Il Socket: il socket è l’elemento

meccanico di interconnessione tra il chip e

la scheda madre.

41

BIOS

Il nome BIOS significa Basic Input Output System,

ossia sistema di base per ingressi e uscite.

Il BIOS è essenzialmente un "software", ossia un

programma. Esso é contenuto in un chip di memoria non

volatile

EEPROM o le Flash Memory.

Le funzioni svolte dal BIOS sono essenzialmente tre:

1. Funzione di Avvio del Computer, all'interno della

quale viene eseguito il POST (Power-On Self Test).

2. Funzione di Memorizzazione di Configurazione

Hardware e di Parametri del ChipSet.

3. Interfaccia del Sistema Operativo.

42

BIOS

Avvio del Computer

Quando si accende il PC, si inizializza l'alimentatore

interno. Non appena la tensione si stabilizza il chipset

invia un comando di reset del processore.

Il comando reset richiede alla CPU di eseguire

l'istruzione posta sempre in una locazione fissa

prestabilita nella ROM del BIOS e denominata

indirizzo di jump.

La CPU esegue l'istruzione, che copia in memoria i

programmi del BIOS e inizia l'esecuzione del BIOS.

43

BIOS

Avvio del Computer

La prima azione eseguita dal programma di BIOS è il

POST (Power-On Self-Test):

Il

processo POST verifica e controlla la

configurazione

hardware

memorizzata

nelle

informazioni di configurazione del BIOS.

Nel caso in cui dovesse rilevare un problema invia

indicazioni acustiche per mezzo di uno o più beep o

beep code, attraverso l'altoparlante del sistema, per

indicare la natura del problema o visualizzare un

messaggio d'errore e il processo di boot si arresta.

Se il POST non incontra problemi, il processo di boot

continua.

44

BIOS

Avvio del Computer

Il BIOS cerca il BIOS dell'adattatore video e lo attiva.

Quasi tutti i dispositivi periferici di un PC dispongono di un

proprio BIOS. Le informazioni sulla scheda video sono

visualizzate sullo schermo del monitor.

informazioni della scheda video, BIOS della scheda

video, produttore e versione.

Vengono

inizializzate la routine del BIOS delle

periferiche presenti, oltre la scheda video.

Il BIOS effettua poi una serie di test nel sistema,

inclusa la dimensione della memoria rilevata.

Un

contatore progressivo visualizza nello

45

schermo la memoria rilevata e verificata.

BIOS

Avvio del Computer

Il BIOS verifica che i dispositivi elencati nei dati di

configurazione siano presenti e funzionanti.

viene visualizzato un messaggio che comunica

che il dispositivo è stato trovato, configurato e

verificato.

Se il BIOS supporta la tecnologia PnP (Plug and

Play), qualsiasi dispositivo PnP rilevato sarà

configurato.

vengono visualizzate sullo schermo tutte le

informazioni dei dispositivi, tuttavia scorrono in

modo troppo veloce per poter essere lette.

46

BIOS

Avvio del Computer

Alla fine della sequenza di test e configurazione, il

BIOS visualizzerà una schermata che riassume i

dettagli del PC verificati dal BIOS, per indicare che il

sistema è pronto per l'uso.

Il BIOS dovrà trovare il sistema operativo ed essere

in grado di accedervi, per poterlo attivare.

I dati di configurazione memorizzati nel BIOS

contengono un parametro che indica le unità

disco (floppy, hard disk o CD-ROM) e l'ordine di

accesso per il caricamento del sistema operativo.

47

BIOS

Avvio del Computer

Se il programma di boot non viene trovato nel primo dispositivo

elencato, verrà ricercato nel dispositivo successivo e così via;

se non si trova alcun dispositivo di boot la relativa sequenza si

arresta e viene visualizzato un messaggio di errore: "Non è

disponibile alcun dispositivo di boot".

Il BIOS memorizza la configurazione hardware del

computer (periferiche non plug&play) e i parametri del

chipset e ne permette all’utente la modifica.

Programma di Configurazione: tasto DEL all'avvio

In genere ogni versione di BIOS permette di

intervenire su taluni parametri del chipset ma non su

altri.

48

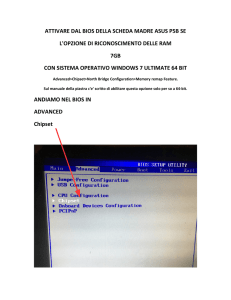

BIOS

Memorizzazione Configurazione

Esempio: alla voce Chipset Features Setup (o Advanced

Chipset Setup) e possibile intervenire sui tempi di accesso

alla memoria e su altri parametri del chipset, così da

migliorare anche sensibilmente le prestazioni del computer;

C'è il rischio di impostare alcuni parametri troppo

performanti per l'hardware installato e il sistema si

bloccherà durante il funzionamento:

basterà rientrare nel Setup del BIOS (premendo, in genere,

il tasto DEL all'avvio) e reimpostare i valori

precedentemente usati.

49

BIOS

Interfaccia Sistema Operativo

L'hardware, cioè la parte elettronica del PC, può presentare

notevoli differenza da costruttore a costruttore o da modello

a modello.

Se il S.O. deve ad esempio recuperare un file dal disco

rigido, esegue tale lettura "chiedendo" al BIOS di leggere il

file, senza occuparsene direttamente.

Il BIOS contiene programmi usati dal sistema operativo e

software applicativo per interagire con l'hardware.

Visto che il BIOS è strettamente legato all’hardware, è facile

comprendere è che ogni diverso computer possiede un

diverso BIOS.

Non è possibile cioè utilizzare il BIOS del computer modello

50

x nel computer modello y.

Produttori di BIOS

Award,

AMI (America Megatrends, Inc.) e Phoenix producono i

BIOS più noti.

Come la maggior parte dei produttori, forniscono le ROM del

BIOS in licenza d'uso alle case costruttrici di schede madri,

mentre il servizio di supporto del BIOS compete generalmente

a produttori delle schede.

In passato AMI era l'unico BIOS per Intel, il principale

produttore di processori e schede madri.

Attualmente, oltre l'60% delle schede madri sono Intel e

adottano il BIOS Phoenix.

51