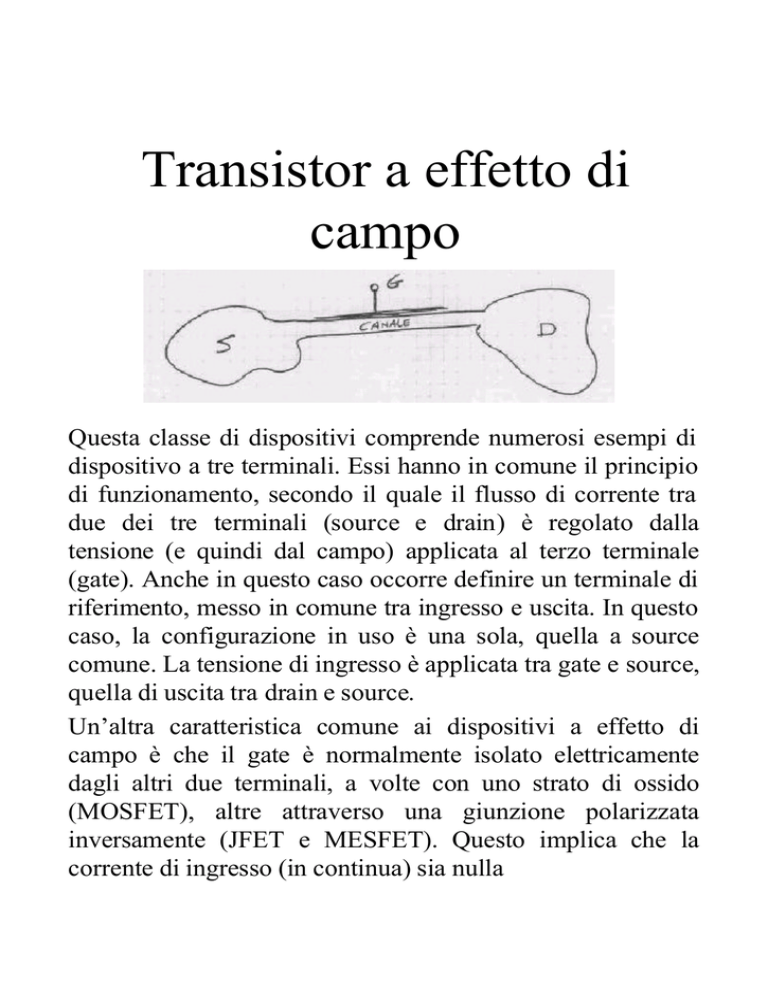

Transistor a effetto di

campo

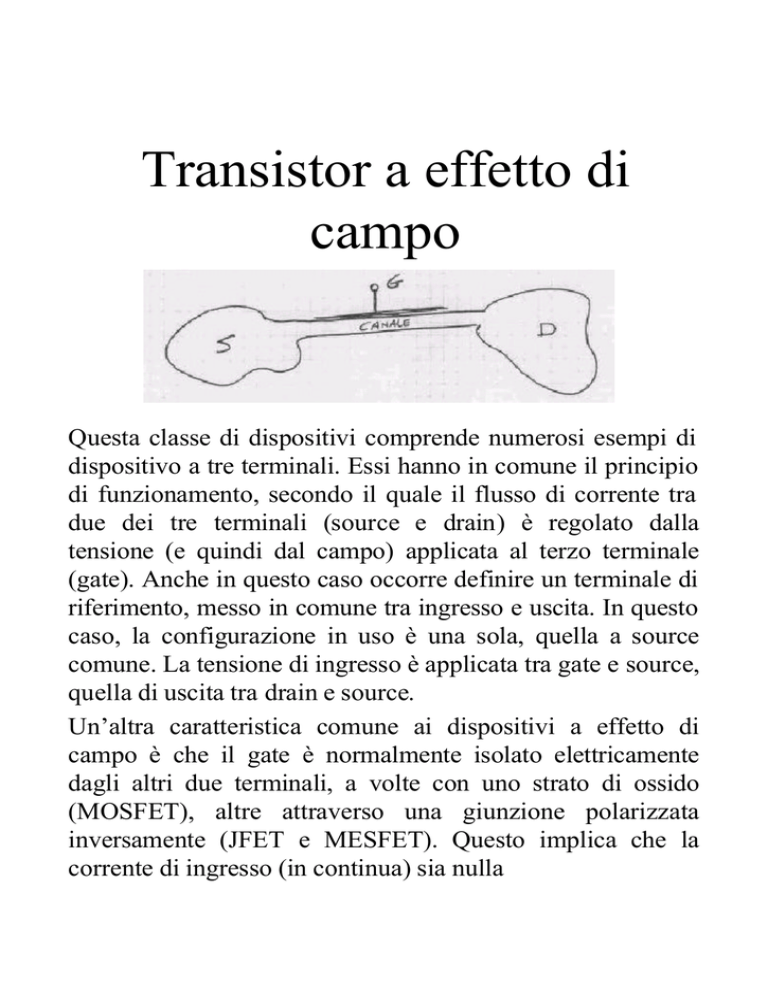

Questa classe di dispositivi comprende numerosi esempi di

dispositivo a tre terminali. Essi hanno in comune il principio

di funzionamento, secondo il quale il flusso di corrente tra

due dei tre terminali (source e drain) è regolato dalla

tensione (e quindi dal campo) applicata al terzo terminale

(gate). Anche in questo caso occorre definire un terminale di

riferimento, messo in comune tra ingresso e uscita. In questo

caso, la configurazione in uso è una sola, quella a source

comune. La tensione di ingresso è applicata tra gate e source,

quella di uscita tra drain e source.

Un’altra caratteristica comune ai dispositivi a effetto di

campo è che il gate è normalmente isolato elettricamente

dagli altri due terminali, a volte con uno strato di ossido

(MOSFET), altre attraverso una giunzione polarizzata

inversamente (JFET e MESFET). Questo implica che la

corrente di ingresso (in continua) sia nulla

JFET

Source e drain sono realizzati mediante contatti ohmici

sul materiale n. Le giunzioni pn superiore e inferiore

sono collegate allo stesso generatore di tensione VG.

Definiamo alcune grandezze di interesse:

L = lunghezza del canale

Z= larghezza del canale

2a = distanza tra le due zone p+

W = estensione della regione svuotata

VS = tensione di source =0

VD = tensione di drain (>=0)

VG = tensione di gate (<=0)

JFET

JFET

JFET

Per trovare la corrente che scorre lungo il canale, si trova

prima la resistenza di quest’ultimo.

R=ρ

L 1

L

L

=

=

A σ 2 Z (a − W ) 2qµ n N D Z (a − W )

W è una funzione della differenza di potenziale

esistente tra la zona p delle giunzioni (ovvero il

gate, equipotenziale per le due giunzioni) e la

zona n, ovvero il canale. Se non c’è tensione

applicata al gate, questa risulta essere

determinata dalla VD.

Il potenziale si distribuisce lungo il canale

partendo dal valore che ha in source, ovvero 0,

fino al valore che ha in drain, ovvero VD.

Conseguentemente, l’ampiezza delle regioni di

svuotamento relative alle due giunzioni cresce

e il canale diventa progressivamente più stretto.

Per piccoli valori di VD, l’effetto di restrizione

progressiva del canale è trascurabile e perciò, la

resistenza complessiva del canale risulta

praticamente indipendente da VD.

JFET

Pertanto in questo intervallo di tensioni vale la relazione:

ID

VD

=

R

Per questo motivo, questo intervallo di valori della

tensione è detto zona lineare.

All’aumentare di VD, l’effetto di restringimento del canale

diventa più rilevante. Inoltre, se al gate è applicata una

tensione VG, tra il gate e il canale si stabilisce una

differenza di potenziale (funzione della coordinata y) che

varia tra VG (in corrispondenza del source, y=0) e VG + VD

(in corrispondenza del drain, y=L). Diminuendo la sezione

media del canale, la corrente cresce meno velocemente

con VD e corrispondentemente la curva viene ad assumere

una pendenza minore rispetto a quella della regione

lineare.

JFET

Questo andamento sublineare prosegue fino a che W(L)=a

Questo avviene per un ben preciso valore della tensione di

drain, detto Vdsat. Se non c’è tensione applicata al gate,

tale valore si ricava dalla seguente relazione:

W (L ) = a

2ε S

⇒

(Vbi − (−VDsat )) = a

qN D

qN D a 2

qN D a 2

⇒ Vbi + V Dsat =

⇒ VDsat =

− Vbi

2ε S

2ε S

Il punto P, di coordinata y=L, è detto punto di pinch-off

(strozzamento) e in quel punto la tensione (rispetto al

source) vale esattamente Vdsat. Se VD aumenta

ulteriormente, P si sposta (di poco, e mantenendo sempre

lo stesso valore di tensione rispetto al source) nella

direzione del source. Corrispondentemente, a partire da

Vdsat, la corrente non cresce più con la tensione, dal

momento che il numero di portatori che possono

partecipare alla conduzione non varia più. A partire da

questo punto si dice che il dispositivo si trova in zona di

saturazione.

JFET

Ma cosa succede nel dispositivo quando VD supera il

valore Vdsat? Come si è detto, il punto di pinch-off si

sposta verso il source, mantenendosi, rispetto al source, ad

una tensione pari a VDsat. Pertanto, il resto della tensione,

ovvero VD – VDsat cade ai capi di una regione i cui

estremi sono, da un lato il punto di pinch-off e dall’altro la

coordinata y=L. Questa regione è completamente svuotata

di portatori, pertanto non può contribuire alla corrente che

scorre nel dispositivo. È però sede di un campo elettrico

attraverso il quale gli elettroni provenienti dal canale

scorrono andandosi poi a riversare nel drain.

Per esplicitare meglio questo concetto, si usa una metafora

idraulica che illustra esattamente lo stesso concetto riferito

però ad un liquido (la nostra corrente) che si riversa da una

cascata (la nostra serie di salti di potenziale elettrico)

Analogamente a ∆h, è Vdsat (che è una

costante, determinata solo da geometrie e

drogaggi) a determinare la corrente.

JFET

Ma cosa succede nel dispositivo quando si applica VG <0?

L’applicazione di una tensione negativa alla zona p di una

giunzione, la manda più in inversa, perciò ne fa allargare

le regioni svuotate e quindi, in questo caso, restringe il

canale. Pertanto, a parità di tensione VD, nel canale scorre

una corrente inferiore. Inoltre, il pinch-off viene raggiunto

per tensioni di drain inferiori, secondo la relazione

W ( L) = a

2ε S

⇒

(Vbi − (VG − VDsat ) ) = a

qN D

qN D a 2

qN D a 2

⇒ Vbi + VDsat − VG =

⇒ V Dsat =

− Vbi + VG

2ε S

2ε S

Da notare che in un JFET a canale n, la

tensione di gate non può mai essere positiva

perché questo farebbe si che le giunzioni di

gate andassero in diretta causando un

dirottamento della corrente dal canale al gate.

Caratteristiche corrente-tensione del JFET

L’andamento della corrente in funzione della

tensione si calcola nel JFET solo per tensioni

inferiori a quella di pinch-off. Quando questo si

instaura infatti si considera che la corrente

rimanga costante al valore che aveva al

momento del pinch-off (in realtà lo

spostamento di P verso l’interno del canale

implica un leggera variazione di I con V dovuta

all’accorciamento del canale, ma di solito

questo fenomeno è quasi impercettibile).

dV ( y) = I D dR = I D ρ

dy

I

dy

= D

=

2 Z ( a − W ( y )) σ 2 Z ( a − W ( y ))

I D dy

2 qµ n N D Z ( a − W ( y ))

D' altra parte :

2ε S

W(y) =

[V ( y ) − VG + Vbi ]

qN D

qN D

⇒ dV =

WdW

εS

=

⇒ I D dy = 2 qµ n N D Z ( a − W ( y)) dV = 2 qµ n N D Z

qN D

( a − W ( y ))WdW

εS

Caratteristiche corrente-tensione del JFET

Integrando ambo i membri tra 0 e L si ottiene:

W ( L)

qN D aW 2 W 3

I D L = 2qµ n N D Z

−

ε S 2

3

W ( 0)

dove :

2ε S

W ( 0) =

[Vbi − VG ]

qN D

2ε S

W ( L) =

[Vbi − VG + VD ]

qN D

da cui, ponendo

VP = Vbi − VG + VDsat

µ n ZN D2 q 2 a 3

IP =

εSL

si ottiene :

2 V − VG + VD

V

I D = I P D − bi

V

3

VP

P

3

2

3

2

2 V − VG

+ bi

3 VP

VP è detta tensione di pinch-off e rappresenta

la tensione del punto di pinch-off misurata

rispetto al gate.

Caratteristiche corrente-tensione del JFET

Vediamo

come

si

può

semplificare

l’espressione completa della corrente nelle

varie regioni di funzionamento:

REGIONE LINEARE

2 V − VG + VD

V

I D = I P D − bi

V

3

VP

P

IP

Vbi − VG

≅

1 −

V D

VP

VP

3

2

3

2

2 V − VG

+ bi

=

3 VP

La relazione lineare tra ID e VD consente di

derivare dalla precedente espressione la

conduttanza di canale, definita come:

∂I D

IP

Vbi − VG

gD =

=

1 −

∂VD V =cost VP

VP

G

analogamente è possibile definire la transconduttanza g m :

∂I

I

VP

gm = D

= P2

VD

∂VG V =cost 2Vp Vbi − VG

D

Caratteristiche corrente-tensione del JFET

REGIONE DI SATURAZIONE

3

3

2 V − VG + VD 2 2 Vbi − VG 2

V

+

=

I D = I P D − bi

V

3

VP

3 VP

P

3

3

VDsat 2 VP 2 2 Vbi − VG 2

⇒ I Dsat = I D V =V = I P

−

+

=

D

Dsat

VP

3 VP

3 VP

3

3

V

−

V

+

V

2

2

V

−

V

2

V

2

p

bi

G

G

= IP

− P + bi

=

VP

3 VP

3 VP

3

2

1 V − VG 2 Vbi − VG

= I P − bi

+

3

VP

3 VP

Come si vede la corrente non dipende più da

VD. Perciò:

∂I D

=0

∂VD V =cost

G

e, per quanto riguarda g m :

∂I D

I P

V − VG

gm =

=−

1 − bi

∂VG V =cost

VP

Vp

gD =

D

Si noti come, in valore assoluto, gm calcolata in

saturazione sia uguale a g D in zona lineare

Effetti di breakdown

Data la presenza di giunzioni polarizzate

inversamente, è lecito aspettarsi la possibilità

che si abbia breakdown relativo a queste

giunzioni, allorchè

VD − VG ≥ V BR

L’effetto sulle curve di uscita è analogo a

quello che si osserva nei BJT in emettitore

comune

Circuito equivalente per piccoli segnali

A questo punto si è ottenuto il circuito per

piccoli segnali in entrambe le regioni di

funzionamento. Il dispositivo, in zona lineare,

risponderà all’applicazione di un piccolo

segnale,≈con una≈ corrente:

i D = g D v D + g m vG

con g D e g m determinat i dalle condizioni di polarizzaz ione

stazionari a del JFET

In saturazion e :

≈

i D = g m vG

Estensione del modello a condizioni di non

idealità

Verranno in particolare presi in considerazione i

seguenti effetti:

• esistenza di resistenze serie

• possibilità che gD sia diverso da 0 in saturazione

• esistenza di capacità di svuotamento tra il gate e

gli altri terminali

Estensione del modello a condizioni di

non idealità

1)Effetti di resistenze serie

Sono dovuti a possibili cadute di potenziale nel

semiconduttore tra il canale vero e proprio e i

contatti di source e drain

Come conseguenza:

VD 'S ' = VDS + I D ( RS + RD )

VG 'S ' = VGS + I D RS

passando ai parametri di piccolo segnale :

≈

≈

≈

≈

≈

≈

v D 'S ' = v DS + i D ( RS + RD )

vG 'S ' = vGS + i D RS

≈

≈

≈

da cui si ricavano v DS e vGS da inserire in iD

≈

≈

≈

i D = g D v DS + g m vGS =

≈

≈

≈

= g D ( v D ' S ' − ( R S + R D ) i D ) + g m ( vG ' S ' − R S i D )

Estensione del modello a condizioni di

non idealità

da cui :

≈

≈

gm

iD =

vG ' S ' +

1 + RS g m + ( RS + R D ) g D

≈

gD

+

v D 'S '

1 + RS g m + ( RS + RD ) g D

da cui :

gm

g 'm =

Più piccoli

1 + RS g m + ( RS + RD ) g D

rispetto al

gD

'

gD =

caso ideale

1 + RS g m + ( RS + R D ) g D

2) gD diverso da 0 in saturazione

Man mano che il

punto di pinch-off si

sposta verso

l’interno, diminuisce

il percorso resistivo

della corrente

Estensione del modello a condizioni di

non idealità

Il circuito equivalente conterrà l’elemento gD

anche in saturazione (con un valore ovviamente

diverso rispetto a quello della zona lineare)

3) Capacità di giunzione

CGS e CGD rappresentano le capacità di

svuotamento delle giunzioni, mentre CDS

rappresenta il “capacitore” compreso tra Drain e

Source che ha come dielettrico l’intera regione

p+ e le sue regioni svuotate