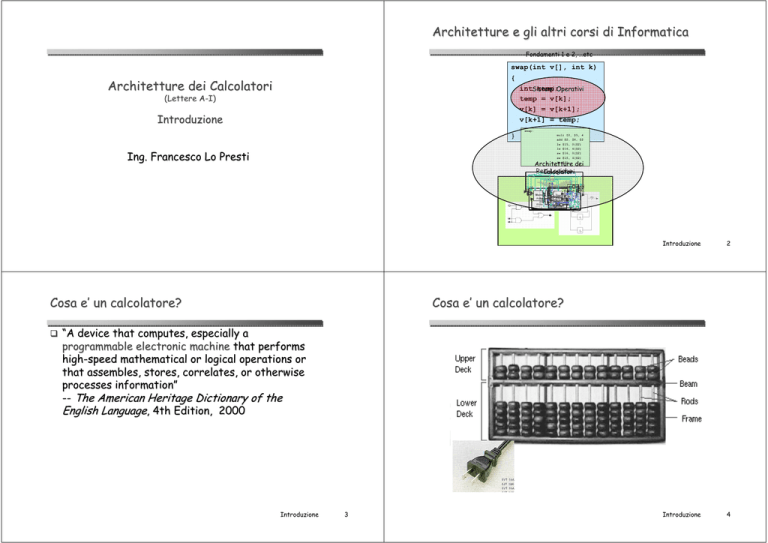

Architetture e gli altri corsi di Informatica

Fondamenti 1 e 2, …etc

swap(int v[], int k)

{

Architetture dei Calcolatori

intSistemi

temp;Operativi

temp = v[k];

v[k] = v[k+1];

v[k+1] = temp;

(Lettere A-I)

Introduzione

swap:

}

muli $2, $5, 4

add $2, $4, $2

lw $15, 0($2)

lw $16, 4($2)

sw $16, 0($2)

sw $15, 4($2)

jr $31

Ing.

Ing. Francesco Lo Presti

Architetture dei

Reti

Logiche

Calcolatori

ALUout

A

B

MDR IR

PC

Cosa e’ un calcolatore?

Instr[31-26]

PCWriteCond

Control

PCWrite

PCSource

IorD

ALUOp

MemRead

ALUSrcB

MemWrite

ALUSrcA

MemtoReg

RegWrite

PC[31-28]

IRWriteRegDst

Instr[25-0]Shift 282

left 2 0

1

0

0 Memory

Read Addr 11zero

1

Read

0Register

Read Addr 2

Address

Read Data

1Data

1 Addr 0

Write

1 Read

ALU

(Instr. or Data)

4

1

Write

File

0Data

2

2 Data 3

Write Data Instr[15-0]

00

SignShift

ALU

Instr[5-0]

32 2

Extend

left

control

Introduzione

2

Introduzione

4

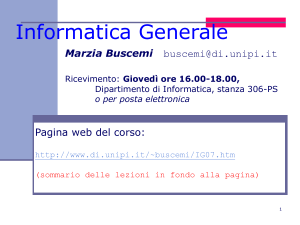

Cosa e’ un calcolatore?

“A device that computes, especially a

programmable electronic machine that performs

highhigh-speed mathematical or logical operations or

that assembles, stores, correlates, or otherwise

processes information”

information”

-- The American Heritage Dictionary of the

English Language, 4th Edition, 2000

Introduzione

3

Calcolatore Elettronico

Calcolatore Elettronico

Macchina per l’

l’esecuzione automatica di algoritmi

❍ General Purpose:

Purpose: puo’

puo’ svolgere qualsiasi elaborazione di

cui sia noto un algoritmo risolutivo

Accetta in ingresso informazioni codificate in

forma digitale

2. Le elabora attraverso un programma memorizzato

3. Produce informazioni in uscita

1.

Programma e’ un algoritmo espresso in un

linguaggio di programmazione

Linguaggio macchina binario:

binario: il linguaggio

direttamente eseguibile dal calcolatore

Istruzione Macchina

❍

❍

Dati

operazione logico/aritmetica su dati o di trasferimento

dati

codificata in binario

Programma

memorizzato in

esecuzione

Risultati

Computer

Esempio 10000110010100000 istruisce il calcolatore di

effettuare una somma

Programma eseguibile:

eseguibile: un algoritmo espresso in

linguaggio macchina

Introduzione

5

Introduzione

6

… e loro interconnessione

Componenti principali di un calcolatore

Processore

Processore

Unità di

controllo

Unità di

elaborazione

dati

Dispositivi

di input

Memoria

Tastiera

Unità di

controllo

Mouse

Disco

Unità di

elaborazione

dati

Monitor

Dispositivi

di output

Dispositivi

di I/O

Dispositivi

di I/O

Interfaccia

di I/O

Interfaccia

di I/O

Memoria

Stampante

Processore o unità

unità centrale di elaborazione (Central

(Central Processing Unit

– CPU)

Memoria principale (Main

(Main Memory – MM)

Dispositivi di Input/Output (I/O) e loro interfacce

Introduzione

Bus

7

dati

indirizzi

controllo

Bus di sistema: collega i componenti principali di un calcolatore

calcolatore

(linee dati, indirizzo, controllo)

Introduzione

8

Processore - Central Processing Unit (CPU)

Processore - Central Processing Unit (CPU)

Provvede all’

all’esecuzione delle istruzioni macchina

Processore e’

e’ composto da due sottosistemi:

Ciclo di Esecuzione

1. Prelievo Istruzione dalla Memoria

2. Decodifica Istruzione

3. Esecuzione Istruzione

1.

Unità

Unità di Controllo (Control) – Parte di Controllo

❍

Controlla il sequenziamento e l’l’esecuzione delle istruzioni

generando i segnali di controllo

2. Unita’

Unita’ di Elaborazione (Datapath

(Datapath)) – Parte

Operativa

Ogni Processore e’ caratterizzato da un proprio

❍

Esegue le istruzioni

ALU

❍

Banco di Registri (Register

(Register File)

❍

linguaggio macchina

Esegue operazioni logico aritmetiche sui dati

Memoria interna CPU

Program Counter (PC)

– Indirizzo Prossima Istruzione

Instruction Register (IR)

– Codice Istruzione da eseguire

Introduzione

9

PC

IR

Bus Dati

Registri

10

Il Bus

La struttura di interconnessione più

più comune

❍ percorsi di comunicazione tra due o più

più dispositivi

❍ mezzo di trasmissione condiviso

❍ Usualmente di tipo broadcast

Bus Controllo

ALU

Bus Interno CPU

Unità di Elaborazione

Bus Indirizzi

Processore - Central Processor Unit (CPU)

Introduzione

I dati sono visibili da tutte le unità

unità connesse

Processore

Unità di

controllo

Unità di Controllo

Unità di

elaborazione dati

Dispositivi di

I/O

Dispositivi di

I/O

Interfaccia di

I/O

Interfaccia di

I/O

Memoria

Segnali di Controllo

Bus

Introduzione

11

dati

indirizzi

controllo

Introduzione

12

Il Bus

La Memoria

Composto da più

più linee.

❍ Ogni linea:

Memoria Primaria:

Primaria: Memoria Centrale

❍ Contiene istruzioni/dati dei programmi in esecuzione

…in formato binario

è conduttore elettrico (traccia in rame)

Può trasmettere segnali che rappresentano 0 o 1, un bit

❍

❍

Tre tipi di linee

❍ Linee dati: Bus dati

❍ Linee indirizzo: Bus indirizzi

❍ Linee di controllo: Bus controllo

Memoria ad accesso casuale

– Tempo di accesso costante

SRAM, DRAM, etc.

❍

❍

Processore

Unità di

controllo

Bus

Dispositivi di

I/O

Dispositivi di

I/O

Interfaccia di

I/O

Interfaccia di

I/O

❍

Veloce (~10(~10-100ns) Costosa

Dimensioni contenute (fino a qualche Gigabyte)

E’ organizzata come una gerarchia di memorie

Cache di primo e secondo livello…

livello…

Memoria

Unità di

elaborazione dati

Volatile

RAM – Random Access Memory

Memoria Secondaria:

Secondaria: Dischi,

Dischi, CD, etc..

❍ Memoria di lungo periodo - non volatile

❍ Tempo di accesso maggiori (~ms e piu’

piu’), economica

dati

indirizzi

controllo

Introduzione

13

La Memoria Centrale

Introduzione

14

Disco rigido

Composta di celle,

celle, o locazioni,

locazioni, a loro volta

composte da un numero fisso di bit

❍

Tipicamente cella=byte

cella=byte (8 bit)

Ogni locazione e’ associata ad un indirizzo

byte M-1

byte M-2

nell’

nell’intervallo [0,1,…

[0,1,…,M,M-1]

❍

❍

M dimensione della memoria

La memoria e’ vista come un vettore di byte

La CPU (ma non solo) accede alle informazioni in

Memoria

Testina

Motore per la rotazione dei dischi

scrittura/lettura tramite indirizzo della cella

❍

Non necessariamente M= 2m

Operazioni:

Operazioni: Lettura/Scrittura

❍

❍

Costituito da un insieme di piatti rotanti (da 1 a 15)

Indirizzi a m bit: spazio di indirizzamento 2m

Per ragioni di efficienza le operazioni di

lettura/scrittura vengono effettuate per gruppi di

byte detti parola (word)

1 parola=

parola= 1,2,4,8 byte

Byte 1

Piatti rivestiti di una superficie magnetica

Byte 0

Esiste una testina (bobina) per ogni faccia

❍

8 bit

Generalmente piatti a doppia faccia

Le testine di facce diverse sono collegate tra di loro e si muovono

muovono

contemporaneamente

Velocità

Velocità di rotazione costante (ad es. 7200 RPM)

Introduzione

15

Introduzione

16

Esecuzione di un Programma

L’organizzazione dei dati sul disco

tracce

Input del Codice/Dati

settori

Processor

traccia

Control

Suddivisione della superficie del disco in anelli concentrici, detti

detti tracce

Registrazione seriale su tracce concentriche

❍

000000

000000

100011

100011

101011

101011

000000

10001000-5000 tracce

00000

00100

00010

00010

00010

00010

11111

00101

00010

01111

10000

10000

01111

00000

0001000010000000

0001000000100000

0000000000000000

0000000000000100

0000000000000000

0000000000000100

0000000000001000

Devices

Input

Memory

Datapath

Output

Tracce adiacenti separate da spazi

Ciascuna traccia è divisa in settori

❍

❍

❍

Il settore è la più

più piccola unità

unità che può essere trasferita (scritta o letta)

Centinaia di settori per traccia, generalmente di lunghezza fissa

fissa (ad es., 512 byte)

Il settore contiene, tra l’l’altro, un ID del settore, i dati e un codice di correzione

di errore: la capacità

capacità formattata scende del 15%

La stessa traccia su piatti diversi forma un cilindro

Introduzione

17

Esecuzione di un Programma

Control

Datapath

Il Processore preleva

un’istruzione

Memory

000000

000000

100011

100011

101011

101011

000000

00000

00100

00010

00010

00010

00010

11111

00101

00010

01111

10000

10000

01111

00000

18

Esecuzione di un Programma

Codice/Dati salvati in

memoria

Processor

Introduzione

0001000010000000

0001000000100000

0000000000000000

0000000000000100

0000000000000000

0000000000000100

0000000000001000

Control

Input

Datapath

Output

Introduzione

Memory

Processor

Devices

19

000000

000000

100011

100011

101011

101011

000000

00000

00100

00010

00010

00010

00010

11111

00101

00010

01111

10000

10000

01111

00000

0001000010000000

0001000000100000

0000000000000000

0000000000000100

0000000000000000

0000000000000100

0000000000001000

Devices

Input

Output

Introduzione

20

Esecuzione di un Programma

L’unita’ di controllo del

processore decodifica l’istruzione

Esecuzione di un Programma

L’unita’ di esecuzione del processore esegue l’istruzione

(eventualmente prelevando operandi/salvando il risultato)

Che devo fare?

Processor

Processor

Devices

Control

000000 00100 00010 0001000000100000

Memory

000000 00100 00010 0001000000100000

Input

Datapath

Introduzione

contents Reg #4 ADD contents Reg #2

results put in Reg #2

21

Esecuzione di un Programma

Memory

Processor

Datapath

Memory

Input

Datapath

Output

Control

Devices

Control

000000

000000

100011

100011

101011

101011

000000

00000

00100

00010

00010

00010

00010

11111

00101

00010

01111

10000

10000

01111

00000

0001000010000000

0001000000100000

0000000000000000

0000000000000100

0000000000000000

0000000000000100

0000000000001000

Output

Introduzione

22

Esecuzione di un Programma

A completamento del programma, i risultati vengono

salvati/inviati su un dispositivo di output

Devices

Input

Processor

Output

Memory

Control

Datapath

Devices

Input

00000100010100000000000000000000

00000000010011110000000000000100

00000011111000000000000000001000

Output

Fetch

Exec

Decode

Introduzione

23

Introduzione

24

Esecuzione di un Programma

Algoritmi e Programmi

Un programma e’ un algoritmo espresso in un

A completamento del programma, i risultati vengono

salvati/inviati su un dispositivo di output

Processor

Control

linguaggio di programmazione

Il linguaggio direttamente eseguibile dal

calcolatore e’ il suo linguaggio macchina binario

Un algoritmo espresso nel linguaggio macchina

binario prende il nome di programma eseguibile

Devices

Memory

Datapath

Input

00000000101000010000000000011000

Output

00000000100011100001100000100001

10001100011000100000000000000000

10001100111100100000000000000100

10101100111100100000000000000000

00000100010100000000000000000000

00000000010011110000000000000100

00000011111000000000000000001000

Introduzione

10101100011000100000000000000100

00000011111000000000000000001000

25

Dalle istruzioni in binario all’assembler

Introduzione

26

Un programma in assembler

swap:

Programmazione in linguaggio macchina binario

❍

Per semplificare e velocizzare e’

e’ preferibile impiegare una

rappesentazione simbolica delle istruzioni

Un esempio di traduzione

Da un programma in

Linguaggio assembler:

assembler: Linguaggio composto da istruzioni

assembler MIPS ad un

programma in linguaggio

macchina binario

simboliche che corrispondono a istruzioni binarie

❍

simbolico add A,B al posto di 1000110010100000

Programma assemblatore

(assembler):

(assembler):

❍

❍

Prende in ingresso un

programma scritto in

assembler

Genera il corrispondente

programma in linguaggio

macchina

muli $2, $5, 4

add $2, $4, $2

lw $15, 0($2)

lw $16, 4($2)

sw $16, 0($2)

sw $15, 4($2)

jr $31

00000000101000010000000000011000

00000000100011100001100000100001

assemblatore

10001100011000100000000000000000

10001100111100100000000000000100

10101100111100100000000000000000

00000000101000010000000000011000

10101100011000100000000000000100

00000000100000100001000000100001

10001100011000100000000000000000

00000011111000000000000000001000

10001100111100100000000000000100

10101100010100000000000000000000

10101100011000100000000000000100

Introduzione

27

00000011111000000000000000001000

Introduzione

28

Da un linguaggio di programmazione ad alto

livello all’assembler

Il processo di traduzione completo

swap(int v[], int

k)

Un linguaggio di programmazione ad alto livello

❍ Offre astrazioni notevoli

{

int temp;

temp = v[k];

v[k] = v[k+1];

v[k+1] = temp;

Variabili, tipizzazione dei dati

Procedure, funzioni

Programmazione ad oggetti

Gestione di eccezioni

❍

❍

swap:

}

Programma in linguaggio

ad alto livello

Aumenta la produttività

produttività del programmatore

Permette al programma di essere indipendente dal

computer sul quale viene sviluppato

compilatore

Programma in

linguaggio assembler

(MIPS)

muli $2, $5, 4

add $2, $4, $2

lw $15, 0($2)

lw $16, 4($2)

sw $16, 0($2)

sw $15, 4($2)

jr $31

assemblatore

Programma in linguaggio

macchina binario (MIPS)

Programma compilatore

❍ traduce da un linguaggio di programmazione ad alto livello

al linguaggio assembler

❍ Talvolta traduce direttamente da linguaggio di

programmazione ad alto livello a linguaggio macchina

00000000101000010000000000011000

00000000100011100001100000100001

10001100011000100000000000000000

10001100111100100000000000000100

10101100111100100000000000000000

10101100011000100000000000000100

Introduzione

29

Introduzione

00000011111000000000000000001000

Compilazione ed Interpretazione

Il Compilatore

La compilazione e’ un processo di traduzione che,

che, a

Il Compilatore sostituisce a ogni istruzione del

partire da un programma scritto in linguaggio

simbolico,

simbolico, ne genera una versione equivalente in

assembler/linguaggio

assembler/linguaggio macchina

❍

❍

programma PL1, scritto nel linguaggio L1, una

sequenza di istruzioni scritte nel linguaggio L0 di

piu’

piu’ basso livello

ProgrammaC

ProgrammaLM

Il programma che effettua la traduzione prende il nome

di compilatore

Il programma risultante puo’

puo’ essere eseguito

direttamente sul calcolatore

❍

indiretta di un programma ad opera di un

programma detto interprete

❍

L’interprete legge il codice del programma da eseguire e

ne simula l’esecuzione,

esecuzione, generando i relativi risultati

L’interprete e’, in sostanza,

sostanza, un simulatore di un

calcolatore virtuale il cui linguaggio macchina e’ il

linguaggio interpretato

Introduzione

31

Compilatore

C/Assembler

Il programma risultante PL0

equivalente a PL1 ma scritto

nel linguaggio L0

Se L0 e’

e’ il linguaggio

macchina binario LM, PL0

puo’

puo’ essere direttamente

eseguito

Altrimenti puo’

puo’ essere

ulteriormente compilato,

compilato,

oppure interpretato

L’interpretazione e’ un processo di esecuzione

❍

30

Computer

Dati

Risultati

ProgrammaLM

Computer

Introduzione

32

L’interprete

Interpretazione o compilazione?

Per eseguire PL1, scritto in L1, l’interprete,

interprete, scritto

Ogni linguaggio puo’

puo’ essere sia interpretato che

compilato

in L0, analizza – passo passo - ogni istruzione da

eseguire di PL1 e ne realizza l’effetto,

effetto, eseguendo

una sequenza di istruzioni del linguaggio di L0 ad

essa equivalenti

❍

L’interpretazione e’ piu’

piu’ lenta dell’

dell’esecuzione

diretta

❍

❍

Programma C

Migliore diagnostica

Maggiore portabilita’

portabilita’

L’interprete,

interprete, se scritto in un linguaggio diffuso,

diffuso, puo’

puo’ essere

reso piu’

piu’ facilmente disponibile su un nuovo calcolatore

Risultati

Interprete C

Dati

Il C, C++ sono normalmente compilati

Talvolta,

Talvolta, compilazione ed interpretazione sono

combinate

❍

❍

Computer

Per combinare i vantaggi

Si compila in un linguaggio intermedio che poi e’

e’

interpretato

Approccio utilizzato per l’esecuzione dei programmi in Java

Introduzione

33

Diversi Livelli di Astrazione

swap(int v[], int

k)

int temp;

temp = v[k];

v[k] = v[k+1];

v[k+1] = temp;

Diversi Livelli di Astrazione

compilatore

Programma in

linguaggio assembler

(MIPS)

}

Programma in linguaggio

ad alto livello

muli $2, $5, 4

add $2, $4, $2

lw $15, 0($2)

lw $16, 4($2)

sw $16, 0($2)

sw $15, 4($2)

jr $31

Compiler

0

1

B

0

1

FileAddr

Write

Read

1

Data

2

Write

Data

0

Sign

Shift

Instr[15-0]

Extend left 2

Instr[5-0] 32

MDR

Write Data

Read Addr 1

Read

Register

Read

Addr

Data

1 2

4

0

1

2

3

zero

Assembler

ALU

00

ALU

control

0000 1001

Programma in linguaggio

1010 1111

macchina (MIPS) Software 1100 0110

0101 1000

00000000101000010000000000011000

Hardware

microinterpreta

zione

10001100011000100000000000000000

Relazioni di Trasferimento

del Datapath (RTL)

10001100111100100000000000000100

10101100111100100000000000000000

00000011111000000000000000001000

0110

1000

1111

1001

1010

0000

0101

1100

1111

1001

1000

0110

0101

1100

0000

1010

1000

0110

1001

1111

IR ← Imem[PC]; PC ← PC + 4

RTL Code

ALUOP[0:3] ⇐ InstReg[9:11] & MASK

10101100011000100000000000000100

Introduzione

Assembly

code

Machine

code

0($2)

4($2)

0($2)

4($2)

1100

0101

1010

0000

C code

Machine Interpretation

00000000100011100001100000100001

2

0

1

lw $15,

lw $16,

sw $16,

sw $15,

Programma in linguaggio

Assembler (e.g., MIPS)

Programma in linguaggio

macchina binario (MIPS)

ALUout

A

IR

PC

Instr[31-26]

PCWriteCond

PCWrite Control

PCSource

IorD

ALUOp

MemRead

ALUSrcB

MemWrite

ALUSrcA

MemtoReg

RegWrite

IRWrite

RegDst

PC[31-28]

Shift

Instr[25-0]

left 2 28

temp = v[k];

v[k] = v[k+1];

v[k+1] = temp;

Programma in un linguaggio

di alto livello (e.g., C)

assemblatore

Memory

Address

Read Data

(Instr. or Data)

34

swap:

{

0

1

Introduzione

35

Introduzione

36

Architettura a Livelli

Calcolatore come insieme gerarchico di livelli o

Livelli tipici di un calcolatore

Macchine Virtuali {MV0, MV1,…

MV1,…,MVn}

MVn}

MVi rappresenta un diverso livello di astrazione del

calcolatore

Macchina Virtuale a livello i

❍ Moduli che operano al livello i

Processore

Linguaggio Li per la

programmazione a livello i

Livello dei linguaggi orientati

alle applicazioni

M3Dispositivi

Dispositivi

di I/O

Unità di

controllo

e loro struttura d’interazione

❍

M2

di I/O

Livello del Linguaggio assembler

Memoria

M1

Unità di

elaborazione

dati

Struttura di

Interfaccia

interazione

di I/O

Livello del Sistema Operativo

Interfaccia

di I/O

M4

Software

Livello del Linguaggio Macchina –

Livello ISA

Elemento Caratterizzante

❍

❍

Risorse Ri visibili al livello i

(Li,Ri)

Li,Ri) l’architettura

del livello i

Bus

Hardware

M5

dati

indirizzi

controllo

M6

Emulazione

❍

Macchina Firmware - Microarchitettura

Macchina Hardware

Astrazione o Virtualizzazione

Architettura a Livelli

Aspetti visibili a chi programma

al livello i

Introduzione

37

Architettura a Livelli

Linguaggi ai vari livelli e loro relazioni

5.

Livello dei Linguaggi orientati alle appl.

appl. (C,C++, Java)

4.

Compilazione o Interpretazione (Java)

Assemblaggio (Assembler)

Livello 1: Macchina Firmware – Microarchitettura

❍ Interpreta ed esegue le istruzioni del linguaggio macchina

❍ E’ direttamente realizzato con i componenti della

macchina hardware

❍ Moduli - Unita’

Unita’ di Elaborazione:

Elaborazione: CPU, Memoria,

Memoria, Unita’

Unita’ di

I/O

❍ L1: Linguaggio di Microprogrammazione

❍ R1: Reti combinatorie e sequenziali

Livello del Sistema Operativo (Linguaggio

Macchina+Chiamate di Sistema)

Sistema)

Interpretazione parziale

2.

Software

Livello del linguaggio macchina – ISA (Linguaggio

(Linguaggio Macchina)

Macchina)

Hardware

Esecuzione diretta o microinterpretazione

1.

Macchina Firmware (Linguaggio

(Linguaggio di microprogrammazione)

microprogrammazione)

0.

Livello 0: Macchina Hardware

❍ Livello della logica digitale

❍ Moduli:

Moduli: Reti combinatorie e sequenziali

❍ L0: Algebra booleana binaria

❍ R0: Porte logiche

Livello del Linguaggio Assembler (Assembler)

3.

38

Architettura a Livelli

Introduzione

Realizzazione hardware

Macchina Hardware (Algebra booleana?)

booleana?)

Introduzione

39

Introduzione

40

Architettura a Livelli

Architettura a Livelli

Livello 2: Livello del Linguaggio Macchina (ISA)

❍ Macchina nuda come appare al programmatore di sistema.

sistema.

Le istruzioni del suo linguaggio sono interpretate ed

eseguite dai microprogrammi del processore

❍ Moduli:

Moduli: Programmi

❍ L2: Linguaggio macchina

❍ R2: Registri,

Registri, spazio di memoria

Livello 4: Livello del Linguaggio Assembler

❍ Livello piu’

piu’ basso utilizzabile dal programmatore di

applicazioni

❍ Moduli:

Moduli: Processi

❍ L4: linguaggio assembler

Livello 3: Livello del Sistema Operativo

❍ Gestisce le risorse del sistema nei confronti dei livelli

superiori

Livello 5: Livello dei Linguaggi orientati alle appl.

appl.

❍ Livello usato per sviluppare applicazioni

❍ Moduli:

Moduli: Processi

❍ L5: C, C++, Java, etc..

❍ E’ implementato tramite compilazione e/o interpretazione

Forma simbolica dei linguaggi L2, L3

❍

Processore (Multiprogrammazione),

Multiprogrammazione), Memoria Principale

(Memoria Virtuale),

Virtuale), Memoria Secondaria (File System)

❍

❍

❍

L3: Linguaggio macchina+Chiamate di sistema

R3: R2+spazi di memoria,

memoria, dispositivi di I/O, processori,

processori,…

Interpretazione parziale (per le chiamate di sistema)

sistema)

Introduzione

41

Architettura a Livelli

Linguaggi ai vari livelli e loro relazioni

5.

Livello dei Linguaggi orientati alle appl.

appl. (C,C++, Java)

4.

3.

Compilazione o Interpretazione (Java)

ISA - Cosa il calcolatore e’ capace di fare

Assemblaggio (Assembler)

❍

Livello del Sistema Operativo (Linguaggio

Macchina+Chiamate di Sistema)

Sistema)

2.

1.

Macchina Firmware (Linguaggio

(Linguaggio di microprogrammazione)

microprogrammazione)

0.

Quali istruzioni?

istruzioni?

MO - Come la macchina implementa ISA

Interpretazione parziale

Software

Livello del linguaggio macchina – ISA (Linguaggio

(Linguaggio Macchina)

Macchina)

Hardware

Esecuzione diretta o microinterpretazione

42

Instruction Set Architecture (ISA) + Machine

Organization (MO)

Livello del Linguaggio Assembler (Assembler)

Introduzione

Architettura dei Calcolatori

E’ implementato tramite “assemblaggio”

assemblaggio”

❍

Loro Implementazione Fisica

Realizzazione hardware

Macchina Hardware (Algebra booleana?)

booleana?)

Introduzione

43

Introduzione

44

Instruction Set Architecture (ISA)

Instruction Set Architecture (ISA)

“... the attributes of a [computing] system as seen by the

programmer, i.e. the conceptual structure and functional

behavior, as distinct from the organization of the data

flows and controls, the logic design, and the physical

implementation.”

implementation.”

— Amdahl, Blaaw,

Blaaw, and Brooks, 1964

ISAISA-Interfaccia tra Hardware e Software

Deve:

Deve:

❍ Fornire funzionalita’

funzionalita’ ai livelli piu’

piu’ alti

❍ Permettere un efficiente implementazione ai livelli piu’

piu’

bassi

❍ Insieme delle istruzioni

❍ Numero di bit che rappresentano tipi di dati

software

❍ Tecniche di indirizzamento della memoria, …

Instruction Set Architecture

hardware

Introduzione

45

Introduzione

Organizzazione del Calcolatore

MIPS R3000 ISA

Caratteristiche delle principali unita’

unita’ funzionali

❍ Registri,

Registri, ALU, etc.

Categorie di Istruzioni:

Istruzioni:

❍ Load/Store

❍ Computational

Strutture di Interconnessione

Registri

R0 - R31

Registri come operandi

Unita’

Unita’ di Elaborazione e Unita’

Unita’ di Controllo

❍

Organizzazione del sottosistema di Memoria

Descrizione tramite

46

❍

Register Transfer Level

Jump and Branch

Floating Point

PC

HI

coprocessor

(RTL)

❍

❍

Gestione della Memoria

Speciali

LO

3 formati istruzione: tutti a 32 bits

OP

rs

rt

OP

rs

rt

OP

Introduzione

47

rd

sa

immediate

jump target

funct

Formato R

Formato I

Formato J

Introduzione

48

Evoluzione delle ISA

Evoluzione delle ISA

Dai primi calcolatori (anni ’50)

❍ Semplici

❍ Pochi tipi di istruzioni e modi di indirizzamento

Accumulatore singolo

(EDSAC 1950)

Accumulatore+Registri indice

…ai CISC (Complex Instruction Set Computer)

(Manchester Mark I, IBM 700 1952)

(anni’

(anni’70)

Separazione del modello di programmazione

dall’implementazione

❍ ISA

Basati su linguaggi ad alto livello – Stack

Concetto di famiglia

(B5000 1963)

(IBM 360 1963)

e processori via via piu’

piu’ complessi

❍ Riduzione gap semantico tra linguaggi di alto livello e

linguaggi macchina

❍ Difficcili da ottimizzare

…ai RISC (Reduced Instruction Set Computer)

❍ ISA e processori semplici

❍ Facilita l’ottimizzazione

Macchine a registri generaili

CISC

Architetture Load-Store

(Vax, Intel, 1977-)

Software: Compilatori Ottimizzanti

Hardware: Processori veloci (impiego efficiente delle

tecniche di pipelining)

Introduzione

RISC

(MIPS, Sparc, HP-Pa, …)

Introduzione

49

Le Caratteristiche dei RISC

La famiglia dei Processori INTEL

Le architetture RISC sono caratterizzate da

8086:

8086: (1978, 29k transistor) – Processore a 16 bit,

poche proprieta’

proprieta’ chiave

❍

❍

base del PC IBM originale,

originale, dotato di MSMS-DOS

Numero elevato di registri generali

Pochi formati di istruzione

❍

❍

❍

Indirizzi a 20 bit (1024Kb indirizzabili)

indirizzabili)

80286:

80286: (1982, 134k transistor) – Processore a 16

Generalmente della stessa lunghezza

❍

50

bit, base dei PCPC-AT IBM, piattaforma originale per

MS Windows

i386:

i386: (1985, 275k transistor) – Processore a 32 bit

i486:

i486: (1989, 1.9M transistor) – Prestazioni

migliorare e floating point unit integrata

Pentium:

Pentium: (1993, 3.1M transistor) – Prestazioni

migliorate,

migliorate, qualche estensione del set di istruzioni

Numero limitato di codici operativi e di modi di

indirizzamento

Tutte le operazioni logico/aritmetiche hanno come

operandi i registri

Le sole operazioni che coinvolgono la memoria sono quelle

di load e store

Introduzione

51

Introduzione

52

La famiglia dei Processori INTEL

Un po’ di Storia

Pentium/MMX:

Pentium/MMX: (1997, 4.5M transistor) – Nuove

istruzioni per manipolare vettori d’interi (max

64bit)

Pentium II:

II: (1997, 7M transistor) – Piu’

Piu’ efficiente

implementazione del processore

Pentium III:

III: (1999, 8,2M transistor) – Nuove

istruzioni per manipolare vettori di interi e

floating point (max 128bit)

❍

Le ultime versioni raggiungono i 24M transistor a causa

dell’

dell’inclusione della cache L2 nel processore

Pentium 4:

4: (2001, 42M transistor) – 144 nuove

istruzioni per vettori interi e floating point

I processori Interl moderni sono CISC con un “cuore”

cuore”

RISC

Introduzione

Tabulating machine

(H. Hollerith, 1889)

Harvard Mark I

(IBM, H. Aiken, 1944)

53

ENIAC (Electronic Numerical Integrator and

Calculator)

Difference Engine

(C. Babbage, 1822)

Introduzione

54

Introduzione

56

ENIAC

Primo computer elettronico di tipo generalgeneral-purpose

(programmabile)

programmabile)

1943 John Mauchly e J. Presper Eckert Moore

School of Electrical Engineering University of

Pennsylvania

❍

❍

Calcoli balistici (WW2)

Completata nel 1946

25x2

.5metri

metri (a forma di U)

25x2.5

18.000 tubi a vuoto

30 tonnellate,

tonnellate, 140kW

20 1010-digit registri,

registri,

❍ ~60 cm a registro

1900 addizioni al secondo

Programmata manualmente tramite interruttori

Introduzione

55

Macchina di von Neumann/Turing

La Macchina di von Neumann

1946 EDVAC, Princeton Institute for Advanced

Studies

❍

Completata nel 1952

Concetto di programma memorizzato

Unità logicaaritmetica

Memoria principale per dati e istruzioni

❍ Dati ed istruzioni codificate in binario

Memoria

Principale

ALU opera su dati

Sistema di

I/O

Unità di

controllo di

programma

Unità

Unità di controllo che “interpreta”

interpreta” le istruzioni in

memoria e le esegue

I sistemi di input e output sono controllati

dall’

dall’unità

unità di controllo

CPU

Introduzione

57

Transistors

Introduzione

58

Primi Calcolatori Commerciali

1947 W. Shockley, J.

Bardeen,

Bardeen, W. Brattain nei

Bell Lab. in 1947

❍

❍

Minori dimensioni

Maggiore affidabilita’

affidabilita’

UNIVAC (Remington-Rand, 1951)

IBM 701 (IBM, 1952)

Introduzione

59

Introduzione

60

Integrated Circuit (IC)

Primo Microprocessore

1958 - Jack Kilby:

Kilby: integrazione di un transistor,

1971 Intel 4004

❍ 108 KHz, 0.06 MIPS

❍ 2300 transistors (10 microns)

❍ Larghezza del bus: 4 bits

❍ Memoria indirizzabile:

indirizzabile: 640

bytes

❍ Sviluppato per un calcolatore

della Busicom

resistenze e capacita’

capacita’ iun singolo chip a

semiconduttore

Introduzione

61

Introduzione

Primi Personal Computer

Primi Personal Computer

1977

1977-Apple II: Steve Jobs, Steve Wozniak

1981 IBM PC: Intel 8088, 4.77MHz,

4.77MHz, 16Kb RAM, 2

Motorola 6502 CPU, 48Kb RAM

62

160Kb floppy disks

Introduzione

63

Introduzione

64

Primi Personal Computer

Anni ‘80

1973: PC Alto Xerox PARC

❍ Mouse, Ethernet, grafica

bitbit-mapped, icone,

icone, menu,

WYSIWG editing

Da IC a VLSI

VLSI

Introduzione di una nuova architettura per i

processori:

processori: RISC (Reduced Instruction Set

Computer)

Laboratori Xerox:

❍ LocalLocal-area networking

❍ Laser printing

❍ …

❍

❍

❍

IBM: John Cocke

UC Berkeley: David Patterson

Stanford: John Hennessy

Commercializzazione Processori RISC nel 1985

❍ MIPS: MIPS, Sun: Sparc,

Sparc, IBM: Power RISC, HP: PAPARISC, DEC: Alpha

Competizione RISCRISC-CISC (complex instruction set

computer), principalmente processori Intel x86

Introduzione

65

Generazioni di Computer

Generazione

Data

Tecnologia

Introduzione

66

Evoluzione della potenza di calcolo (MIPS)

Prestazioni

per unita’

di costo

Tubi a

1

1950 - 1959

2

1960 - 1968 Transistor

3

1968 - 1977 IC

4

1978 - ?

vuoto

LSI/VLSI

1

35

900

2,400,000

(“The Cooler the Better: New Directions in the Nomadic Ages,” Computer, April 2001.)

Introduzione

67

Introduzione

68

Evoluzione del numero di transistor nelle CPU

Intel

Evoluzione della capacita’ delle memorie

DRAM (1 Chip DRAM)

anno dimensione

1980

64k

1983

256k

1986

1M

1989

4M

1992

16M

1996

64M

2000

256M

x2 transistors/chip

ogni 1.5 anni

Introduzione

69

Gap Processore-Memoria

1000

IC technology:

clock rate, potenza,

potenza, densita’

densita’

CPU

100

⇓ permettono

Miglioramenti nell’

nell’architettura dei calcolatori:

calcolatori:

Gap cresce del 50%

ogni anno

istruzioni per ciclo,

ciclo, pipeline, cache, MMX

10

⇓ Spinti da

DRAM

X2/10anni

DRAM

Mercato di massa:

massa:

vantaggio competitivo,

competitivo, applicazioni

2000

1995

1990

1985

1

1980

70

Fattori Determinanti

µProc

x2/1.5anni

Performance

Introduzione

Tempo

Introduzione

71

Introduzione

72

Fattori Determinanti

Calcolatori General Purpose

Applicazioni determinano i fattori

❍ Simulazioni numeriche:

numeriche: floatingfloating-point, banda di memoria

❍ Appl.

Appl. Transazionali:

Transazionali: I/O, matematica intera

❍ Appl.

Appl. Multimediali:

Multimediali: estensioni multimediali

Applicazioni:

Applicazioni: commerciali (int.), scientifiche (FP,

grafica),

grafica), home (int., audio, video, grafica)

grafica)

❍

❍

Applicazioni e le prestazioni

❍ Si potrebbe eseguire il tutto in meta’

meta’ tempo?

❍ La memoria richiesta dalle applicazioni cresce in

continuazione:

continuazione:

❍

SO impatta l’architettura del calcolatore

RISCRISC-based Unix workstation vs x86x86-based PC: (1) unita’

unita’

vendute sono in rapporto 100:1, (2) enfasi sulle prestazioni

– Impatto di Linux?

1.51.5-2 per annno

❍

Compatibilita’

Compatibilita’ del software

Rapida obsoloscenza

Importanza del Sistema Operativo

Linguaggi ad alto livello sostituiscono gli assembler

Importanza dei Compilatori

Importanza della compatibilita’

compatibilita’ e facilita’

facilita’ d’uso

Importanza della domanda/fetta di mercato

❍ E’ possibile ripagare gli investimenti in ricerca?

ricerca?

Introduzione

73

Calcolatori Embedded

Introduzione

74

Calcolatori Embedded

Tipicamente senza FP MMU

❍ Grande varieta’

varieta’ di architetture,

architetture, prestazioni,

prestazioni, periferiche

❍ Compatibilita’

Compatibilita’ non e’

e’ un problema.

problema. Piu’

Piu’ importante e’ il

consumo di potenza

Tempo di vita piu’

piu’ lungo:

lungo:

microprocessori a 44- or 88-bit ancora in uso

Grandi volumi (~miliardi

(~miliardi)) a prezzi bassi ($5($5-$40)

Trend: costi decrescenti,

decrescenti, crescente numero di

funzionalita’

funzionalita’

Introduzione

75

Introduzione

76