Università degli Studi di Bologna

Seconda Facoltà di Ingegneria - Sede di Cesena

C.d.L. in Ingegneria Elettronica e delle Telecomunicazioni

Modelli circuitali gerarchici SPICE

per la simulazione di logiche dinamiche

Laboratorio di Elettronica L-A (prof. C. Fiegna)

Anno Accademico 2008/09

Data esecuzione: 18 maggio 2009

Marco

Alessandrini

Alessandro

Callozzo

Lorenzo

Minghini

0000281742

[email protected]

0000286147

[email protected]

0000274090

[email protected]

Sommario

Nella presente esercitazione si utilizzerà l’esempio della descrizione di logiche Domino per avere un primo approccio con la realizzazione gerarchica di

modelli circuitali, che è alla base di qualsiasi progetto di circuiti integrati. Si

realizzeranno blocchi circuitali parametrici di granularità superiore ai transistori visti nelle esercitazioni precedenti, e li si utilizzeranno per completare in

modo intuitivo circuiti anche complessi.

=

$

CC

BY:

\

Modelli SPICE per simulare logiche dinamiche

Indice

1 Dati di ingresso

2

2 Simulazione di inverter dinamico

3

3 Simulazione di porta logica Domino

9

4 Simulazione di cascata di porte Domino

11

Elenco delle figure

15

Riferimenti bibliografici

15

1

Dati di ingresso

Parametri elettrici del circuito.

• Tensione di alimentazione: VDD = 5 V.

• Capacità di carico: Cload = 0, 1 pF.

Parametri elettrici dei MOS.

• Conducibilità intrinseca (nMOS): KPN = 80 µA/V2 .

• Conducibilità intrinseca (pMOS): KPP = 40 µA/V2 .

• Spessore dell’ossido di gate: tOX = 150 Å.

• Tensione di soglia: VTN = −VTP = 1 V.

• Capacità di giunzione (per unità di area): Cj = 3, 6 · 10−4 F/m2 .

• Capacità di giunzione (per unità di perimetro): CjSW = 2, 1 · 10−10 F/m.

Parametri geometrici dei MOS.

• Lunghezza minima del canale: LM IN = 1, 0 µm

• Larghezza del canale (inverter dinamico): WNIN V dyn = WPIN V dyn = 1 µm

• Larghezza del canale (nMOS dell’inverter statico): WNIN V stat = 1 µm

• Larghezza del canale (pMOS dell’inverter statico): WPIN V stat = 2 µm

• Lunghezza giunzioni di drain e source (rettangolari): PD = PS = 3LM IN

Metodo analitico. Il circuito è simulato con il software P-SPICE, parte costitutiva dell’ambiente di sviluppo OrCAD. Grazie ad esso si implementano le netlist

del circuito, potendo analizzare i grafici delle simulazioni plottando le grandezze

d’interesse ed effettuando le misure più opportune.

Indice

2

=

$

CC

BY:

2

\

Modelli SPICE per simulare logiche dinamiche

Simulazione di inverter dinamico

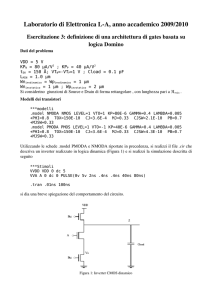

(a) Circuito

(b) Netlist SPICE

Figura 1: Inverter dinamico

1) Utilizzando le schede .model PMODA e NMODA qui riportate:

*** MODELLI

.model NMODA NMOS LEVEL=1 VTO=1 KP=80E-6 GAMMA=0.4 LAMBDA=0.005

+PHI=0.8 TOX=150E-10 CJ=3.6E-4 MJ=0.33 CJSW=2.1E-10 PB=0.7

+MJSW=0.33

.model PMODA PMOS LEVEL=1 VTO=-1 KP=40E-6 GAMMA=0.4 LAMBDA=0.005

+PHI=0.8 TOX=150E-10 CJ=3.6E-4 MJ=0.33 CJSW=4.3E-10 PB=0.7

+MJSW=0.33

si realizzi il file .cir che descriva un inverter realizzato in logica dinamica

(figura 1(a)) e si realizzi la simulazione descritta di seguito:

***Stimoli

VVDD VDD 0 dc 5

VVA A 0 dc 0 PULSE(0v 5v 2ns .4ns .4ns 40ns 80ns)

.tran .01ns 100ns

La simulazione dell’inverter dinamico è stata effettuata all’interno della seguente

netlist SPICE:

* Inverter

*** MODELLI NMOS E PMOS ***

.model NMODA NMOS LEVEL=1 VTO=1 KP=80E-6 GAMMA=0.4 LAMBDA=0.005

+PHI=0.8 TOX=150E-10 CJ=3.6E-4 MJ=0.33 CJSW=2.1E-10 PB=0.7

+MJSW=0.33

.model PMODA PMOS LEVEL=1 VTO=-1 KP=40E-6 GAMMA=0.4 LAMBDA=0.005

+PHI=0.8 TOX=150E-10 CJ=3.6E-4 MJ=0.33 CJSW=4.3E-10 PB=0.7

+MJSW=0.33

*** SOTTOCIRCUITI ***

* INVERTER STATICO

.subckt INV_CMOS VDD IN OUT PARAMS: Wp=2u Wn=1u

MPI OUT IN VDD VDD PMODA W={Wp} L=1u AS=6e-12 AD=6e-12 PS=10e-6 PD=10e-6

MNI OUT IN 0 0 NMODA W={Wn} L=1u AS=3e-12 AD=3e-12 PS=8e-6 PD=8e-6

.ends

* INVERTER DINAMICO

.subckt INV_DOM VDD IN OUT PARAMS: Wd=1u CLK=20ns

2 Simulazione di inverter dinamico

3

MP OUT

MN 2 1

MA OUT

VPHI 1

.ends

=

$

CC

BY:

\

Modelli SPICE per simulare logiche dinamiche

1 VDD VDD PMODA W={Wd} L=1u AS=3e-12 AD=3e-12 PS=8e-6 PD=8E-6

0 0 NMODA W={Wd} L=1u AS=3e-12 AD=3e-12 PS=8e-6 PD=8E-6

IN 2 0 NMODA W={Wd} L=1u AS=3e-12 AD=3e-12 PS=8e-6 PD=8E-6

0 dc 5 PULSE(5V 0V 0ns .1ns .1ns {clk/2} {clk})

*** NETLIST ***

XINVD 1 2 3 INV_DOM

*** STIMOLI ***

VVDD 1 0 dc 5

VVA 2 0 dc 0 PULSE(0v 5v 2ns .4ns .4ns 40ns 80ns)

*** CAPACITA’ DI CARICO ***

Cload 3 0 0.1p

*** SIMULAZIONE DEL CIRCUITO ***

.tran .01ns 100ns

.probe V(2), V(3)

.end

I risultati della simulazione sono in figura 2.

* Esercitazione 3

Date/Time run: 06/06/09 09:38:05

Temperature: 27.0

(A) ES3-1_0.dat (active)

7.0V

5.0V

0V

-2.0V

V(2)

7.0V

5.0V

0V

SEL>>

-2.0V

0s

20ns

40ns

60ns

80ns

100ns

V(3)

Date: June 06, 2009

Time

Page 1

Time: 09:38:47

Figura 2: Inverter dinamico - Andamento delle tensioni (da netlist in fig. 1(b))

La successiva simulazione, comprensivi degli effetti della corrente inversa di saturazione delle giunzioni IS , ha prodotto le forme d’onda in figura 3 avendo modificato

il modello dell’nMOS con l’aggiunta del parametro IS:

* Inverter con IS

*** MODELLI NMOS E PMOS ***

.model NMODA NMOS LEVEL=1 VTO=1 KP=80E-6 GAMMA=0.4 LAMBDA=0.005

+PHI=0.8 TOX=150E-10 CJ=3.6E-4 MJ=0.33 CJSW=2.1E-10 PB=0.7

+MJSW=0.33 IS=1.0E-5

[...]

2 Simulazione di inverter dinamico

4

=

$

CC

BY:

\

Modelli SPICE per simulare logiche dinamiche

* Esercitazione 3

Date/Time run: 06/01/09 10:33:39

Temperature: 27.0

(A) ES3-1_0.dat (active)

7.0V

5.0V

0V

SEL>>

-2.0V

V(2)

7.0V

5.0V

0V

-2.0V

0s

20ns

40ns

60ns

80ns

100ns

V(3)

Time

Page 1

Date: June 01, 2009

Time: 10:35:52

Figura 3: Inverter dinamico - Andamento delle tensioni con effetto della corrente IS (da netlist in

fig. 1(b))

2) Si dia una breve spiegazione del comportamento del circuito. (1 )

Il clock φ(2 ) fornito all’inverter ha periodo pari a 20 ns; in totale l’ingresso di

clock è alimentato per 80 ns, quindi saranno visualizzati quattro periodi completi di precharge ed evaluation. In questi periodi si valuta sia il caso di VA =0 10 , sia

VA =0 00 .

Nel semiperiodo in cui VA è alto si ha un collegamento diretto verso massa

quando φ =0 10 . Durante la fase di precharge viene caricata Cload , mentre in

evaluation la stessa capacità si scarica fino a 0 V.

Nel semiperiodo in cui VA è basso non sarà disponibile un collegamento diretto

verso massa, né verso altre alimentazioni: quindi l’uscita, flottante, deve mantenersi

autonomamente costante a 0 10 . Nella figura 2 si può notare che su V(3) si verifica

una piccola perdita di carica in questa fase.

L’introduzione del parametro IS, associato alle correnti di perdita al nodo di

uscita, mostra gli effetti (amplificati rispetto alla realtà della tecnologia) della perdita di carica su Z, cioè una riduzione della tensione sul nodo durante la fase di

evaluation rispetto al valore imposto in precharge. Possiamo valutare tale riduzione

di Vout utilizzando la formula:

Tdist =

Cload · ∆Vdist

IS

⇒

∆Vdist =

Tdist · IS

10 ns · 10 µA

=

= 1V

Cload

0, 1 pF

In figura 3 è evidente che, al termine del periodo di evaluation (agli istanti t = 60 ns

e t = 80 ns), la perdita di tensione su V(3) sia proprio pari a 1 V.

1 Si osservi che durante la fase di evaluation, con φ =0 10 , il nodo di uscita si trova in condizione

di alta impedenza. Nel caso le correnti di leakage dei transistori nMOS che lo connettono a massa

fossero particolarmente significative, si rischierebbe una scarica non voluta del valore di Z. Questo

è il caso ad esempio, delle più avanzate tecnologie digitali a 130 nm e 90 nm, che presentando

valori di VDD molto bassi (da 1, 8 V a 1, 2 V) sono particolarmente soggette a correnti sottosoglia.

Per visualizzare tale fenomeno nella simulazione, si provi ad aggiungere alla .model dei transistori

nMOS il parametro IS=1.0e5, che descrive la corrente inversa di saturazione delle giunzioni e viene

usato come base per calcolare le correnti di perdita. Si tenga presente che IS = 10 µA è un valore

assolutamente irrealistico dati i parametri dell’esercizio, ma è utile per comprendere il fenomeno.

2 Convenzionalmente chiameremo i due sottoperiodi di φ coi nomi inglesi: precharge quando

φ = 0, evaluation quando φ = 1.

2 Simulazione di inverter dinamico

5

=

$

CC

BY:

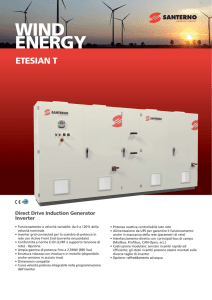

(a) Circuito

\

Modelli SPICE per simulare logiche dinamiche

(b) Netlist SPICE

Figura 4: Inverter dinamico con circuito di keeper

3) Nel caso il valore di φ sia tale da rendere intollerabile il fenomeno di

scarica di Z (che viene detto charge sagging ), è possibile rendere stabile

l’uscita col circuito di figura 4(a), detto keeper. Si realizzi un keeper come

.SUBCKT (usando un inverter CMOS descritto a sua volta come .SUBCKT) e

si verifichi il funzionamento dell’inverter dinamico cosı̀ realizzato. (3 ) Il

circuito di keeper è stato aggiunto alla precedente netlist con le seguenti istruzioni,

relative al modello, all’istanziazione e alla connessione agli altri sottocircuiti:

* Inverter con keeper

[...]

* KEEPER

.subckt KEEPER VDD IN OUT PARAMS: Wp=1u

MP OUT 1 VDD VDD PMODA W={Wp} L=1u AS=3e-12 AD=3e-12 PS=8e-6 PD=8E-6

XINV_Keeper VDD IN 1 INV_CMOS

.ends

*** NETLIST ***

XINVD 1 2 3 INV_DOM

XK 1 3 3 KEEPER

*** STIMOLI ***

[...]

Simulando il circuito con gli stimoli forniti in precedenza, si sono ottenuti i risultati

in figura 5. Da un rapido confronto con quanto avveniva senza keeper (figura 3)

si nota che è quasi scomparsa la perdita di tensione sul nodo d’uscita VZ (V(3)),

grazie all’azione del pMOS che fornisce all’uscita un valore 0 10 forte, scongiurando

lo stato di alta impedenza che affligge la versione tradizionale.

Un inconveniente riscontrato è la scarica più lenta, quando il nodo d’uscita deve

avere tensione 0 V: il colpevole è proprio il pMOS del keeper, che con la propria

conduttività ostacola la scarica del nodo d’uscita. Infatti il pMOS dovrebbe essere

poco conduttivo per non rallentare la scarica di VZ , ed evidentemente il valore scelto

Wp = 1 µm non è il migliore possibile. Il dimensionamento viene fatto riassegnando

Wp il quale, essendo legato alla corrente del MOS da proporzionalità diretta, deve

essere piccolo per avere bassa conduttività del dispositivo. Sono state effettuate due

ulteriori prove:

• una prova con Wp = 2 µm (figura 6), nella quale è marcato l’effetto di corruzione della funzione logica provocato dall’eccessiva conducibilità del MOS;

3 Si

faccia attenzione a dimensionare il parametro Wp del transistore del keeper in maniera da

non compromettere il funzionamento del circuito: il transistore dovrà essere weak in modo da

sostenere il nodo quando è in alta impedenza, ma non deve poter dominare la rete di pull-down

al momento della commutazione.

2 Simulazione di inverter dinamico

6

=

$

CC

BY:

\

Modelli SPICE per simulare logiche dinamiche

* Esercitazione 3

Date/Time run: 06/01/09 10:28:23

Temperature: 27.0

(A) ES3-1_1.dat (active)

7.0V

5.0V

0V

-2.0V

V(2)

7.0V

5.0V

0V

SEL>>

-2.0V

0s

20ns

40ns

60ns

80ns

100ns

V(3)

Date: June 01, 2009

Time

Page 1

Time: 10:32:13

Figura 5: Inverter con keeper - Andamento delle tensioni con Wpkeeper = 1 µm (da netlist in

fig. 4(b))

• una prova con Wp = 0, 5 µm (figura 7) che ha prodotto un risultato sostanzialmente pari a quello atteso: oltre a correggere i difetti dell’uscita flottante,

non danneggia i fronti di discesa nei casi di uscita bassa.

Entrambi i test confermano, inoltre, che il miglior funzionamento si ha dal compromesso scelto nel dimensionamento di Wp scelto per il transistor: infatti, calando

troppo Wp si ritorna alla condizione iniziale di uscita flottante4 , mentre aumentando

troppo Wp si corrompe lo stato basso della funzione logica, che non ha più tensione

0 V.

4 Il MOS diventa cosı̀ poco conduttivo che la scarica nei fronti di discesa è perfetta, ma il

mantenimento della carica sul nodo d’uscita a livello alto è impossibile perché non transita corrente.

2 Simulazione di inverter dinamico

7

=

$

CC

BY:

\

Modelli SPICE per simulare logiche dinamiche

* Esercitazione 3

Date/Time run: 06/06/09 09:41:43

Temperature: 27.0

(A) ES3-1_1.dat (active)

7.0V

5.0V

0V

-2.0V

V(2)

7.0V

5.0V

0V

SEL>>

-2.0V

0s

20ns

40ns

60ns

80ns

100ns

V(3)

Time

Page 1

Date: June 06, 2009

Time: 09:41:54

Figura 6: Inverter con keeper - Andamento delle tensioni con Wpkeeper = 2 µm (da netlist in

fig. 4(b))

* Esercitazione 3

Date/Time run: 06/06/09 09:42:20

Temperature: 27.0

(A) ES3-1_1.dat (active)

7.0V

5.0V

0V

-2.0V

V(2)

7.0V

5.0V

0V

SEL>>

-2.0V

0s

20ns

40ns

60ns

80ns

100ns

V(3)

Date: June 06, 2009

Time

Page 1

Time: 09:42:32

Figura 7: Inverter con keeper - Andamento delle tensioni con Wpkeeper = 0, 5 µm (da netlist in

fig. 4(b))

2 Simulazione di inverter dinamico

8

=

$

CC

BY:

3

\

Modelli SPICE per simulare logiche dinamiche

Simulazione di porta logica Domino

4) Si provi a realizzare e simulare un circuito composto dalla cascata

di due porte NOT dinamiche (sfruttando i sottocircuiti descritti in precedenza). I risultati ottenuti sono corretti? Perché? La netlist è stata

aggiornata come segue:

* Cascata di due NOT dinamici

[...]

*** NETLIST ***

XINVD 1 2 3 INV_DOM

XINV2 1 3 4 INV_DOM

*** STIMOLI ***

[...]

*** CAPACITA’ DI CARICO ***

Cl_1 3 0 0.1p

Cl_2 4 0 0.1p

[...]

La simulazione ha prodotto i risultati in figura 8. Si nota una variazione anomala

del valore sull’uscita complessiva V(4) quando V(3) ha valore basso: infatti V(4)

non riesce a sostenere il valore alto (che dovrebbe avere, negando V(3)) e alla fine

del periodo di evaluation si trova di ben 2 V al di sotto dei 5 V attesi.

Il comportamento della cascata di NOT dinamici è causato dal fatto che il MOS

di comando del secondo NOT non si spegne istantaneamente all’inizio dell’evaluation: deve attendere la fine della transizione all’uscita del primo NOT. Solo quando

questo nodo avrà tensione al di sotto della soglia, allora l’uscita generale assumerà il

valore definitivo. Quindi, durante la transizione, essa ha tutto il tempo di scaricarsi

attraverso il secondo NOT, che sta lentamente spegnendosi.

Il problema (irrisolvibile) ha origine quando l’uscita della prima logica ha valore

0 0

1 all’inizio della fase di evaluation, quindi sono accettabili solo i casi in cui:

• gli ingressi rimangano costanti durante l’evaluation;

• le transizioni degli ingressi in evaluation seguano solo lo schema 0 V → VDD .

* Esercitazione 3

Date/Time run: 06/01/09 10:41:50

Temperature: 27.0

(A) ES3-2_0.dat (active)

5.0V

0V

V(2)

5.0V

0V

V(3)

5.0V

0V

SEL>>

0s

20ns

40ns

60ns

80ns

100ns

V(4)

Date: June 01, 2009

Time

Page 1

Time: 10:44:09

Figura 8: Cascata di inverter dinamici - Andamento delle tensioni V(2)=VA , V(3)=VZ1 , V(4)=VZ2

3 Simulazione di porta logica Domino

9

=

$

CC

BY:

(a) Circuito

\

Modelli SPICE per simulare logiche dinamiche

(b) Netlist SPICE

Figura 9: Porta logica Domino

5) Per evitare il problema precedente, è possibile realizzare una struttura

Domino, composta da un invertitore dinamico seguito da un invertitore

statico (figura 9(a)). Si realizzi un file .cir che descrive tale struttura,

ancora composto dai sottocircuiti definiti in precedenza. Si supponga

per semplicità che non sia necessario mantenere il keeper. La precedente

netlist è modificata solo nel nuovo sottocircuito XINVS, che sostituisce XINV2:

* Cascata di NOT dinamico e NOT statico (senza keeper)

[...]

*** NETLIST ***

XINVD 1 2 3 INV_DOM

XINVS 1 3 4 INV_CMOS

[...]

I risultati della simulazione sono plottati in figura 10.

* Esercitazione 3

Date/Time run: 06/01/09 10:46:08

Temperature: 27.0

(A) ES3-2_1.dat (active)

5.0V

0V

SEL>>

V(2)

5.0V

0V

V(3)

5.0V

0V

0s

20ns

40ns

60ns

80ns

100ns

V(4)

Date: June 01, 2009

Time

Page 1

Time: 10:47:23

Figura 10: Porta logica Domino - Andamento delle tensioni (da netlist in fig. 9(b))

3 Simulazione di porta logica Domino

10

4

=

$

CC

BY:

\

Modelli SPICE per simulare logiche dinamiche

Simulazione di cascata di porte Domino

Figura 11: Cascata di porte logiche Domino

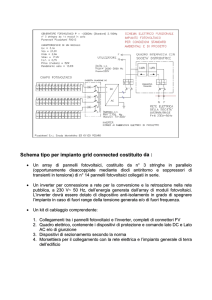

6) Si descriva ora un circuito in cui si realizza una cascata di stadi di

inversione, alternativamente dinamici e statici (figura 11). Si osservi che

la presenza dell’invertitore statico fa sı̀ che durante la fase di precarica

(φ = 0) l’uscita di ogni doppio stadio dinamico-statico sia 0 V, e durante

la fase di valutazione (φ = VDD ) possa solo commutare da 0 a VDD . Si

spieghino le ragioni teoriche, e le si verifichino nel circuito, che permettono di utilizzare la cascata senza manifestare i problemi di cui al caso

precedente (cascata di soli elementi dinamici). La struttura che alterna un

blocco dinamico a uno statico risolve il problema delle transizioni ammesse durante la fase di evaluation (una dimostrazione è nelle tensioni mostrate in figura 10),

infatti:

• l’inverter dinamico accetta in ingresso solo transizioni 0 V → VDD ;

• l’inverter dinamico, allora, ha in uscita solo transizioni VDD → 0 V;

• l’inverter statico nega l’uscita dell’inverter statico, quindi propone un segnale

con sole transizioni 0 V → VDD .

Quindi l’uscita di un inverter statico può pilotare tranquillamente un qualunque

inverter dinamico, e in generale n logiche Domino.

Si spieghi infine perché negli stadi dinamici (escluso il primo) non è

necessario il transistore nMOS che isola la rete di pull-down durante la

fase di valutazione (φ = VDD ). Il transistor nMOS che isola la rete di pull-down

non è necessario perché, per la struttura del circuito, non è mai presente un percorso

conduttivo tra alimentazione e massa tale da porli in cortocircuito: la protezione,

quindi, diventa superflua. Infatti:

• in precharge la prima logica dinamica carica la C1 1 (nodo 3), quindi l’inverter

statico propone un valore basso all’ingresso del secondo NOT dinamico (nodo

4). Questi, allora, ha il nMOS di comando spento, quindi non c’è cortocircuito

tra VDD e massa;

• in evaluation tutti i pMOS dei NOT dinamici sono spenti, perché φ =0 10 , e

parimenti manca un percorso conduttivo che cortocircuiti l’alimentazione.

4 Simulazione di cascata di porte Domino

11

=

$

CC

BY:

\

Modelli SPICE per simulare logiche dinamiche

Figura 12: Cascata di porte logiche Domino (come da netlist SPICE)

7) Si realizzi e si simuli, con le stesse specifiche di analisi del transitorio

descritte in precedenza, il circuito di figura 11 utilizzando nella netlist

esclusivamente come elementi:

1. un sottocircuito che descriva il primo stadio NOT dinamico (a tre transistori)

detto INV DOM (Inverter Domino);

2. un sottocircuito che descriva il secondo stadio NOT dinamico (a due transistori) detto INV DOM2 (Inverter Domino 2 );

3. un sottocircuito che descriva un inverter CMOS statico detto INV CMOS;

4. capacità di carico delle interconnessioni poste tutte al valore convenzionale

0, 1 pF.

* Cascata di porte logiche Domino

*** MODELLI NMOS E PMOS

[...]

*** SOTTOCIRCUITI ***

* INVERTER STATICO

.subckt INV_CMOS VDD IN OUT PARAMS: Wp=2u Wn=1u

MPI OUT IN VDD VDD PMODA W={Wp} L=1u AS=6e-12 AD=6e-12 PS=10e-6 PD=10e-6

MNI OUT IN 0 0 NMODA W={Wn} L=1u AS=3e-12 AD=3e-12 PS=8e-6 PD=8e-6

.ends

* INVERTER DINAMICO

.subckt INV_DOM VDD IN OUT PARAMS: Wd=1u CLK=20ns

MP OUT 1 VDD VDD PMODA W={Wd} L=1u AS=3e-12 AD=3e-12 PS=8e-6 PD=8E-6

MN 2 1 0 0 NMODA W={Wd} L=1u AS=3e-12 AD=3e-12 PS=8e-6 PD=8E-6

MA OUT IN 2 0 NMODA W={Wd} L=1u AS=3e-12 AD=3e-12 PS=8e-6 PD=8E-6

VPHI 1 0 dc 5 PULSE(5V 0V 0ns .1ns .1ns {clk/2} {clk})

.ends

* INVERTER DINAMICO A DUE MOS

.subckt INV_DOM2 VDD IN OUT PARAMS: Wd=1u CLK=20ns

MP OUT 1 VDD VDD PMODA W={Wd} L=1u AS=3e-12 AD=3e-12 PS=8e-6 PD=8E-6

MA OUT IN 0 0 NMODA W={Wd} L=1u AS=3e-12 AD=3e-12 PS=8e-6 PD=8E-6

VPHI 1 0 dc 5 PULSE(5V 0V 0ns .1ns .1ns {clk/2} {clk})

.ends

*** NETLIST

XINVD1 1 2

XINVS1 1 3

XINVD2 1 4

XINVS2 1 5

***

3 INV_DOM

4 INV_CMOS

5 INV_DOM2

6 INV_CMOS

4 Simulazione di cascata di porte Domino

12

=

$

CC

BY:

\

Modelli SPICE per simulare logiche dinamiche

*** STIMOLI ***

VVDD 1 0 dc 5

VVA 2 0 dc 0 PULSE(0v 5v 2ns .4ns .4ns 40ns 80ns)

VPHI 7 0 dc 5 PULSE(5V 0V 0ns .1ns .1ns {10 ns} {20ns})

*** CAPACITA’ DI CARICO ***

Cl_1 3 0 0.1p

Cl_2 4 0 0.1p

Cl_3 5 0 0.1p

Cl_4 6 0 0.1p

*** SIMULAZIONE DEL CIRCUITO ***

.tran .01ns 100ns

.probe V(7), V(2), V(3), V(4), V(5), V(6)

.end

Il risultato della simulazione è proposto in figura 13. In particolare si notano le tensioni d’uscita degli stadi dinamici (V(3) e V(5)) afflitte dai problemi di scarica legati

a IS ; queste tensioni non influiscono minimamente sul risultato finale della cascata

V(6), grazie all’azione degli stadi statici intermedi. Una conseguenza facilmente

individuabile, però, è il ritardo introdotto da ogni blocco, che causa una delazione

dell’inizio del fronte di commutazione quantificabile in circa 2, ns tra l’inizio della

commutazione su V(3) e l’azione corrispondente su V(6).

8) Sarebbe possibile utilizzare il secondo stadio dinamico senza il transistore nMOS connesso a φ nel caso si volesse realizzare funzioni logiche più complesse di un singolo inverter (quali ad esempio la funzione

Z = A · B + C descritta nella esercitazione precedente)? Perché? Il funzionamento del secondo stadio dinamico senza nMOS pilotato da φ non è garantito

con ogni funzione logica. Nel caso dell’inverter, la presenza di un solo ingresso di

segnale e la certezza che il segnale d’ingresso attivi il relativo MOS in controfase

rispetto al pMOS di φ (grazie alla logica Domino) permette di risparmiare un nMOS

senza correre rischi.

Qualora si volessero realizzare funzioni più complesse, per risparmiare un nMOS

bisognerebbe assicurare che ogni ingresso di comando sia pilotato da una logica Domino: in tale condizione, ogni ingresso vale 0 00 in precharge ed evita il cortocircuito

di VDD a massa. Se anche solo un ingresso è pilotato diversamente, ad esempio

con comando diretto, allora non è possibile garantire che non siano presenti percorsi conduttivi tra alimentazione e massa, rendendo obbligatorio l’uso del nMOS

connesso a φ.

4 Simulazione di cascata di porte Domino

13

=

$

CC

BY:

\

Modelli SPICE per simulare logiche dinamiche

* Esercitazione 3

Date/Time run: 06/01/09 11:26:47

7V

Temperature: 27.0

0V

V(2)

7V

0V

V(7)

5.0V

0V

V(3)

5.0V

0V

V(4)

5.0V

0V

V(5)

5.0V

SEL>>

0V

0s

10ns

V(6)

Date: June 01, 2009

20ns

30ns

40ns

50ns

Time

Page 1

60ns

70ns

80ns

90ns

Time: 11:34:14

Figura 13: Cascata di porte logiche Domino - Andamento delle tensioni V(2)=VA , V(7)=φ,

V(3)=V1 , V(4)=V2 , V(5)=V3 , V(6)=VZ (da netlist in fig. 12)

4 Simulazione di cascata di porte Domino

14

=

$

CC

BY:

\

Modelli SPICE per simulare logiche dinamiche

Elenco delle figure

1

2

3

4

5

6

7

8

9

10

11

12

13

Inverter dinamico . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Inverter dinamico - Andamento delle tensioni (da netlist in fig. 1(b))

Inverter dinamico - Andamento delle tensioni con effetto della corrente IS (da netlist in fig. 1(b)) . . . . . . . . . . . . . . . . . . . . .

Inverter dinamico con circuito di keeper . . . . . . . . . . . . . . . .

Inverter con keeper - Andamento delle tensioni con Wpkeeper = 1 µm

(da netlist in fig. 4(b)) . . . . . . . . . . . . . . . . . . . . . . . . . .

Inverter con keeper - Andamento delle tensioni con Wpkeeper = 2 µm

(da netlist in fig. 4(b)) . . . . . . . . . . . . . . . . . . . . . . . . . .

Inverter con keeper - Andamento delle tensioni con Wpkeeper = 0, 5 µm

(da netlist in fig. 4(b)) . . . . . . . . . . . . . . . . . . . . . . . . . .

Cascata di inverter dinamici - Andamento delle tensioni (come indicate in ascissa) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Porta logica Domino . . . . . . . . . . . . . . . . . . . . . . . . . . .

Porta logica Domino - Andamento delle tensioni (da netlist in fig. 9(b))

Cascata di porte logiche Domino . . . . . . . . . . . . . . . . . . . .

Cascata di porte logiche Domino (come da netlist SPICE) . . . . . .

Cascata di porte logiche Domino - Andamento delle tensioni (da

netlist in fig. 12) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3

4

5

6

7

8

8

9

10

10

11

12

14

Riferimenti bibliografici

[1] David Esseni. Fondamenti di circuiti integrati digitali CMOS. SG Editoriali

Padova, 2006.

\

=

$

CC

BY:

Quest’opera è stata rilasciata sotto la licenza Creative Commons Attribuzione-Non commerciale-Non opere derivate 2.5 Italia. Per leggere

una copia della licenza visita il sito web

http://creativecommons.org/licenses/by-nc-nd/2.5/it/

o spedisci una lettera a Creative Commons, 171 Second Street, Suite

300, San Francisco, California, 94105, USA.

È consentito riprodurre e distribuire liberamente il presente testo, senza apporvi

modifiche e mantenendo sempre riconoscibile il nome degli autori, purché non a scopo di lucro, senza scopi commerciali (direttamente o indirettamente) e per esclusivo

uso personale.

È possibile pubblicare il file o sue parti su siti internet, purché siano citati in

maniera evidente gli autori (Marco Alessandrini, Alessandro Callozzo e Lorenzo

Minghini).

Per qualunque informazione, problematica, suggerimento o reclamo utilizzare

l’indirizzo [email protected].

Elenco delle figure

15