Tecnologie per la memoria e

gerarchie di memoria

Architetture dei Calcolatori

(lettere A-I)

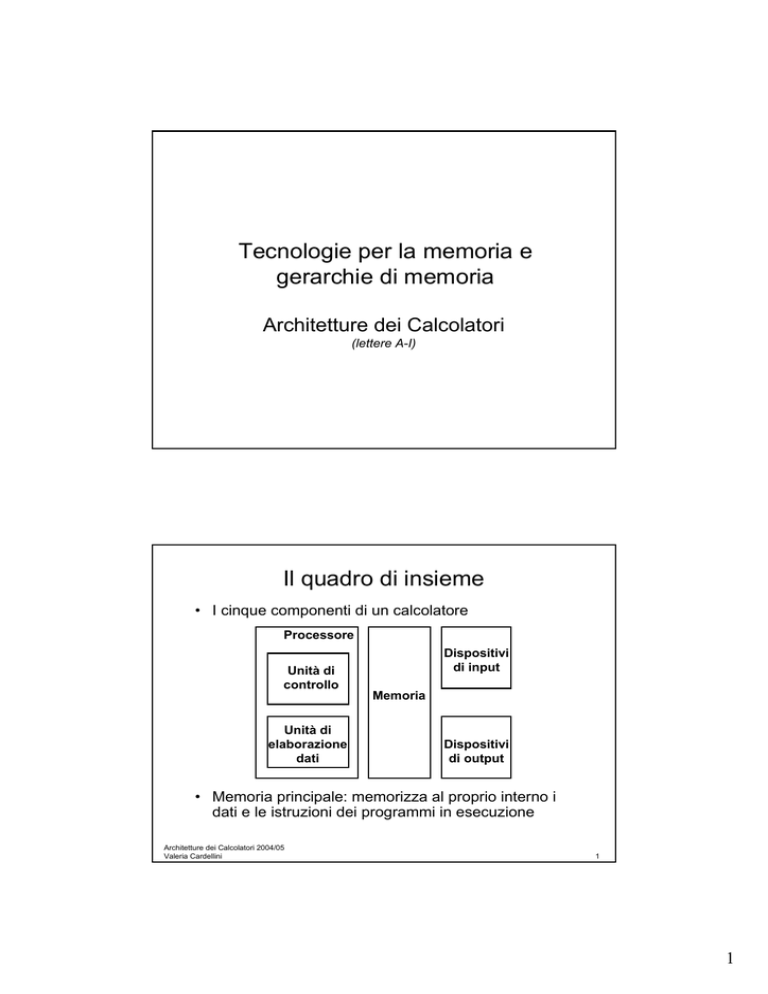

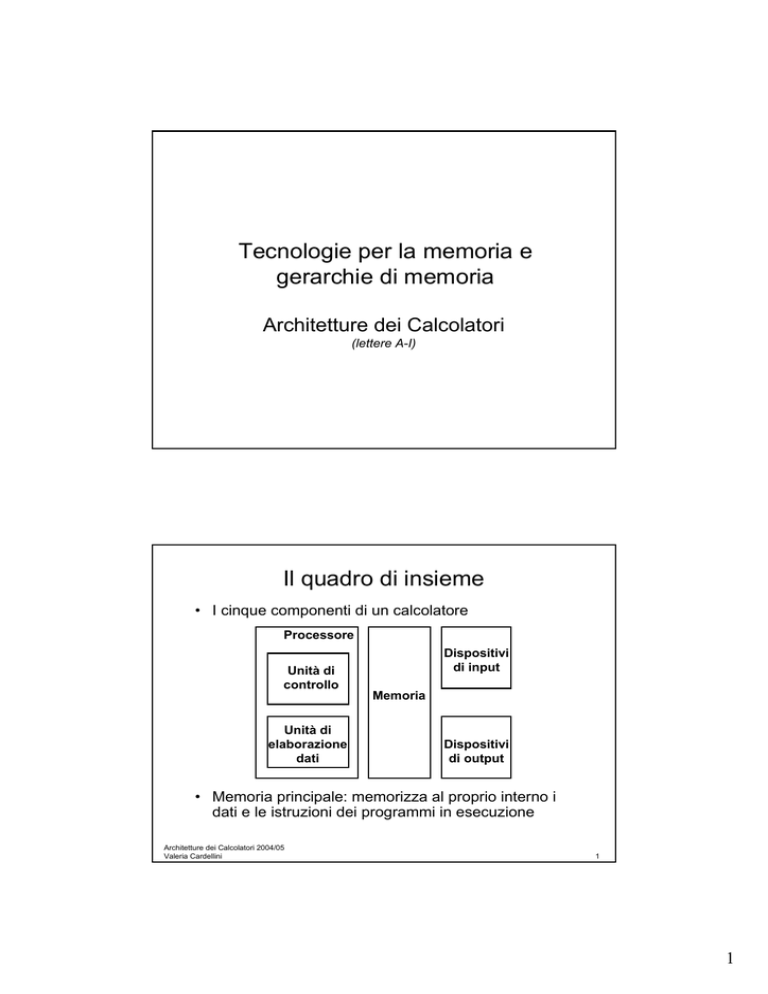

Il quadro di insieme

• I cinque componenti di un calcolatore

Processore

Unità di

controllo

Unità di

elaborazione

dati

Dispositivi

di input

Memoria

Dispositivi

di output

• Memoria principale: memorizza al proprio interno i

dati e le istruzioni dei programmi in esecuzione

Architetture dei Calcolatori 2004/05

Valeria Cardellini

1

1

Un ripasso: clock

• Nei circuiti sequenziali sincroni tutti i cambiamenti di

stato vengono sincronizzati da un segnale (clock)

• Da un clock primario ne vengono ricavati altri per

sfasatura, sottrazione ecc.

• Le transizioni di stato del circuito possono avvenire:

A) In corrispondenza dei livelli

B) In corrispondenza dei fronti (edge-triggered clocking)

Architetture dei Calcolatori 2004/05

Valeria Cardellini

2

Un ripasso: latch D e flip-flop D

C

D

Q

C

_

Q

Q

D

• Il latch D (Delay) quando il segnale di clock C va ad 1

cambia stato e registra nello stato Q il valore

dell’ingresso D; il latch non cambia stato quando C=0

– La porta NOR agisce da invertitore quando l’altro ingresso è 0

• Nel flip-flop D, il valore di D deve essere stabile

quando il clock C cambia

• setup time: prima del cambio di fronte del clock

• hold time: dopo il cambio di fronte del clock

D

Set-up time

Architetture dei Calcolatori 2004/05

C

Valeria Cardellini

Hold time

Setup e hold time

per un flip-flop D

(clock sul fronte di

discesa)

3

2

Registro

• Registro

– Simile ad un flip flop D eccetto

• N bit di ingresso e uscita

• Input Write Enable

Write Enable

Data In

N

– Write Enable:

• Se negato (0): i dati in uscita (Data Out) non

cambiano

• Se asserito (1): i dati in uscita (Data Out)

divengono uguali ai dati in ingresso (Data In)

Data Out

N

CLK

Architetture dei Calcolatori 2004/05

Valeria Cardellini

4

Banco di registri (register file)

• Banco di registri ad accesso rapido per memorizzare

temporaneamente gli operandi usati nelle istruzioni

• Nel MIPS il banco dei registri è composto

RW RA RB

Write Enable 5 5 5

da 32 registri generali

– Due bus di output a 32 bit: busA e busB

– Un bus di input a 32 bit: busW

busW

• Il registro è selezionato da:

32

CLK

32 registri

(da 32 bit)

– RA (numero): seleziona il registro da mettere su busA (dati)

busA

32

busB

32

– RB (numero): seleziona il registro da mettere su busB (dati)

– RW (numero): seleziona il registro che deve essere scritto tramite busW

(dati) quando Write Enable è 1

• Clock (CLK)

– L’input CLK ha influenza soltanto durante le operazioni di scrittura

– Durante le operazioni di lettura, si comporta come un blocco di logica

combinatoria: RA o RB valido → busA o busB valido dopo il tempo di accesso

Architetture dei Calcolatori 2004/05

Valeria Cardellini

5

3

Banco di registri (2)

• Un banco di registri può essere implementato con un

multiplexer per ciascuna porta read, un decoder per

ciascuna porta write ed un array di registri costruiti

partendo da flip-flop D

• Esempio: implementazione di due porte read per un

banco di registri composto da n registri

Read register

number 1

Register 0

Register 1

Register n – 1

M

u

x

Read data 1

M

u

x

Read data 2

Register n

Read register

number 2

Architetture dei Calcolatori 2004/05

Valeria Cardellini

6

Banco di registri (3)

• Esempio: implementazione di una porta write

per un banco di registri composto da n registri

Architetture dei Calcolatori 2004/05

Valeria Cardellini

7

4

Memoria (idealizzata)

Write Enable

• Memoria (schema idealizzato)

– Un bus di input: Data In

– Un bus di output: Data Out

Address

Data In

32

CLK

Data Out

32

• La parola di memoria è selezionata da:

– Indirizzo: seleziona la parola da mettere su Data Out

– Write Enable=1: l’indirizzo seleziona la parola di memoria

che deve essere scritta mediante il bus Data In (operazione

di scrittura)

• Clock (CLK)

– L’input CLK ha influenza soltanto durante le operazioni di

scrittura

– Durante le operazioni di lettura, si comporta come un blocco

di logica combinatoria:

• Indirizzo valido => Data Out valido dopo il tempo di accesso

Architetture dei Calcolatori 2004/05

Valeria Cardellini

8

Principali tecnologie per RAM

• Le memorie RAM sono di due tipi

– Memorie statiche: Static Random Access Memory (SRAM)

– Memorie dinamiche: Dynamic Random Access Memory (DRAM)

• Memorie statiche

– Il singolo elemento corrisponde ad un flip-flop

• Memorie dinamiche

– Il singolo elemento corrisponde ad un condensatore ed un

transistor

– L’informazione è memorizzata sotto forma di carica del

condensatore

– Richiedono un refresh periodico dell’informazione

• Le memorie statiche sono (rispetto a quelle dinamiche)

–

–

–

–

Più veloci

Più costose (6 transistor per bit)

Persistenti (non è richiesto il refresh)

Più affidabili

Architetture dei Calcolatori 2004/05

Valeria Cardellini

9

5

Memoria principale, cache e tecnologie

• Prestazioni della memoria principale

– Latenza

• Tempo di accesso: tempo tra quando arriva la richiesta e la parola

• Tempo di ciclo: tempo tra richieste

– Banda

• La memoria principale è DRAM

– Dinamica in quanto ha bisogno di essere rinfrescata

periodicamente (8 ms)

– Indirizzi di memoria divisi in due parti (memoria come una

matrice 2D):

• RAS o Row Access Strobe

• CAS o Column Access Strobe

• La memoria cache usa SRAM

– No refresh (6 transistor/bit vs. 1 transistor)

Dimensione: DRAM/SRAM = 4-8

Cost/Cycle time: SRAM/DRAM = 8-16

Architetture dei Calcolatori 2004/05

Valeria Cardellini

10

Diagramma logico di un chip SRAM

A

N

WE_L

OE_L

2 N words

x M bit

SRAM

M

D

• Write Enable è solitamente attivo se basso (WE_L)

• Data in and Data out sono combinati per risparmiare piedini

sul chip

– C’è bisogno di un nuovo segnale di controllo, output enable (OE_L)

– WE_L è asserito (Low), OE_L is disasserito (High)

• D serve come input

– WE_L is disasserito (High), OE_L è asserito (Low)

• D serve come output

– WE_L e OE_L sono entrambi asseriti:

• Il risultato non è noto!

Architetture dei Calcolatori 2004/05

Valeria Cardellini

11

6

Buffer three-state

• Un dispositivo a tre stati, in base ad un segnale di

controllo, si comporta:

(b) controllo=1: come circuito chiuso

(c) controllo=0: come circuito aperto

• Tempo di commutazione: pochi nsec

• Consente di usare gli stessi piedini sia per la lettura

che per scrittura

Architetture dei Calcolatori 2004/05

Valeria Cardellini

12

Struttura di una SRAM 4x2

Din[1]

Write enable

Din[0]

D

D

C latch Q

Enable

D

D

D

C latch Q

Enable

D

D

D

C latch Q

Enable

D

D

D

C latch Q

Enable

D

D

C latch Q

Enable

D

C latch Q

Enable

0

2-to-4

decoder

D

C latch Q

Enable

1

Address

D

C latch Q

Enable

2

3

Dout[1]

Dout[0]

Il buffer three-state è incorporato nei flip-flop che formano le celle di

base di una SRAM (buffer controllato dal segnale Enable)

Architetture dei Calcolatori 2004/05

Valeria Cardellini

15

7

Struttura di una SRAM 4Mx8

• Il primo decoder (12-to-4096) genera l’indirizzo per gli 8 array da 4K x

1024 (4K = 4096 = 212)

• Un set di 8 multiplexer con 10 linee di controllo ciascuno è usato per

selezionare 1 bit tra i 1024 (1024 = 210) in ingresso (uscita degli 8 array

da 4Kx1024)

Architetture dei Calcolatori 2004/05

Valeria Cardellini

16

Memoria DRAM

• Cella di memoria con un transistor

– Il condensatore memorizza il contenuto della cella

ed il transistor è usato per accedere alla cella

– La memoria deve essere rinfrescata perché il

condensatore non può tenere la carica per un

tempo indefinito

Architetture dei Calcolatori 2004/05

Valeria Cardellini

17

8

Decodifica su due livelli

• DRAM usa un decoder a due livelli

– Indirizzo di memoria (n bit) suddiviso in row address (n/2 bit)

e column address (n/2 bit)

– Accesso di riga seguito da accesso di colonna

– Segnale di controllo RAS: Row Address Strobe

– Segnale di controllo CAS: Column Address Strobe

• Esempio

Row address

– Memoria DRAM 4Mx1 (4 Mbit) con una matrice 2048x2048

Row

decoder

11-to-2048

2048 × 2048

array

Column latches

Address[10–0]

Column address

Mux

Architetture dei Calcolatori 2004/05

Valeria Cardellini

Dout

18

Decodifica su due livelli (2)

bit (data) lines

r

o

w

Each intersection represents

a 1-T DRAM Cell

RAM Cell

Array

d

e

c

o

d

e

r

row

address

word (row) select

Column Selector &

I/O Circuits

data

column

address

• Row e Column Address insieme:

– Selezionano 1 bit alla volta

Architetture dei Calcolatori 2004/05

Valeria Cardellini

19

9

Refresh nelle DRAM

• Necessario rinfrescare, cioè riscrivere, tutta la DRAM

con periodo T

• Possibile scrivere in un solo ciclo una riga o una

colonna

• Refresh simultaneo di tutti i chip e tutte le schede

Esempio

– T: periodo di refresh

– n: dimensione

(4 ms)

(4MB)

– τ: durata ciclo refresh

– η: overhead

(40ns)

η=(√ n·τ) / T

η = (2048·40·10-9) / (4·10-3) ≈ 2%

Architetture dei Calcolatori 2004/05

Valeria Cardellini

20

Tipi di memoria a semiconduttore

• SRAM (Static RAM): a flip-flop, molto veloce (~5 nsec)

• DRAM (Dynamic RAM): basata su capacità parassite;

richiede refresh, alta densità, basso costo (~70 nsec)

– FPM: selezione a matrice

– EDO: (Extended Data Output) lettura in pipeline, più banda

• SDRAM (Synchronous DRAM)

– Sincrona (scambia dati con il processore in sincronia con un

segnale di clock esterno), prestazioni migliori

•

•

•

•

PROM (Programmable ROM)

EPROM (Erasable PROM): raggi UV

EEPROM: cancellabile elettricamente

Flash Memory: tipo di EEPROM

Architetture dei Calcolatori 2004/05

Valeria Cardellini

21

10

Problema: divario delle prestazioni

CPU-memoria

CPU

Capacità: 2x / 3 anni

Velocità: 2x / 3 anni

Prestazioni

1000

“Legge di Moore”

100

Divario di prestazione

processore-memoria:

(aumenta 50% / anno)

10

DRAM

Capacità: 4x / 3 anni

Velocità: 2x / 10 anni

1980

1981

1982

1983

1984

1985

1986

1987

1988

1989

1990

1991

1992

1993

1994

1995

1996

1997

1998

1999

2000

1

Tempo

Architetture dei Calcolatori 2004/05

Valeria Cardellini

22

Obiettivo: illusione di una memoria

grande, veloce ed economica

• Osservazioni:

– Le memorie di grandi dimensioni sono lente

– Le memorie veloci hanno dimensioni piccole

• Come creare una memoria che sia grande,

economica e veloce (per la maggior parte del

tempo)?

– Gerarchia

– Parallelismo

Architetture dei Calcolatori 2004/05

Valeria Cardellini

23

11

Gerarchia di memoria

• La memoria di un calcolatore è implementata come una

gerarchia di memoria

– Differenti tempi di accessi e di costo corrispondenti ai diversi

livelli di memoria

CPU

Aumenta il tempo di

accesso

Livello 1

Livello 2

Aumenta la capacità

di memorizzazione

.

.

.

Diminuisce il costo

per bit

Livello n

Dimensione della memoria ad ogni livello

Architetture dei Calcolatori 2004/05

Valeria Cardellini

24

Gerarchia di memoria (2)

• Obiettivi della gerarchia di memoria:

– Fornire all’utente una quantità di memoria pari a quella disponibile

nella tecnologia più economica

– Fornire una velocità di accesso pari a quella garantita dalla

tecnologia più veloce

Processor

Control

On-Chip

Cache

Registers

Datapath

Second

Level

Cache

(SRAM)

Main

Memory

(DRAM)

Speed (ns): 1

10

100

Size (bytes): 100

K

M

Architetture dei Calcolatori 2004/05

Valeria Cardellini

Secondary

Storage

(Disk)

10,000,000

(10 ms)

G

Tertiary

Storage

(Tape)

10,000,000,000

(10 sec)

T

25

12

Principio di località

• Osservazione: i programmi accedono ad una porzione

relativamente piccola del loro spazio di indirizzamento

• Esistono due tipi differenti di località

• Località temporale (nel tempo): se un elemento (dato o

istruzione) è stato acceduto, tenderà ad essere

acceduto nuovamente in un tempo ravvicinato

• Località spaziale (nello spazio): se un elemento (dato o

istruzione) è stato acceduto, gli elementi i cui indirizzi

sono vicini tenderanno ad essere acceduti in un tempo

ravvicinato

Esempio

– I programmi contengono cicli: le istruzioni ed i dati saranno

acceduti ripetutamente (località temporale)

– Gli accessi agli elementi di un array presentano un’elevata

località spaziale; nell’esecuzione di un programma è altamente

probabile che la prossima istruzione sia contigua a quella in

esecuzione

Architetture dei Calcolatori 2004/05

Valeria Cardellini

26

Principio di località (2)

Probabilità di

riferimento

0

Spazio di indirizzamento

2n-1

• Località temporale:

=> Tenere gli elementi acceduti più frequentemente vicino al

processore

• Località spaziale:

=> Spostare blocchi contigui di parole al livello superiore

To Processor

Upper Level

Memory

Lower Level

Memory

Blk X

From Processor

Architetture dei Calcolatori 2004/05

Valeria Cardellini

Blk Y

27

13

Gerarchia di memoria (3)

• Basandosi sul principio di località, la memoria di un

calcolatore è implementata come una gerarchia di

memoria

• Solo il livello più alto della gerarchia di memoria è a

contatto diretto con il processore

– Costituito dalla memoria cache

• Livelli di memoria inclusivi

– Un livello superiore, più vicino al processore, contiene un

sottoinsieme di informazioni dei livelli inferiori

– Tutti i dati sono memorizzati nel livello più basso

• Migrazione dei dati fra livelli della gerarchia

– I dati vengono di volta in volta copiati solo tra livelli adiacenti

Architetture dei Calcolatori 2004/05

Valeria Cardellini

28

Migrazione dei dati

• Blocco: la minima unità di informazione che può essere

trasferita tra due livelli adiacenti

• Hit (successo): il dato richiesto dal processore è

presente in un blocco del livello superiore

• In caso contrario si ha un miss (fallimento):il livello

inferiore della gerarchia deve essere acceduto per

recuperare il blocco contenente il dato richiesto

Processore

Architetture dei Calcolatori 2004/05

Valeria Cardellini

29

14

Memoria cache

• La memoria principale (DRAM) è sempre più lenta del

processore e tende a rallentarlo

• Sono disponibili memorie più veloci (SRAM) ma solo per

dimensioni limitate

• La cache funziona alla velocità del processore, e quindi

nasconde la “lentezza” della memoria

– Scopo della cache: disaccoppiare le velocità di processore e RAM

• Contiene le ultime porzioni di memoria acceduta: se il

processore richiede l’accesso ad una di esse evita un

accesso alla memoria

• Funziona bene sfruttando il principio di località dei

riferimenti

Architetture dei Calcolatori 2004/05

Valeria Cardellini

30

Strategia di utilizzo della cache

• La prima volta che il processore richiede dei dati si

ha un cache miss

– I dati vengono caricati dalla memoria principale e vengono

copiati anche nella cache

• Le volte successive, quando il processore richiede

l’accesso ad una cella di memoria

– Se il dato è presente in un blocco contenuto nella cache, la

richiesta ha successo ed il dato viene passato direttamente

al processore

• Si verifica un cache hit

– Altrimenti la richiesta fallisce ed il blocco contenente il dato

viene anche caricato nella cache e passato al processore

• Si verifica un cache miss

• Obiettivo: aumentare quanto più possibile il tasso di

cache hit

Architetture dei Calcolatori 2004/05

Valeria Cardellini

31

15

Hit rate e tempo medio di accesso

in memoria

• Hit rate: frazione degli accessi in memoria risolti nel

livello superiore della gerarchia di memoria

Hit rate = numero di hit / numero di accessi in memoria

• Miss rate: 1 – (Hit rate)

• Tempo medio di accesso in memoria (AMAT):

AMAT = c + (1-h)m

–

–

–

–

c: hit time (tempo di accesso alla cache)

h: hit rate

1-h: miss rate

m: miss penalty=access time + transfer time (tempo per

accedere al livello inferiore della gerarchia di memoria più tempo

per trasferire il blocco dal livello inferiore della gerarchia)

– Hit time << miss penalty

Architetture dei Calcolatori 2004/05

Valeria Cardellini

32

Come è gestita la gerarchia di memoria?

• Registri ↔ Memoria principale

– Dal compilatore (programmatore?)

• Cache ↔ Memoria

– Dall’hardware

• Memoria ↔ Dischi

– Dall’hardware e dal sistema operativo (memoria

virtuale)

– Dal programmatore (file)

Architetture dei Calcolatori 2004/05

Valeria Cardellini

33

16

Come aumentare la larghezza di

banda della memoria

• Diverse organizzazioni del sistema di memoria

CPU

CPU

CPU

Multiplexor

Cache

Cache

Cache

Bus

Bus

Bus

Memory

b. Wide memory organization

Memory

Memory

bank 0

Memory

bank 1

Memory

bank 2

Memory

bank 3

c. Interleaved memory organization

• Interleaved:

• Semplice:

a. One-word-wide

memory organization

CPU, Cache, Bus, Memoria

con stessa larghezza

(es. 32 bit)

• Wide:

CPU, Cache, Bus 1 parola;

Memoria a N banchi (es. N=4)

CPU/Mux 1 parola; Mux/Cache,

Bus, Memoria N parole

(es. Alpha: 64 bit e 256 bit)

Architetture dei Calcolatori 2004/05

Valeria Cardellini

34

Aumentare la banda: interleaving

• Accesso senza interleaving:

Tempo di accesso

CPU

Memory

Tempo di ciclo

D1 disponibile

Inizio accesso per D1

Inizia accesso per D2

Memory

Bank 0

• Accesso con interleaving a 4 vie:

CPU

Memory

Bank 1

Accesso banco 0

Memory

Bank 2

Memory

Bank 3

Accesso banco 1

Accesso banco 2

Accesso banco 3

Architetture dei Calcolatori 2004/05

Valeria Cardellini

Possiamo nuovamente accedere a banco 0

35

17