Esercitazione di Elettronica Digitale

Prof. F. Iannuzzo - A.A. 2013/2014

STADI DI INGRESSO

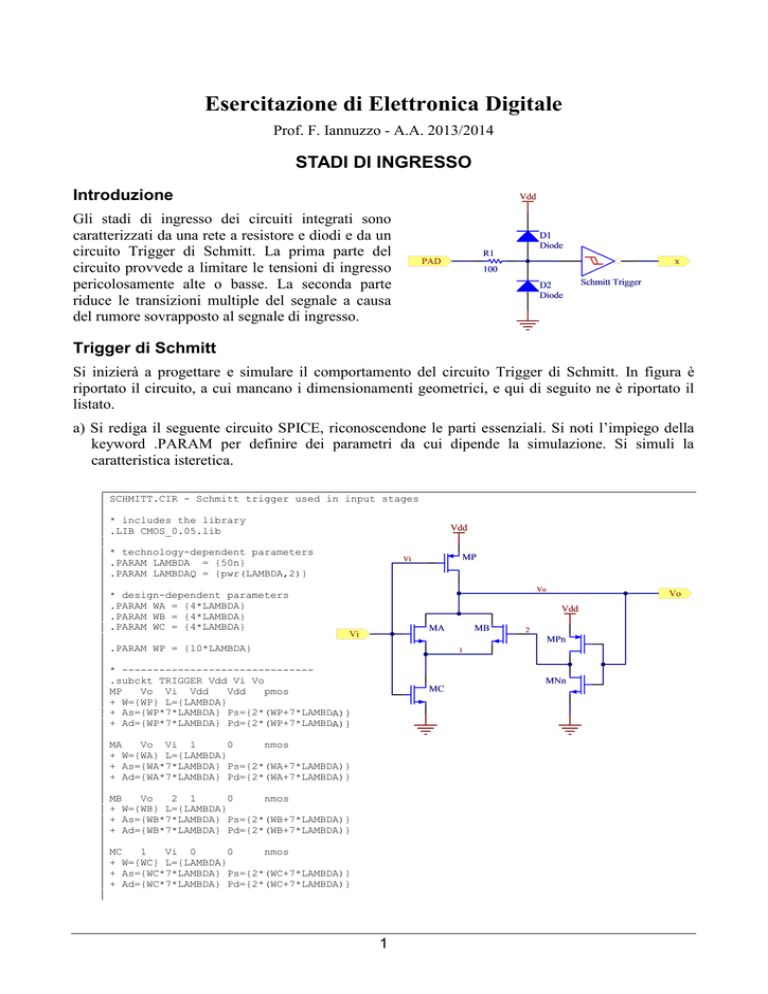

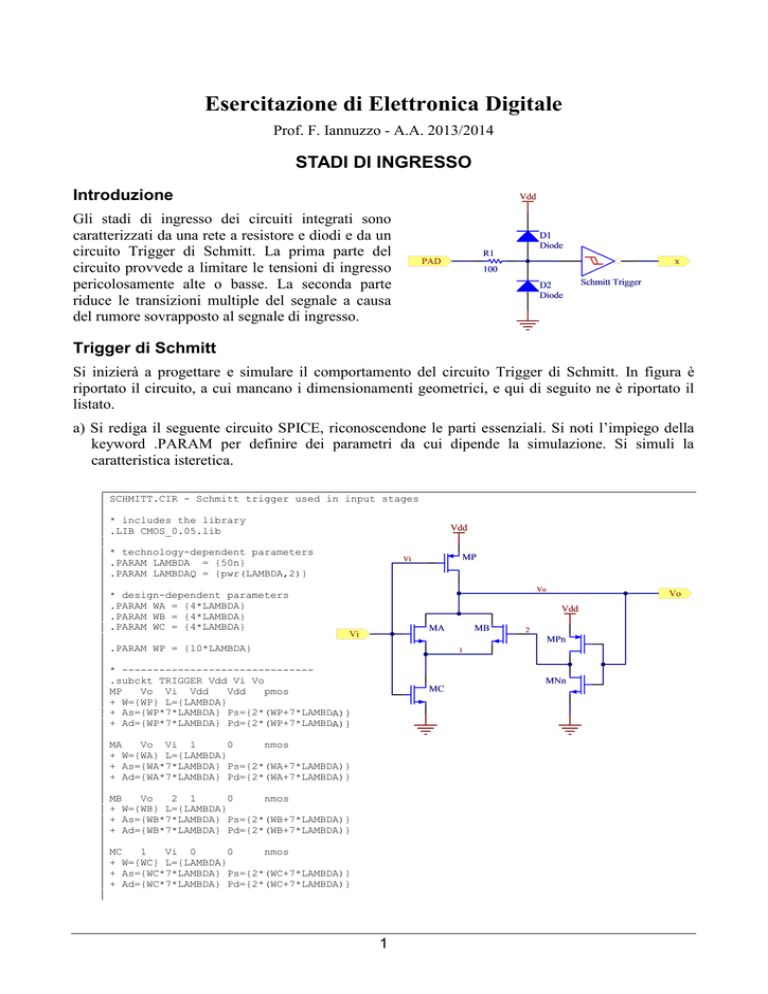

Introduzione

Gli stadi di ingresso dei circuiti integrati sono

caratterizzati da una rete a resistore e diodi e da un

circuito Trigger di Schmitt. La prima parte del

circuito provvede a limitare le tensioni di ingresso

pericolosamente alte o basse. La seconda parte

riduce le transizioni multiple del segnale a causa

del rumore sovrapposto al segnale di ingresso.

Trigger di Schmitt

Si inizierà a progettare e simulare il comportamento del circuito Trigger di Schmitt. In figura è

riportato il circuito, a cui mancano i dimensionamenti geometrici, e qui di seguito ne è riportato il

listato.

a) Si rediga il seguente circuito SPICE, riconoscendone le parti essenziali. Si noti l’impiego della

keyword .PARAM per definire dei parametri da cui dipende la simulazione. Si simuli la

caratteristica isteretica.

SCHMITT.CIR - Schmitt trigger used in input stages

* includes the library

.LIB CMOS_0.05.lib

* technology-dependent parameters

.PARAM LAMBDA = {50n}

.PARAM LAMBDAQ = {pwr(LAMBDA,2)}

* design-dependent parameters

.PARAM WA = {4*LAMBDA}

.PARAM WB = {4*LAMBDA}

.PARAM WC = {4*LAMBDA}

.PARAM WP = {10*LAMBDA}

* ------------------------------.subckt TRIGGER Vdd Vi Vo

MP

Vo Vi Vdd

Vdd

pmos

+ W={WP} L={LAMBDA}

+ As={WP*7*LAMBDA} Ps={2*(WP+7*LAMBDA)}

+ Ad={WP*7*LAMBDA} Pd={2*(WP+7*LAMBDA)}

MA

Vo Vi 1

0

nmos

+ W={WA} L={LAMBDA}

+ As={WA*7*LAMBDA} Ps={2*(WA+7*LAMBDA)}

+ Ad={WA*7*LAMBDA} Pd={2*(WA+7*LAMBDA)}

MB

Vo

2 1

0

nmos

+ W={WB} L={LAMBDA}

+ As={WB*7*LAMBDA} Ps={2*(WB+7*LAMBDA)}

+ Ad={WB*7*LAMBDA} Pd={2*(WB+7*LAMBDA)}

MC

1

Vi 0

0

nmos

+ W={WC} L={LAMBDA}

+ As={WC*7*LAMBDA} Ps={2*(WC+7*LAMBDA)}

+ Ad={WC*7*LAMBDA} Pd={2*(WC+7*LAMBDA)}

1

* auxiliary inverter

MPn

2 Vo Vdd

Vdd pmos

+ W={10 * LAMBDA} L={LAMBDA}

+ As={10*7*LAMBDAQ} Ps={(10+7)*2*LAMBDA}

+ Ad={10*7*LAMBDAQ} Pd={(10+7)*2*LAMBDA}

MNn

2 Vo 0

0

nmos

+ W={4 * LAMBDA} L={LAMBDA}

+ As={6*7*LAMBDAQ} Ps={(6+7)*2*LAMBDA}

+ Ad={6*7*LAMBDAQ} Pd={(6+7)*2*LAMBDA}

; Due to contact, source area is minimum 6 x 7

; Due to contact, drain area is minimum 6 x 7

.ends

* ------------------------------* Main circuit

Xtrig 10 1 2 TRIGGER

Vdd 10

0

; 10 is Vdd, 1 is Vi and 2 is Vo

0.7V

* emulates a DC analysis

Vi

1 0 PWL 0s,0V 10ns, 0.7V, 20ns, 0V

.TRAN 0 20ns 0 1ps

.PROBE

.END

Per visualizzare la caratteristica di ingresso-uscita, si cambi la variabile X in V(1), e si

visualizzi V(2).

b) Si noterà come la caratteristica di isteresi non è simmetrica rispetto a Vdd/2. Si studi una

possibile combinazione delle larghezze di canale di MA, MB e MC al fine di simmetrizzare al

meglio la caratteristica [Suggerimento: cosa accade se si rende W(MC) sufficientemente grande?]

2

c) si implementi in Micro il layout del circuito, utilizzando la figura qui in alto come riferimento,

ma impiegando le dimensioni calcolate di MA, MB e MC. Si verifichi il comportamento applicando

un segnale periodico all’ingresso.

d) si esporti la netlist e si risimuli il circuito in SPICE, al fine di verificare la corrispondenza con le

aspettative progettuali.

e) E’ opportuno eseguire anche una verifica dinamica sull’immunità al disturbo. Per il segnale di

ingresso, si impieghi la seguente rete:

...

Vi1

Vi2

...

1a 0

1 1a

PWL 0s,0V 10ns, 0.7V, 20ns, 0V ; parte a rampa

SIN 0V 50mV 1GHz

Completamento dello stadio di ingresso

e) si completi la simulazione SPICE dello stadio di ingresso, impiegando per i diodi il seguente

modello:

...

.MODEL DCLAMP D(IS = 1e-16)

...

che viene impiegato come segue:

...

* diodes and resistor

R

PAD

1

100 ; Ohm

D1

1 10

DCLAMP

D2

0

1

DCLAMP

...

e per l’impulso esterno un segnale di alta tensione:

...

* High voltage external signal

Vi

PAD

0 PULSE -2V 3V 1ns 1ns 1ns 10ns 20ns

...

f) si integri il layout del trigger di Schmitt aggiungendo i due diodi e il resistore, nonché un

piccolo (!) pad metallico di 10m x 10m.

3