Capitolo IX

Convertitori di dati

9.1 Introduzione

I convertitori di dati sono circuiti analogici integrati di grande importanza.

L’elaborazione digitale dei segnali è alternativa a quella analogica e presenta diversi vantaggi

rispetto a questa. E’ più economica, è più accurata, usa circuiti integrati digitali più semplici di

quelli analogici. Inoltre i risultati possono essere presentati in un aveste migliore come, ad esempio,

la misura di una tensione con display numerico. Infine subiscono una minore influenza da parte del

rumore (ad esempio nelle comunicazioni si trasmette una sequenza di impulsi binari).

In questo capitolo si esamineranno i circuiti di interfaccia fra i domini analogico e digitale.

Campionamento

Il principio alla base dell’elaborazione digitale dei segnali è quello del campionamento di un

segnale analogico. La figura 9.1 illustra in una forma concettuale il processo con cui si ottengono

campioni di un segnale analogico.

L’interruttore (switch) si chiude periodicamente sotto il controllo di un segnale impulsivo

periodico (clock). Il tempo di chiusura dello switch, τ, è relativamente breve ed i campioni ottenuti

sono registrati (held) sul condensatore. Il circuito di Fig. 9.1 è noto come circuito sample-and-hold

(S/H). Tra gli intervalli di campionamento, cioè durante gli intervalli hold, il livello della tensione

del condensatore rappresenta i campioni del segnale. Ciascuno di questi livelli di tensione entra poi

nel convertitore A/D, che fornisce un numero binario ad N bit proporzionale al valore del campione

del segnale.

274

Figura 9.1 Processo di campionamento di un segnale analogico. (a) circuito “sample-and-hold”; (b) forma d’onda

d’ingresso; (c) segnale campionamento; (d) segnale d’uscita

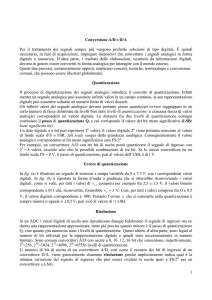

Convertitori A/D e D/A come blocchi funzionali

La figura 9.2 mostra la rappresentazione per blocchi funzionali di convertitori A/D e D/A.

Figura 9.2 Convertitori A/D e D/A come blocchi circuitali

275

Il convertitore A/D (detto anche ADC) accetta un campione analogico vA e produce una

parola digitale di N bit. di trasferimento Di contro, il convertitore D/A (detto anche DAC) accetta

una parola digitale di n bit e produce un campione analogico. I campioni d’uscita del convertitore

D/A sono spesso portati all’ingresso di un circuito sample-and-hold. All’uscita del circuito S/H si

ottiene una forma d’onda a gradino come quella mostrata in figura 9.3.

Figura 9.3 Forma d’onda a gradino all’uscita di un circuito sample-and-hold

La forma d’onda a gradino può essere addolcita da un filtro passa-basso, dando origine alla

curva mostrata nella figura 9.3. In questo modo si può ricostruire un segnale analogico d’uscita.

Infine si noti che l’errore di quantizzazione di un convertitore A/D è equivalente a ±

1

del bit meno

2

significativo (bN).

9.2 Convertitori D/A

La figura 9.4 mostra un semplice circuito per un convertitore D/A a N bit con rete resistiva

pesata. Il circuito presenta una tensione di riferimento Vref, N resistori pesati in modo binario R, 2R,

4R, 8R,….., 2N-1R, N commutatori S1, S2, …….., SN ed un amplificatore operazionale con una

resistenza di retroazione Rf = R/2. I commutatori sono controllati da una parola digitale D in

ingresso a N bit,

D=

b1 b2

bN

+ 2 +!+ N

1

2 2

2

(9.1)

dove b1, b2 … possono essere 1 o 0.

276

Si noti che bN è il bit meno significativo (LSB) e b1 è il bit più significativo (MSB). Nel

circuito in Fig. 9.4 b1 controlla lo switch S1, b2 controlla S2 e così via. Quando bi = 0, lo switch Si è

nella posizione 1 e quando bi = 1 lo switch è nella posizione 2.

Figura 9.4 Convertitore D/A a N-bit che usa una rete resistiva opportunamente pesata

Poiché la posizione 1 di tutti gli switch è la terra e la posizione 2 è la massa virtuale, la

corrente attraverso ciascun resistore rimane costante al variare della posizione dello switch.

Ciascuno switch controlla semplicemente dove va la corrispondente corrente: a massa (se il bit

corrispondente è 0) oppure alla massa virtuale (se il bit corrispondente è 1). Le correnti che

fluiscono nella massa virtuale si sommano e la corrente somma fluisce attraverso la resistenza di

retroazione Rf. La corrente totale è quindi data da

iO =

Vref

V

V

2V b b

b

b1 + ref b 2 + ! N −ref1 b N = ref 11 + 22 + ! + NN

R

2R

R 2 2

2 R

2

(9.2)

Quindi

iO =

2Vref

D , e la tensione d’uscita è data da

R

vO = −i O R f = − Vref D

(9.3)

(9.4)

che è direttamente proporzionale alla parola D, come desiderato.

Si può notare che l’accuratezza di un convertitore D/A dipende criticamente dalla:

1) accuratezza di Vref

2) precisione dei resistori pesati in modo binario

277

3) perfezione degli switch.

Lo svantaggio della rete realizzata con resistori pesati in modo binario è che, per un numero

elevato di bit, la differenza tra i valori delle resistenze più piccole e più grandi diventa notevole, il

che rappresenta un problema nel processo di fabbricazione dei circuiti integrati. Ciò comporta anche

una certa difficoltà nel mantenere la desiderata accuratezza nel valore dei resistori. Un notevole

miglioramento si può ottenere implementando la rete illustrata di seguito.

Rete R-2R

La figura 9.5 mostra lo schema fondamentale di un convertitore D/A che utilizza una rete R2R.

Figura 9.5 Configurazione di un convertitore D/A che usa una rete R-2R

La resistenza vista ad ogni nodo, verso destra, è 2R. Per dimostrare ciò è sufficiente partire

dall’ultimo blocco di resistenze (vedi figura 9.6).

Figura 9.6 Resistenza equivalente vista verso destra da ciascun nodo della rete in figura 9.5

La resistenza vista da A verso destra è R + 2R//2R = 2R. Questo risultato può essere fatto propagare

verso sinistra. Perciò la corrente che fluisce verso destra è uguale a quella verso il basso. Quindi la

278

corrente che arriva al nodo è il doppio della corrente che parte dal nodo verso il basso. Infatti

risulta: I1 = 2I 2 e, ancora 2I 3 = I 2 =

I1

e cioè I1 = 4I 3 e così via.

2

Pertanto si ha: I1 = 2I 2 = 4I3 = ! = 2 N −1 I N cioè le correnti sono pesate in modo binario, perciò:

iO =

Vref

D.

R

Nei casi pratici le correnti I1, I2, ….. sono generate da BJT.

9.3 Convertitori A/D

Ci sono varie tecniche di conversione A/D che differiscono per complessità circuitale e

velocità.

Convertitore a retroazione

La figura 9.7 mostra un semplice convertitore A/D che usa un comparatore, un contatore “updown” ed un convertitore D/A.

Figura 9.7 Convertitore A/D a retroazione

Il circuito comparatore fornisce un’uscita che può assumere uno di due distinti valori: positivo

quando il segnale differenza in ingresso è positivo, negativo quando tale segnale differenza è

negativo. Se il contatore è azzerato, l’uscita vO del DAC è nulla e l’uscita del comparatore sarà a

livello alto e, perciò, il contatore può contare gli impulsi di clock in modo crescente (up).

Aumentando il conteggio, l’uscita del DAC aumenta ed il processo continua finché vO = vA dove il

comparatore commuta ed il contatore interrompe il conteggio. A questo punto l’uscita del contatore

è l’equivalente digitale del segnale analogico in ingresso.

279

Il convertitore è lento ma segue le variazioni del segnale in ingresso con molta rapidità.

Convertitore a doppia pendenza

Uno schema di convertitore A/D ad elevata risoluzione (12-14 bit) ma a bassa velocità è

mostrato in figura 9.8.

Figura 9.8 Metodo di conversione A/D a doppia pendenza

Si ipotizzi che il segnale d’ingresso vA sia negativo. Prima dell’inizio del ciclo di conversione,

si chiude S2 in modo da far scaricare C e porre v1 = 0. Il ciclo di conversione inizia chiudendo S1 su

280

vA ed aprendo S2. In questo modo si ha una corrente I =

aumenta con pendenza

vA

uscente dall’integratore. Quindi v1

R

I vA 1

=

. Contemporaneamente il contatore comincia a contare gli impulsi

C RC

da un clock a prefissata frequenza. Questa fase del processo di conversione dura un prefissato

intervallo di tempo T1. Al tempo T1 il contatore ha contato nref impulsi. (ad esempio, per N bit si ha

nref = 2N). Si può scrivere

Vpeak

T1

=

vA

RC

(9.5)

con Vpeak tensione di picco all’uscita dell’integratore. Alla fine di questa fase, il contatore è

riportato a 0. All’istante t = T1, si collega S1 a Vref > 0. La corrente nell’integratore inverte il segno

ed è uguale a Vref/R. Quindi v1 decresce con pendenza Vref/RC. Contemporaneamente il contatore è

abilitato e conta gli impulsi dal clock a frequenza fissa. Quando v1 raggiunge lo zero, il comparatore

segnala alla logica di controllo di bloccare il contatore. Indicando con T2 la durata della seconda

fase della conversione, si ha

Vpeak

T2

=

Vref

RC

(9.6).

Le equazioni (9.5) e (9.6) possono essere combinate per dare

v

T2 = T1 A

Vref

(9.7).

Poiché nref è proporzionale a T1 e n, che è conteggio alla fine di T2, è proporzionale a T2, si ha

n = n ref

vA

Vref

(9.8).

T

1

Si ricorda che v1 = −

1 1

1

v A dt = −

( − v A )t =T1 ⋅ T1

∫

RC 0

RC

281

Quindi il contenuto del contatore, n, alla fine del processo di conversione è l’equivalente digitale di

vA.

Il convertitore a doppia pendenza mostra un’elevata accuratezza poiché le sue prestazioni

sono indipendenti dal valore preciso di R e C. Ci sono molte realizzazioni del metodo a doppia

pendenza, alcune delle quali fanno uso di tecnologia CMOS.

Convertitore parallelo o flash

Lo schema di conversione A/D più veloce è quello del convertitore flash, illustrato in figura

9.9.

Figura 9.9 Conversione A/D flash

Concettualmente la conversione flash è molto semplice. Essa utilizza 2N-1 comparatori per

confrontare il livello del segnale in ingresso con ciascuno dei 2N-1 possibili livelli di

quantizzazione. Ad esempio, nel caso di codifica a quattro bit, si possono rappresentare 16 diversi

valori (livelli di quantizzazione) mediante altrettante configurazioni da 0000 a 1111, a cui

corrispondono nel sistema decimale, i valori da 0 a 15, cioè da 0 a 2N-1. Le uscite dei comparatori

sono codificate da un circuito logico per fornire una parola a N bit. Una conversione completa può

essere ottenuta in un ciclo di clock.

La velocità dei circuito viene pagata con un’elevata complessità circuitale.

282