Sistemi Embedded

per il Mobile Multimedia

Tecnologie FPGA

Fabrizio Fazzino

Catania, 11/06/2007

Tecnologie FPGA

FPGA = “Field Programmable

Gate Array”

si potrebbe tradurre “matrice di porte

logiche programmabile sul campo”.

Si tratta di dispositivi digitali programmabili

dall'utilizzatore “sul campo”, ovvero “fuori

dalla fabbrica”.

Progettazione di un circuito

Un circuito elettronico digitale può essere

progettato in varie maniere, ad esempio

utilizzando un linguaggio di descrizione

dell'hardware (come VHDL, Verilog o

SystemC) oppure direttamente tramite un

programma di schematic entry con il

quale il progettista unisce direttamente tra

loro i componenti discreti utilizzando un

apposito programma di CAD.

Implementazione di un circuito

Ovviamente uno dei passi successivi alla

progettazione di un circuito riguarda la sua

implementazione fisica.

Questo solitamente è un passo che richiede

investimenti ingenti in quanto bisogna

ricorrere ad una apposita fabbrica (detta

fab o foundry) che implementi il circuito

su un chip di silicio.

Implementazione Standard Cell

L'implementazione fatta in una wafer fab da

un produttore di semiconduttori viene detta

Standard Cell o ASIC.

Standard cell si riferisce al fatto che quando

il designer si trova ad effettuare la sintesi

logica del circuito che ha progettato deve

utilizzare la libreria di componenti

standard che gli è stata fornita da chi

dovrà implementare il design. Questa

libreria contiene la descrizione di tutte le

porte logiche (AND, OR...) che il design su

silicio potrà utilizzare.

Tecnologie Standard Cell

Anche a parità di produttore esistono

librerie differenti in base alla tecnologia da

usare e alle caratteristiche richieste dal

design (bassi consumi, alte prestazioni

o un giusto compromesso tra le due).

Ad esempio ST nel corso degli anni ha fatto

riferimento alle tecnologie da 0.50, 0.35,

0.25, 0.18, 0.13um e 90nm come HCMOS 5,

6, 7, 8, 9 e 10, con le varianti relative ai

consumi e alla velocità.

Tecnologie ASIC

Il termine ASIC si riferisce invece al campo

di applicazione del prodotto:

ASIC = Application Specific Integrated

Circuit

Ci sono aziende che si occupano solo della

progettazione dei circuiti digitali (aziende

fabless), aziende che si occupano solo

dell'implementazione fisica (i principali sono

TSMC e UMC) ed aziende che si occupano

di entrambi gli aspetti (Intel, AMD, Texas

Instruments, STMicroelectronics).

Svantaggi degli ASIC

Le tecnologie Standard Cell permettono di

implementare un ASIC con un costo per

chip bassissimo, sull'ordine di grandezza del

dollaro.

Però hanno alcuni grossi svantaggi:

●il ciclo di progettazione e produzione è

abbastanza lungo;

●se si trova un bug dopo avere prodotto un

chip non è possibile correggerlo;

●ci sono dei costi iniziali (NRE) che per

tecnologie da 90nm possono raggiungere

un milione di dollari (1,000,000 US$).

Alternative FPGA

A causa degli svantaggi indicati prima, in

alcuni casi per l'implementazione ci si può

rivolgere alle tecnologie FPGA, che infatti:

hanno un ciclo di progettazione molto

veloce;

●utilizzano un approccio riprogrammabile e

quindi permettono la correzione di

eventuali bug;

●hanno un costo iniziale pressoché nullo.

●

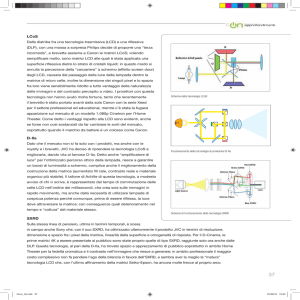

Principio di funzionamento

Un dispositivo FPGA è un chip che contiene

un array di blocchi logici configurabili e dei

canali di routing.

Ogni singolo blocco logico contiene una

Lookup Table (LUT) a 4 ingressi ed un

Flip-Flop: l'unica uscita può quindi essere

l'uscita registrata o non registrata della

LUT:

Routing negli FPGA

Quindi tutto quello che manca per

realizzare un qualunque circuito digitale è

semplicemente l'interconnessione tra tutti

questi blocchi logici disponibili sul

dispositivo: questa interconnessione può

essere codificata sotto forma di una

sequenza di bit (bitstream) che viene

introdotta serialmente dopo il reset e va a

programmare gli switch presenti nel

dispositivo.

Switch negli FPGA

Infatti i 4 ingressi della LUT di ogni blocco

logico sono disposti sui 4 lati del blocco, ed i

segnali che uniscono tra loro i vari blocchi

confluiscono in alcuni switch la cui tabella

di routing statico può essere programmata

in binario:

Principali produttori di FPGA

I principali player del fiorente mercato degli

FPGA sono Xilinx e Altera, ma ci sono

molti altri produttori che realizzano

dispositivi specializzati in alcuni campi

specifici.

Famiglie di FPGA

Ogni produttore è in grado di offrire diverse

famiglie di prodotti con caratteristiche

completamente diverse sia dal punto di

vista delle prestazioni che dei costi.

Attualmente le famiglie di punta dei due

principali produttori sono Virtex-5 di Xilinx

e Stratix-III di Altera.

Invece le famiglie più economiche sono

Spartan-3 di Xilinx e Cyclone-III di Altera.

Principali utilizzi degli FPGA

Famiglie di prodotti differenti vengono

utilizzati per applicazioni diverse.

I prodotti di punta possono avere un costo

intorno ai 1000$ per pezzo, quindi vengono

utilizzati quasi esclusivamente per

realizzare prototipi di chip che poi

verranno implementati in serie come ASIC.

I dispositivi economici (50$-100$) possono

invece essere utilizzati anche per prodotti

riprogrammabili rivolti al mercato.

Limitazioni degli FPGA

A causa della tecnologia utilizzata i

dispositivi FPGA dispongono di alcuni

svantaggi rispetto alla controparte ASIC:

occupano più area (visto che la logica

presente non è ottimizzata per la

particolare applicazione) e dissipano più

potenza (circa 10 volte tanto), quindi non

possono essere utilizzati in dispositivi mobili

alimentati a batteria; inoltre anche le

frequenze di funzionamento sono

molto più basse (circa 10 volte, es. 50

Mhz contro 500 MHz).

Differenza tra classi di prodotti

La principale differenza tra i dispositivi

FPGA di fascia bassa e quelli di fascia alta è

data dalla quantità di blocchi logici

configurabili presenti sul dispositivo.

Ad esempio riguardo ai dispositivi Xilinx:

●i dispositivi della serie Spartan-3E

dispongono di un numero di LUT che va

da 2K a 30K;

●invece i dispositivi della serie Virtex-5

dispongono di un numero di LUT che va

da 20K a 200K.

Software EDA

In compenso il software utilizzato per il ciclo

di progettazione degli FPGA è molto più

economico della controparte ASIC (1000$

contro i 100'000$ per una licenza

Synopsys).

Esistono addirittura due tool gratuiti forniti

direttamente dai produttori di dispositivi:

●Xilinx ISE WebPack (per Linux e

Windows);

●Altera Quartus (solo per Windows).

ASIC vs. FPGA

In definitiva la progettazione ASIC e quella

FPGA coprono esigenze molto diverse:

ASIC ha costi iniziali molto elevati, sia per

le licenze che per le maschere (NRE) e

tempi di sviluppo molto lunghi; in compenso

ogni chip avrà costi di produzione e

consumi molto bassi;

FPGA ha costi iniziali quasi nulli e tempi di

progettazione ridotti, ma ogni singolo

dispositivo può costare centinaia di dollari e

dissipare molta potenza.

Development Board

Verrà adesso mostrato un esempio di

progettazione digitale utilizzando la

tecnologia FPGA.

Poiché non è pensabile iniziare costruendo

tutta una scheda su circuito stampato

(PCB, Printed Circuit Board) si inizierà

selezionando una delle tante schede

presenti in commercio che integrano già un

chip FPGA: tali schede si chiamano

Development Board.

Spartan Starter Kit

La development board più diffusa è il

cosiddetto Spartan 3E-500 Starter Kit da

149$, che integra un FPGA da 10K LUT.

Questo dispositivo non è in grado di

implementare microprocessori molto

complessi ma può contenere un

microcontrollore ed alcune periferiche.

La scheda dispone inoltre di vari tipi di

memorie ed alcune interfacce.

Aspetto della board

Memorie presenti sulla board

Intel StrataFlash 128 Mbit (memoria

Flash con interfaccia byte-wide da 16

MByte)

●STMicroelectronics SPI Flash 16 Mbit

(memoria Flash con interfaccia seriale da 2

MByte)

●Micron Technology 512 Mbit DDR

SDRAM (memoria DDR a 16 bit da 64

MByte)

●

Sulla board è inoltre presente una ulteriore

memoria Flash di Xilinx ma può essere

utilizzata solo per contenere il bitstream.

Altre interfacce on-board

La board include inoltre:

un display LCD con due righe da 16

caratteri ciascuna;

●una uscita VGA;

●due porte seriali RS-232;

●una porta PS/2 per mouse o tastiera;

●una porta FastEthernet 10/100 con

incluso un chip PHY (physical layer);

●quattro pulsanti ed una manopola.

●

Esempio “Hello World”

Come esempio di utilizzo della board verrà

progettato un piccolo blocco VHDL in grado

di scrivere sul display LCD presente sulla

board la frase desiderata (ad esempio

“Hello” o “Ciao”).

Per prima cosa bisogna prendere il manuale

della board all'indirizzo

http://www.xilinx.com/bvdocs/userguides/ug230.pdf

e studiare le specifiche del display LCD.

Interfaccia del display LCD

Intanto bisogna vedere l'interfaccia tra il

dispositivo FPGA e il display LCD:

Entità VHDL

Il blocco VHDL da implementare sull'FPGA si

dovrà interfacciare con i pin di top-level del

display LCD.

In base al manuale la descrizione dell'entità

sarà la seguente:

entity hello is

port (

clock: in std_logic; ­­ Clock di sistema

lcd_d : inout std_logic_vector(7 downto 4); ­­ 4­bit di dati in/out

lcd_rs : out std_logic; ­­ Register Select (0=config, 1=dati)

lcd_rw : out std_logic; ­­ Read/Write (1=read, 0=write)

lcd_e : out std_logic ­­ Enable (abilita tutti gli altri segnali)

);

end hello;

Protocollo di comunicazione

Come si vede l'interfaccia di comunicazione

tra l'FPGA e il display LCD dispone di un

bus dati di soli 4 bit, quando la

trasmissione del codice ASCII di ogni

carattere ne richiede il doppio.

Di conseguenza per scrivere un byte di dato

o di configurazione nella memoria del

display LCD il relativo byte va spezzato in

due nibble da scrivere separatamente,

prima il nibble alto (bit 7...4) e poi il nibble

basso (bit 3...0).

Sequenza di passi

1) all'inizio mando segnali validi tra i quali

sul bus dei dati LCD_D il nibble alto, ma con

LCD_E disabilitato

2) dopo 2 cicli attivo LCD_E portandolo a 1

3) dopo altri 12 cicli disabilito LCD_E

riportandolo a zero

4) dopo 1 altro ciclo posso rimuovere i

segnali validi dai bus (opzionale)

5) aspetto 50 cicli

6) ripeto i passi 1-4 per il nibble basso

7) aspetto 2'000 cicli

8) ripeto i passi 1-7 per un altro carattere o

byte di configurazione

Comando “Clear Display”

All'accensione del dispositivo ed ogni qual

volta si voglia cancellare il display della

board è necessario inviare all'LCD un

comando “Clear Display”.

Solo in questo caso al passo 7 non bisogna

aspettare 2'000 cicli ma bensi' 82'000 per

dare il tempo al display LCD di

sovrascrivere con spazi tutti i caratteri.

Architettura VHDL

Posso ora scrivere l'architettura VHDL del

mio blocco in modo da rispettare le

temporizzazioni previste dal manuale.

Per mantenere semplice l'esempio si

utilizzerà un semplice contatore ed i vari

segnali verranno assegnati sulla base del

contatore globale.

Da notare che a parte il clock il nostro

blocco non ha ingressi, se volessimo gestire

anche i pulsanti della board la logica

sarebbe senz'altro stata più complessa.

Comando “Clear Display” in

VHDL

case counter is

­­ LCD_D=0000­0001, LCD_RS=0, LCD_RW=0, LCD_E=0­1­0

when 2000 =>

lcd_d <= "0000"; lcd_rs <= '0'; lcd_rw <= '0'; lcd_e <= '0';

when 2002 =>

lcd_d <= "0000"; lcd_rs <= '0'; lcd_rw <= '0'; lcd_e <= '1';

when 2014 =>

lcd_d <= "0000"; lcd_rs <= '0'; lcd_rw <= '0'; lcd_e <= '0';

when 2100 =>

lcd_d <= "0001"; lcd_rs <= '0'; lcd_rw <= '0'; lcd_e <= '0';

when 2102 =>

lcd_d <= "0001"; lcd_rs <= '0'; lcd_rw <= '0'; lcd_e <= '1';

when 2114 =>

lcd_d <= "0001"; lcd_rs <= '0'; lcd_rw <= '0'; lcd_e <= '0';

Comando “Write Data” in VHDL

­­ LCD_D=DDDD­DDDD, LCD_RS=1, LCD_RW=0, LCD_E=0­1­0

when 85000 =>

lcd_d <= ASCII_CMAIUSC(7 downto 4);

lcd_rs <= '1'; lcd_rw <= '0'; lcd_e <= '0';

when 85002 =>

lcd_d <= ASCII_CMAIUSC(7 downto 4);

lcd_rs <= '1'; lcd_rw <= '0'; lcd_e <= '1';

when 85014 =>

lcd_d <= ASCII_CMAIUSC(7 downto 4);

lcd_rs <= '1'; lcd_rw <= '0'; lcd_e <= '0';

when 85100 =>

lcd_d <= ASCII_CMAIUSC(3 downto 0);

lcd_rs <= '1'; lcd_rw <= '0'; lcd_e <= '0';

when 85102 =>

lcd_d <= ASCII_CMAIUSC(3 downto 0);

lcd_rs <= '1'; lcd_rw <= '0'; lcd_e <= '1';

when 85114 =>

lcd_d <= ASCII_CMAIUSC(3 downto 0);

lcd_rs <= '1'; lcd_rw <= '0'; lcd_e <= '0';

Comando “DD RAM Address”

Normalmente i caratteri vengono scritti in

sequenza: ma in ogni momento è possibile

selezionare in quale posizione andare a

scrivere specificando il corrispondente

indirizzo della Display Data RAM:

LCD_D=1AAA­AAAA

LCD_RS=0

LCD_RW=0

LCD_E=0­1­0

dove AAA-AAAA corrisponde in binario

all'indirizzo 0x40 se si vuole andare al

primo carattere della seconda riga.

File UCF

Prima di passare all'ambiente integrato di

sviluppo è necessario predisporre anche un

altro file, detto file UCF (User Constraint

File). Questo file tra le altre cose creerà il

mapping tra i nomi che noi abbiamo

assegnato ai pin di top-level del nostro

blocco ed i veri nomi dei piedini dell'FPGA.

Per fortuna poiché abbiamo acquistato una

board già pronta tutti gli altri constraint per

ogni piedino possono essere semplicemente

copiati dal manuale.

Esempio di file UCF

#

# File dei constraint dell'esempio 'hello' per lo Xilinx Spartan Starter Kit

#

# Utilizza il clock cablato di 50MHz

NET "clock" PERIOD = 20.0ns HIGH 50%;

NET "clock" LOC = "C9" | IOSTANDARD = LVTTL;

# Mapping delle porte dell'entita' ai pin effettivamente connessi all'LCD

NET "lcd_rs" LOC = "L18" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 2;

NET "lcd_rw" LOC = "L17" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 2;

NET "lcd_e" LOC = "M18" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 2;

NET "lcd_d<4>" LOC = "R15" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 2;

NET "lcd_d<5>" LOC = "R16" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 2;

NET "lcd_d<6>" LOC = "P17" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 2;

NET "lcd_d<7>" LOC = "M15" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 2;

Ambiente integrato ISE

Utilizzando solo i due file hello.vhd e

hello.ucf sarà possibile mappare il blocco

sullo Starter Kit e fare apparire la scritta sul

display.

Tutto quello che serve sono un cavo USB

(per connettere la board al proprio PC) e

l'ambiente integrato ISE di Xilinx, la cui

versione WebPack è liberamente scaricabile

dal sito www.xilinx.com (le dimensioni

attuali sono di 1.4 GByte).

ISE WebPack per Linux

L'unica differenza tra la versione Linux e

quella Windows è che nella prima

l'installazione del driver che serve alla

programmazione della board potrebbe

risultare problematico; comunque l'ex

studente Giacomo Fazio ha scritto una

esauriente guida all'installazione dei driver

Linux all'indirizzo

http://www.intilinux.com/howto/478/u

sare­le­board­xilinx­fpga­su­linux/

Creazione progetto ISE

In entrambe le versioni il progetto si crea da

File | New Project...

e assegnando un nome (es. “hello”) al

progetto; il top-level è di tipo HDL.

Selezione del dispositivo

Aggiunta dei file al progetto

Dopo avere selezionato il dispositivo in uso

sullo Spartan-3E 500 Starter Kit tra tutti i

dispositivi Xilinx disponibili (come mostrato

nella diapositiva precedente) bisogna

saltare la finestra “Create a New

Source” e passare direttamente alla

finestra di dialogo “Add Existing

Sources”, dove potremo aggiungere i

nostri due file e confermare.

Avvio del mapping

Conclusione del mapping

Dopo alcuni secondi il mapping, ovvero la

sequenza dei processi di sintesi,

implementazione e creazione del bitstream,

si concluderà con successo:

Come mostrato dal report

alla pagina successiva, il

nostro blocchetto occuperà

solo l'1% delle LUT

disponibili:

Programmazione della board

Ora non ci resta che programmare la board

utilizzando il tool offerto sempre da ISE,

chiamato iMPACT:

Catena di dispositivi JTAG

iMPACT ci presenterà la catena di dispositivi

presenti sulla board programmabili tramite

l'interfaccia JTAG:

Il dispositivo che ci interessa è xc3s500e

(codice di Spartan-3E 500), quindi

assegneremo a questo il nostro bitstream

hello.bit e poi con il tasto destro

selezioneremo “Program...”.

Se tutto va bene...

...sulla nostra board dovrebbe apparire...

Conclusioni

Questa presentazione è dunque servita a:

1) descrivere i campi di applicazione

delle tecnologie FPGA;

2) spiegare per sommi capi le modalità di

funzionamento;

3) mostrare un semplicissimo esempio

VHDL dalla specifica funzionale fino

all'esecuzione sulla board.

Possibili sviluppi

Per realizzare un programma interattivo

oltre all'output serve anche la gestione

dell'input.

Su questo argomento già nello scorso A.A.

sono state sviluppate diverse tesine,

compresi alcuni videogiochi (es. il “Gioco

delle Tre Carte”).