Margherita Napoli

17-04-2002

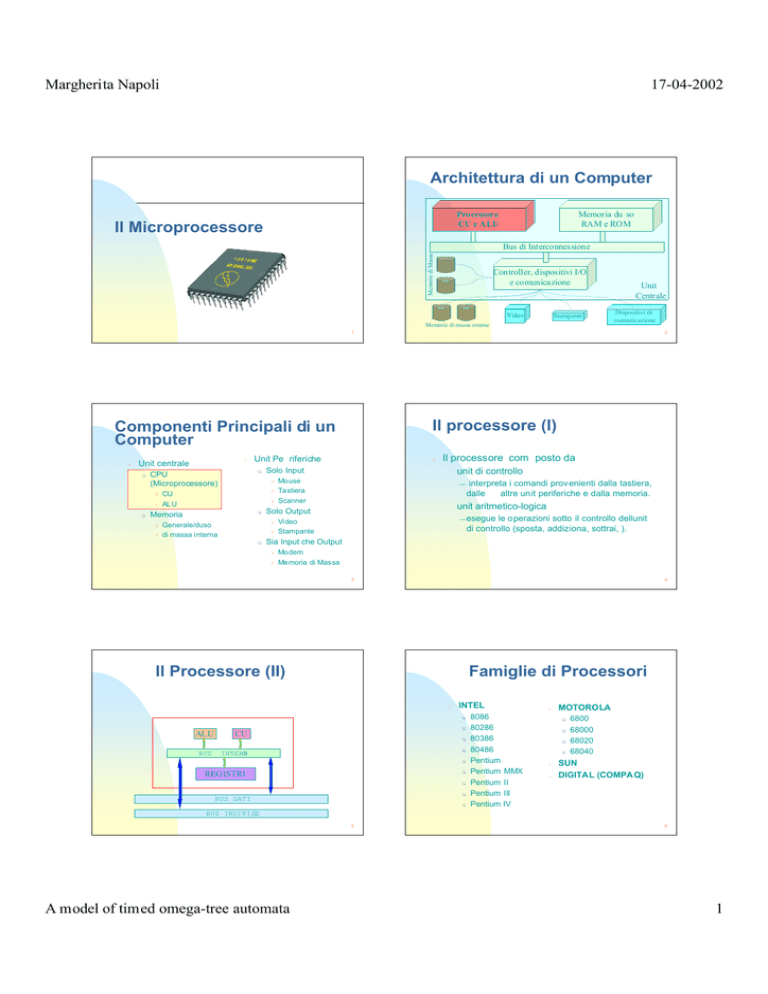

Architettura di un Computer

Processore

CU e ALU

Il Microprocessore

Memoria du so

RAM e ROM

Memorie di Massa

Bus di Interconnessione

Controller, dispositivi I/O

e comunicazione

Video

Stampante

Memorie di massa esterne

Unit

Centrale

Dispositivi di

comunicazione

1

Il processore (I)

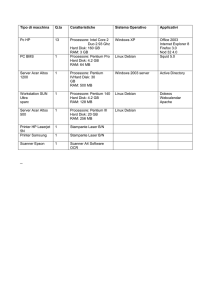

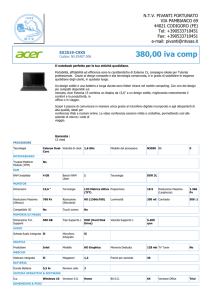

Componenti Principali di un

Computer

n

n

Unit centrale

u

CPU

(Microprocessore)

F

F

u

F

CU

ALU

F

u

F

F

u

Il processore com posto da

unit di controllo

Mouse

Tastiera

Scanner

—

interpreta i comandi prov enienti dalla tastiera,

dalle

altre unit periferiche e dalla memoria.

unit aritmetico-logica

Solo Output

F

Generale/duso

di massa interna

n

Solo Input

F

Memoria

F

Unit Pe riferiche

u

2

— esegue

le operazioni sotto il controllo dellunit

di controllo (sposta, addiziona, sottrai, ).

Video

Stampante

Sia Input che Output

F

F

Modem

Memoria di Massa

3

4

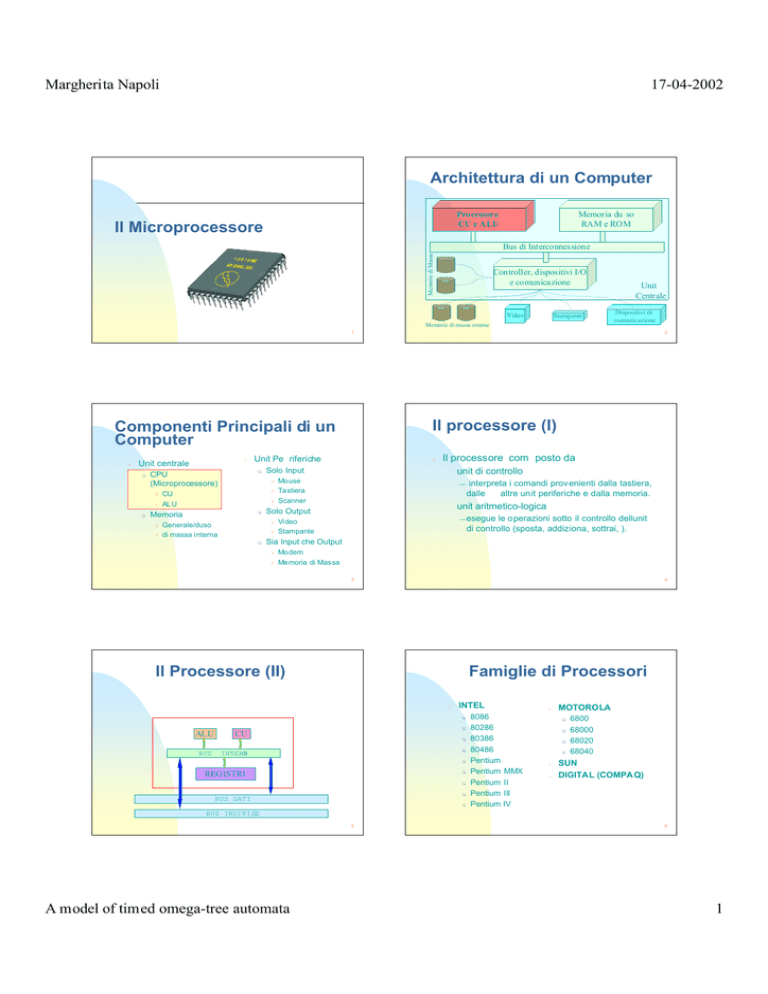

Il Processore (II)

Famiglie di Processori

n

INTEL

u

ALU

CU

BUS

INTERN

O

u

u

u

u

u

REGISTRI

u

u

BUS DATI

u

8086

80286

80386

80486

Pentium

Pentium MMX

Pentium II

Pentium III

Pentium IV

n

MOTOROLA

u

u

u

u

n

n

6800

68000

68020

68040

SUN

DIGITAL (COMPA Q)

BUS INDIRIZZ

I

5

A model of timed omega-tree automata

6

1

Margherita Napoli

17-04-2002

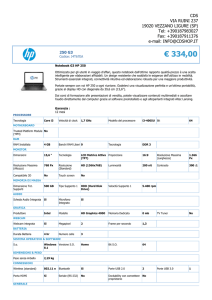

Caratteristiche di un

processore

n

Dimensione del bus

u

n

n

@

numero di fili che costituiscono il bus

Legge di JOY (previsione sullaument o di

velocit)

Velocit di elaborazione

u

n

Velocità dei processori

misurata in numero di operazioni al secondo

MIPS oppure in MHz

MIPS = 2 (anno-1984)

Numero di transistor contenuti nel chip

Set di istruzioni implementate

u

Il re ndimento dei processori andat o

molto vicino alle previsioni di Joy

CISC, RISC, CRISP, MMX

7

Transistor

F

8

Confronto: Numero di

Transistor

Piccoli interruttori che implementano le

funzioni in un microprocessore

10000000

9000000

8000000

7000000

6000000

Legge di Moore

(1965):

5000000

4000000

Il numero di

transistor in un

ngolo

si chip

raddoppia ogni anno e mezzo.

3000000

2000000

Pentium II

Pentium III

Pentium Pro

Pentium MMX

Intel406

Pentium

Intel386

8086

80286

8080

4004

0

8008

1000000

Moore stato uno d ei fondatori di INTEL

9

Evoluzione P Intel (I)

Nome

Data

Velocit

4004 1971 108KHz

10

Evoluzione P Intel (II)

Intel 386

1985

16MHz

275000

32

Intel 486

1989

25MHZ

1200000

32

Transistor

Bus

2300

4

Pentium

1993

66MHz

3100000

32

1995

200MHz

5500000

64

4500000

32

8008 1972 200KHz

3500

8

Pentium Pro

8080 1974

2MHz

6000

8

Pentium MMX

1997

200MHz

8086 1978 10MHz

29000

16

Pentium II

1997

300MHz

7000000

64

16

Pentium III

1999

450MHz

10000000

64

Merced

2000

800MHz

10000000

64

80286 1982 12MHz

134000

11

A model of timed omega-tree automata

12

2

Margherita Napoli

17-04-2002

Set di Istruzioni

La cache del processore

@

Processore

Memoria Cache I liv.

Cache

di

II liv.

Memoria Centrale

Insieme di semplici operazioni che pu

eseguire un microprocessore

F

CISC: Complex Instruction Set Chips

F

RISC: Reduced Instruction Set Chips

F

CRISC: Complex RISC

Bus di I nterconnessione

n

Memoria estremamente veloce (e costosa)

u

u

n

situata allinte rno del processore (I livello)

situate alle sterno del processore (II livello)

Vengono usate come aree di transito

13

CISC: più di 300 Istruzioni

14

RISC: meno di 200 Istruzioni

Pu eseguire istruzioni complesse, ad esempio

si possono moltiplicare due numeri.

Istruzioni eseguite da un microprogramma.

Lesecuzione di una istruzione pu prendere

vari cicli.

Soltanto

l80%

delle

istruzioni

effettivamente utilizzato.

Esegue istruzioni semplici, ad esempio, per

moltiplicare due numeri si esegue pi volte la

somma.

u

A*B = A+A+ Æ Æ

+AÆ

Istruzioni eseguite dallhardware.

Pi istruzioni eseg uite in un unico ciclo.

Pi economici dei CISC

15

Compatibilità tra P Diversi

Migliorare le prestazioni

di un P

Ogni processore usa il proprio insieme di

comandi per eseguire le operazioni richieste

Programmi scritti per un processore non

sono utilizzabili su di un altro processore

u

16

Capacit dat i

— Aumentare

Velocit di elaboraz ione

Es. un programma che funziona su un P

Pentium non funziona su un processore

Motorola 68000 (computer Apple).

— Aumentare

la velocit del clock

Efficienza

— Cambiare

Un P pu simularne degli altri.

il set di istruzioni

Area Occupata

—

17

A model of timed omega-tree automata

numero di bit da elaborare (8, 16, 32,

64 bit)

Passare da alluminio a rame

18

3

Margherita Napoli

17-04-2002

Coprocessori e P Paralleli

Coprocessore matematico

n

Processori che aumentano la

capacit di calcolo di un computer.

F

n

CPU

CO- P

Parte

Rimanente

Computer

CPU 1

CPU 2

Parte

Rimanente

Computer

Processore di supporto, predisposto per

operazioni matematiche su numeri con la

virgola.

Utilizzato soprattutto in applicazioni che

richiedono elevata capacit di calcolo:

u

u

programmi di simulazione tridimensionale

(ingegneria o architettura).

programmi per fisica, matematica, astronomia

19

20

Processori Dedicati

Grafica

Suono

Lisp Machine

Gestione videoregistratori, telecamere, TV

DSP: Digital Signal Processing

u

u

La Memoria d’Uso

Sistema frenante ABS

Sospensioni autolivellanti

21

22

La Memoria d’Uso

Processore

CU e A LU

Memoria (I)

Memoria dus o

RAM e ROM

@

@

Memorie di Massa

Bus di Interconnessione

Controller, dispositivi I/O

e comunicazione

Video

Stampante

Memorie di massa esterne

@

Unit

Centrale

Possiamo considerarla come un casellario

numerato.

Ogni casella (cella) ha un numero (indirizzo).

Possiamo accedere al contenuto della cella

tramite il suo indirizzo.

Dispositivi di

comunicazione

23

A model of timed omega-tree automata

@

Posto dove vengono immagazzinati i dati e i

programmi.

24

4

Margherita Napoli

17-04-2002

Memoria (II)

@

@

Chip di Memoria

Memoria Volatile: i dati vengono persi

una volta tolta lalimentazione al

computer.

F

RAM: Random Access Memory

Memoria ad Accesso Casuale

Volatile - Dinamica

Memoria non Volatile: anche in assenza

di alimentazione, i dati sono conservati.

F

ROM: Read Only Memory

Memoria a Sola Lettura

Non Volatile - Statica

25

RAM

26

Dimensione Memoria (I)

La dimensione della memoria legata alla

lunghezza dellindirizzo e alla dimensione del

bus.

F

Memoria dinamica, volatile

Conserva dati e programmi

Random (c asuale): a d accesso

diretto

v

v

Con 8 bit si potrebbero indirizzare solo 256

celle di memoria. Tramite uno stratagemma il

P 8080 riesce ad indirizzare 64KB.

Diretto: CD musicale

Sequenziale: cassetta musicale

27

28

Dimensione Memoria (II)

F

bus a 32 bit

Confronto di Memorie

RAM 4 GB

(232 byte = 4 *230 byte )

Dimensione

300000

256Mb

250000

F

bus a 64 bit

RAM 2 24 TB

(264 byte = 224 *240 byte )

200000

150000

100000

F

F

232 < Numero secondi in un secolo < 2 33

257 < Secondi dalla creazione del sistema solare < 258

64Mb

50000

0

64Kb 256Kb

1984

29

A model of timed omega-tree automata

1985

1Mb 4Mb

1986

1988

16Mb

1989

1992

1994

30

5

Margherita Napoli

17-04-2002

Accesso alla Memoria

Velocità di Accesso

@

Chip d

i

memor ia

F

31

Ciclo di Memoria

32

Confronto di Memorie

120

120

100

80

70

60

60

50

50

40

40

30

1998

0

1994

20

1992

F

Tempo minimo richiesto tra due accessi

consecutivi.

Il tempo di accesso misura to in nanosecondi

(ns)

1 nanosecondo = 1 miliardesimo

di

secondo

140

1989

@

Velocit(in ns)

150

160

1988

Posto dove

sono

memor izzati

i dati

1986

Gestisce

l’accesso

alla

memor ia

Sarebbe meglio distinguere il tempo di

accesso in scrittura da quello in lettura,

in genere differiscono.

1985

Controller della

memor ia

1984

Tempo di Accesso: tempo necessario

per leggere un dato da una certa

locazione di memoria.

33

Tipi di Memorie

Wait State

DRAM: Dynamic RAM

F

F

F

@

Dinamica perch ha bisogno di continui (ogni

due ms) cicli di refresh (aggiornamento dei dati

presenti in essa)

Pregi: basso costo e grandi capacit di

memoria di un singolo chip

Difetti: il controller, per ogni singolo bit, deve

indicare al chip di memoria lindirizz o della

cella.

tempo morto indotto dal ciclo di

refresh

durante questo tempo la CPU non

pu far e niente

i dati possono essere trasferiti

solo dopo ogni refresh

35

A model of timed omega-tree automata

34

36

6

Margherita Napoli

17-04-2002

SRAM

Cronologia

Static RAM:

—

—

—

—

Non necessita di cicli di refresh

Molto costosa

Molto veloce

Utilizzata come memoria cache

DRAM

Primi PC

FPM DRAM

Tarda era 486

EDO DRAM

Pentium

SDRAM

Pentium MMX

SRAM

Memoria Cache

37

38

Moduli di Memoria

@

Circuiti che contengono chip di memoria

F

SIMM: Single In-line Memory Module

F

consentivano di trasferire 8 bit alla volta

F

90 intr odotte SIMM per dati a 32 bit

Capacità del Chip

1976: 16.000 bit

Oggi: oltre un miliardo di bit

10 copie dellop era omnia di

Shakespeare

4 ore di musica (qualit d i un CD)

15 minuti di immagini video

DIMM: Double In-line Memory Module

F

F

Pi chip for mano un modulo di

memoria

consente di trasferire 64 bit alla volta

39

40

Memoria Virtuale (II)

La Memoria Virtuale (I)

s

I programmi possono eccedere la capacit

della memoria disponibile.

Rende i programmi ed i dati indipendenti

dalla effettiva dimensione della memoria

Utilizzato da molti dei sistemi operativi

attuali.

@ di ogni pr ogramma (o dati) sono presenti in

memoria centrale solamente quelli in uso

I dati non usati sono messi sullhard disk

Non esiste fisicamente ma solo logicamente

—

41

A model of timed omega-tree automata

Nel 1997: 1MB di HD

160 lire

1MB di RAM 16.000 lire

42

7

Margherita Napoli

17-04-2002

Memoria Virtuale (III)

Memoria Cache

I dati in

ccesso

e

vengo no spostati

tempo raneamente

sull’h

ard disk

@

Memoria ad accesso veloce interposta tra

processore e RAM. Contiene istruzione e dati

di immediato o prossimo utilizzo.

Il cerca prima nella cache poi nella RAM

Nella cache ci sono sia il dato che

informazioni sul suo indirizzo.

All’occo

rrenza

dati ven

gono

trasfer

iti

nuo vamente

nella RAM

i

43

Buffer

@

Esistono cache di primo e secondo livello.

44

ROM

Memoria RAM cuscinetto o tampone

dove vengono messi temporaneamente i

dati durante il trasferimento da/verso

periferiche

Conservano i dati immessi da tastiera

prima che vengano accettati dalla CPU.

Conservano i dati associati ad operazioni

di taglia/copia e incolla (clipboard)

Memoria statica, non volatile

Contenuto inalterabile predisposto in fase di

produzione

Contiene istruzioni eseguite allaccensione

del computer (software di diagnostica)

Sistema Operativo e/o Programmi

applicativi

La ROM pi vel oce della RAM

Non espandibil e come la RAM

45

Tipi di Memoria ROM

46

Gerarchia di Memorie

Costo

Velocit

PROM: Programmable ROM

—

Tipo di ROM che si pu programmare una sola

volta con apparecchiature speciali e costose.

EPROM: Erasable PROM

—

Dimensione

Memoria Cache

Volatile

Memoria ROM programmabile e cancellabile

EEPROM: Elettrically Erasable PROM

Memoria Centrale

Riprogrammabile tramite impulsi elettrici senza

doverla rimuovere.

Conservano i dati relativi alla configurazione di

un sistema (usate anche in televisori, radio,

videoregistratori per conservare la sintonia).

Memoria di Massa (dischi)

Non Volatile

47

A model of timed omega-tree automata

Volatile

48

8

Margherita Napoli

17-04-2002

Interazione tra CPU e

RAM

Schema di Interazione

Interagiscono nellesecuzione di

programmi e nellelaborazione di dat i

Interagiscono in un processo di quattro

fasi

F

F

F

F

caricamento

decodifica

esecuzione

memorizzazione

CU

Deco difica

ALU

Esecuzione

Memor izzazion

e

Caricamento

49

Fasi 1 e 2

50

Fasi 3 e 4

Caricamento: La CU preleva listruzione

successiva presente in memoria e la

immagazzina al suo interno in un registro.

Decodifica

: La CU interpreta listruzione e

trasferisce i dati a cui questa fa riferimento dalla

RAM alla ALU.

51

Esecuzione: La

ALU

esegue

loperazione logica o ar itmetica richiesta.

Memorizzazione: I risultati delle

operazioni svolte sono immagazzinati

nella RAM oppure in un registro della

ALU detto accumulatore.

52

Tempi dell’Interazione

Tempo di istruzione:tempo necessario

per portare a termine le fasi 1 e 2

Tempo di esecuzione: tempo necessario

per portare a termine le fasi 3 e 4

53

A model of timed omega-tree automata

9