La Comunicazione NR&N

Roberto Marani

Anna Gina Perri

Dipartimento di Ingegneria Elettrica

e dell’Informazione, Laboratorio di

Dispositivi Elettronici, Politecnico di

Bari

Memorie ferroelettriche e magnetiche:

stato dell’arte e sviluppi futuri

Ferroelettric and magnetic memories: status and future

challenges

Sommario

In questo articolo vengono esaminate le memorie di ultimissima generazione: le Memorie Ferroelettriche (FeRAM), basate sull’effetto fotoelettrico, e le Memorie Magnetiche (MRAM), basate sull’effetto tunnel magnetico. Entrambi questi tipi di memorie forniscono performance superiori rispetto alle attuali FlashRAM e promettono di superare

i limiti strutturali a cui le Flash stanno attualmente andando in contro.

Abstract

In this paper we present the status and future challenges of ferroelectric and magnetic memories, which are the promise for dramatic improvements in the speed, endurance and power consumption of non-volatile semiconductor memories.

1. Introduzione

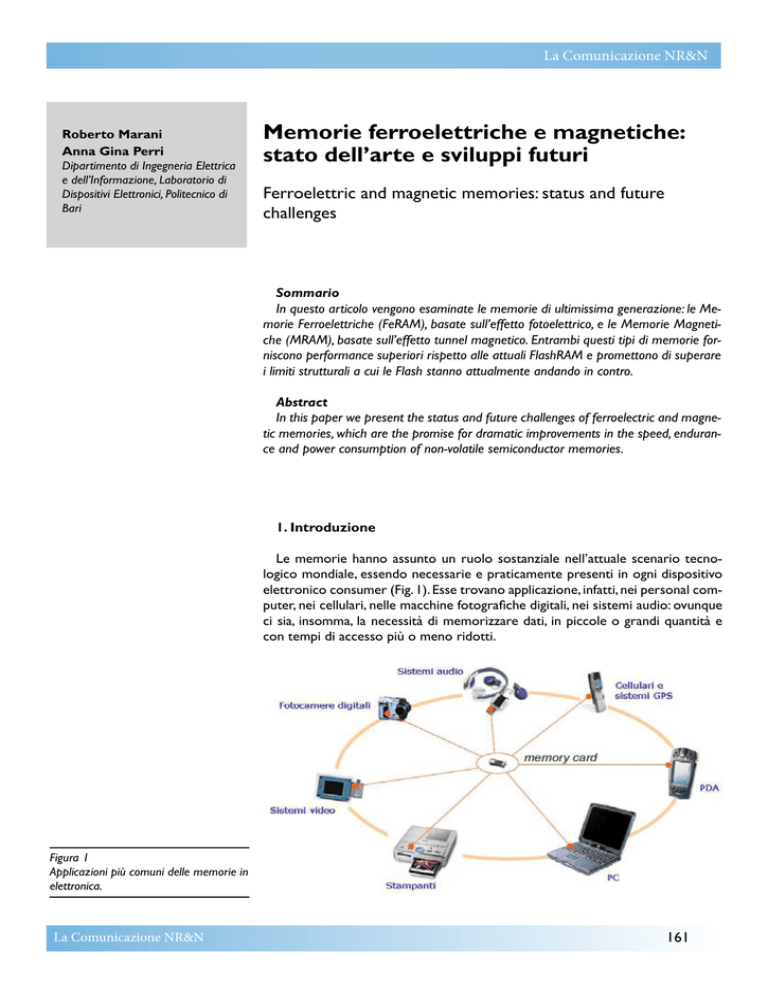

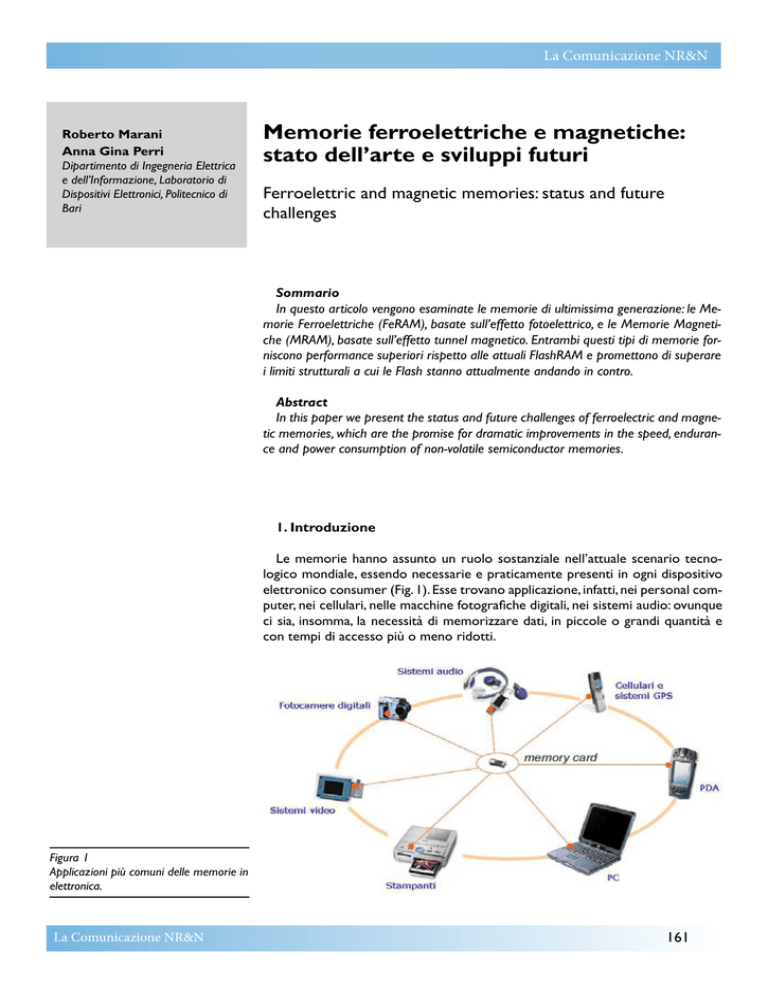

Le memorie hanno assunto un ruolo sostanziale nell’attuale scenario tecnologico mondiale, essendo necessarie e praticamente presenti in ogni dispositivo

elettronico consumer (Fig. 1). Esse trovano applicazione, infatti, nei personal computer, nei cellulari, nelle macchine fotografiche digitali, nei sistemi audio: ovunque

ci sia, insomma, la necessità di memorizzare dati, in piccole o grandi quantità e

con tempi di accesso più o meno ridotti.

Figura 1

Applicazioni più comuni delle memorie in

elettronica.

La Comunicazione NR&N

161 161

R. Marani, A. G. Perri

Esistono diversi tipi di memoria, a seconda della capacità di memorizzazione

e del tempo necessario a reperire l’informazione in esse contenuta. Le memorie

sono generalmente organizzate in matrici bidimensionali di celle, ognuna delle

quali preposta alla memorizzazione di un bit.

L’accesso a ciascuna cella avviene secondo un meccanismo noto come accesso casuale, perchè la lettura del contenuto di ciascuna cella avviene in un tempo

indipendente dalla posizione occupata dalla cella nella matrice.

Le memorie a semiconduttore tradizionali sono realizzate mediante tecnologia

CMOS, che permette l’integrazione monolitica ad altissima scala (ULSI) di dispositivi MOSFET a canale n e a canale p. Peraltro le memorie a semiconduttore

possono essere realizzate secondo tecnologie differenti.

Una classificazione piuttosto importante riguarda la capacità di tali dispositivi

di conservare l’informazione quando questi non sono alimentati.

Le memorie sono dette volatili quando perdono l’intero contenuto informativo in assenza di alimentazione; sono non volatili quelle memorie che mantengono l’informazione anche in assenza di alimentazione.

In generale, le memorie volatili permettono un accesso più rapido al contenuto binario in esse memorizzato: è possibile accedere in lettura e/o scrittura

con tempi di accesso molto ridotti, bassi livelli di potenza e memorizzare grandi

quantità di dati. Al contrario, le memorie non volatili hanno tempi di accesso

sensibilmente più lunghi e mantengono, almeno attualmente, consumi di potenza

piuttosto elevati.

La tendenza attuale è quella di unire i vantaggi di entrambi tipi di memoria,

realizzando dispositivi in grado di mantenere l’informazione anche in assenza di

alimentazione, accedendo rapidamente al contenuto binario e con bassi livelli di

potenza. Molto significativa è, inoltre, la durata di una memoria a semiconduttore

che deve essere la più lunga possibile.

Nella Fig. 2 è mostrata la classificazione delle memorie nelle due grandi famiglie

di memorie volatili e non volatili.

Come si può facilmente osservare, ognuno dei due gruppi è costituito da tipi

diversi di dispositivi, a seconda delle loro intrinseche caratteristiche e delle modalità di funzionamento.

Per quanto riguarda il caso delle memorie volatili, esse adottano in generale teconologia CMOS ed hanno una complessità minore nel caso di DRAM (Dynamic

Random Access Memory) e maggiore nel caso di SRAM (Static RAM).

Figura 2

Classificazione delle memorie

162

La Comunicazione NR&N

Memorie ferroelettriche e magnetiche: stato dell’arte e sviluppi futuri

Ferroelectric and magnetic memories : status and future challenges

Le memorie non volatili racchiudono diverse famiglie di dispositivi, quasi tutti

basati sulla cella elementare con MOS floating gate, nella sua struttura base o

rielaborata per migliorarne le prestazioni.

Alle memorie non volatili appartengono anche le memorie ferroelettriche e

magnetiche che, impiegando principi di base e tecnologie differenti, permettono

il miglioramento spinto delle prestazioni e la conservazione, per tempi teoricamente indeterminati, delle informazioni in esse contenute.

In questo articolo vengono esaminate le memorie di ultimissima generazione:

le Memorie Ferro-elettriche (FeRAM), basate sull’effetto fotoelettrico, e le Memorie Magnetiche (MRAM), basate sull’effetto tunnel magnetico. Entrambi questi

tipi di memorie forniscono performance superiori rispetto alle attuali FlashRAM

e promettono di superare i limiti strutturali a cui le Flash stanno attualmente

andando in contro.

2. Memorie ferroelettriche: brevi cenni storici

Le memorie ferroelettriche rappresentano un’importante evoluzione tecnologica in quanto presentano, rispetto alle memorie a semiconduttore, indiscusse

migliorie in termini di velocità, durata e consumo di potenza.

Le attuali memorie Flash e le EEPROM permettono la memorizzazione in

modo non volatile di grandi quantità di dati ma richiedono alte tensioni di programmazione, tempi di programmazione lunghi ed una vita pari a qualche milione

di cicli di programmazione.

Altri tipi di tecnologie sono state dunque studiate per permettere la produzione di memorie a semiconduttore caratterizzate da basse tensioni di programmazione, tempi di programmazione più veloci ed una durata teoricamente illimitata.

Particolare importanza rivestono le memorie ferroelettriche e le memorie

magnetiche a film sottile, le prime basate sulla variazione dello stato di polarizzazione di un condensatore ferroelettrico, le seconde basate sull’impiego del

cosiddetto effetto magneto-resistivo gigante, che verrà discusso in seguito.

Le memorie non volatili ferroelettriche furono sviluppate e brevettate nei primi anni cinquanta, e già dimostrarono ottime caratteristiche in termini di durata,

velocità e basse tensioni di programmazione.

Una delle prime architetture brevettate si deve a J.R Anderson, che di fatto aggiungeva a ciascun elemento di memoria una coppia di diodi in serie per ridurre

la caduta di tensione sulle celle di memoria deselezionate.

Tale architettura, mostrata in Fig. 3, richiedeva una tensione di breakdown

Figura 3

Memoria ferroelettrica brevettata da

Anderson

La Comunicazione NR&N

163 361

R. Marani, A. G. Perri

inversa della serie di diodi (rappresentata dai due triangoli con un rettangolo in

comune) maggiore della tensione di commutazione del condensatore ferroelettrico.

Le architetture attuali sono simili a quella proposta da Anderson, anche se

hanno sostituito il dispositivo a diodi con strutture MOS.

Durante gli anni sessanta e settanta molti studi sono stati fatti per combinare

le tecnologie ferroelettriche con le convenzionali tecnologie del silicio. L’idea era

quella di creare un transistore MOS con un gate di materiale ferroelettrico, così

da realizzare una cella di memoria basata sugli effetti di modulazione della polarizzazione ferroelettrica sulla conduttività del canale del transistore.

Tale tipo di struttura mista è stata subito abbandonata, a causa dell’esistenza di

incompatibilità tra i materiali ferroelettrici ed il silicio.

In particolare, la maggior parte dei materiali ferroelettrici tendono a perdere

ossigeno e a formare uno strato di materiale ridotto durante la fase di annealing.

L’ossigeno perso dallo strato ferroelettrico ossida il silicio nella regione di canale,

rendendo il dispositivo inservibile. Inoltre la permettività dei materiali ferroelettrici è di oltre due ordini di grandezza superiore rispetto a quella dell’ossido di

silicio (3.95 per il SiO2): ciò significa che anche uno strato molto sottile d’ossido di silicio presente sotto lo strato di materiale ferroelettrico impedisce alla

tensione di programmazione di localizzarsi ai capi di quest’ultimo, rendendo il

dispositivo di fatto inservibile.

Per risolvere questi problemi sono state proposte, negli anni ottanta, delle

soluzioni circuitali basate su componenti discreti.

In particolare, come mostrato in Fig. 4, una cella di memoria ferroelettrica è

costituita da un condensatore ferroelettrico discreto in serie con un transistore

MOS, architettura simile a quella proposta da Anderson.

La Word line è la linea di attivazione della cella: se alta essa attiva il MOS che

collega direttamente il condensatore ferroelettrico con l’amplificatore. In questo

modo lo stato di carica del condensatore, che dipende dallo stato di polarizzazione del dielettrico, può essere comparato, dall’amplificatore, con una tensione

di riferimento.

Metalli nobili come il platino vengono utilizzati per realizzare gli elettrodi del

condensatore ferroelettrico. Utilizzando questa architettura scompare il problema legato alla cessione di ossigeno al silicio da parte del materiale ferroelettrico.

164

Figura 4

Schema di cella di memoria con condensatore ferroelettrico discreto

La Comunicazione NR&N

Memorie ferroelettriche e magnetiche: stato dell’arte e sviluppi futuri

Ferroelectric and magnetic memories : status and future challenges

Esistono diversi materiali adatti per realizzare condensatori ferroelettrici.

Il primo materiale utilizzato fu il PZT (Piombo Zirconio Titanato), seguito poi

dall’SBT (Stronzio Bismuto Tantalato): quest’ultimo materiale ha suscitato l’interesse da parte della comunità scientifica a causa della sua maggiore resistenza alla

fatica, rispetto al PZT. Ciò permette di utilizzare elettrodi di platino e garantisce

una vita del componente molto lunga. Il principale svantaggio dell’SBT è la necessità di essere trattato a temperature più alte (700°C) rispetto a quelle del PZT

(450°C), perché le proprietà ferroelettriche siano accentuate.

Un significativo progresso nella tecnologia del PZT si è ottenuto con l’impiego

di elettrodi in LSCO (Lantano Stronzio Cobalto ossido) che, sostituendo gli elettrodi in platino, hanno migliorato le caratteristiche di durata del materiale fino

ad approssimare l’SBT.

Diversi prototipi di memorie ferroelettriche in PZT e SBT sono stati realizzati

e la maggior parte dei problemi di fabbricazione sono stati risolti.

Poiché i processi realizzativi di questo tipo di memoria sono simili ai processi

utilizzati per le classiche DRAM che già incorporano condensatori con dielettrico ad alta costante, c’è da attendersi un altrettanto rapido incremento di densità

di integrazione ed una massiva diffusione del nuovo tipo di memorie sul mercato.

3. Funzionamento delle memorie ferroelettriche

La ferroelettricità, come è noto, è l’allineamento spontaneo dei dipoli elettrici

per mutua interazione sotto l’influenza di un campo elettrico esterno applicato.

Al di sotto di una certa temperatura critica Tc, detta temperatura di Curie,

alcuni isolanti mostrano caratteristiche di ferroelettricità.

La Fig. 5 mostra la dipendenza della permettività dielettrica relativa er dalla

temperatura.

Il termine permettività identifica, diversamente dal termine costante dielettrica, un comportamento non costante, che è tipico dei materiali ferroelettrici.

Poiché la capacità dei condensatori ferroelettrici è direttamente proporzionale alla permettività del materiale ferroelettrico, la curva capacità-temperatura ha

la stessa forma rappresentata in Fig. 5.

Si osservi che, in prossimità della temperatura critica, la permettività relativa

diventa molto elevata per poi decadere secondo la legge di Curie-Weiss data

da:

Figura 5

Andamento della permettività relativa in

funzione della temperatura

La Comunicazione NR&N

er =

C

T − Tc 1)

165 561

R. Marani, A. G. Perri

dove C è la costante di Curie e T è la temperatura.

Poiché lo stato ferroelettrico non esiste al di sopra della temperatura di Curie,

è importante che quest’ultima sia, per i materiali ferroelettrici impiegati, superiore alle temperature di esercizio.

Materiali come PZT ed SBT sono caratterizzati da una cella unitaria detta di

perovskite e rappresentata in Fig. 6.

La struttura cristallina è di tipo ABO3, dove B è un catione (Zirconio per il

PZT) localizzato al centro della cella unitaria, A è un catione relativamente grande (Piombo per il PZT) localizzato sugli spigoli della cella unitaria, O è un anione

di ossigeno localizzato al centro di ogni faccia della cella.

A temperatura più alta della temperatura di Curie, la struttura della perovskite

ha una simmetria cubica ed è paraelettrica.

Al di sotto della temperatura di Curie la cella perde la sua simmetria cubica

per assumere una struttura tetragonale, ortorombica o romboedrica.

Dalla Fig. 6 si osserva che il catione B possiede due posizioni di equilibrio stabile, che ne determinano l’effetto ferroelettrico, posizioni che possono essere controllate da un campo elettrico esterno.Tali materiali trovano dunque applicazione

come dielettrici per la realizzazione di condensatori ferroelettrici. L’applicazione

di una tensione ad un condensatore siffatto produce un cambiamento nella posizione del centroide carico nel materiale ferroelettrico.

Figura 6

Struttura di un cristallo di perovskite

ABO3

166

La Comunicazione NR&N

Memorie ferroelettriche e magnetiche: stato dell’arte e sviluppi futuri

Ferroelectric and magnetic memories : status and future challenges

Applicando un campo elettrico esterno ad un condensatore ferroelettrico si

ottiene una curva di isteresi, mostrata in Fig. 7, che mette in relazione la polarizzazione P con la tensione applicata.

La curva satura ad un valore di polarizzazione massimo Ps. Una volta raggiunto questo valore di polarizzazione è possibile osservare, dopo aver rimosso il

campo elettrico esterno, un decadimento della polarizzazione fino ad un valore

residuo Pr detto polarizzazione residua.

Tale decadimento non si verifica istantaneamente ma nell’arco di qualche millisecondo.

Il vettore spostamento di Maxwell D deve essere riscritto in modo da tenere

conto sia del campo elettrico esterno E sia della polarizzazione P:

D = e0E + P

2)

dove e0 è la permettività dello spazio vuoto.

Per la maggior parte dei materiali ferroelettrici si ha che il termine e0E è minore di P e ciò implica che D è circa eguale a P, ovvero che la curva di isteresi

mostrata in Fig. 7 rappresenta anche l’andamento di D in funzione del campo

elettrico applicato.

La polarizzazione ferroelettrica può cambiare in meno di un nanosecondo:

ciò permette sia di memorizzare sia di leggere lo stato di un bit con velocità di

accesso molto elevate.

Si tenga presente che ad ogni stato di polarizzazione è associato lo stato di un

bit. Per leggere a quale stato si trova il bit è necessario quindi stabilire a quale

stato di polarizzazione si trova il materiale ferroelettrico.

A tal proposito viene forzato un impulso di tensione molto stretto, della durata di qualche decina di nanosecondi: se tale impulso è tale da opporsi allo stato di

polarizzazione residua, viene prodotta una commutazione di polarizzazione con

la conseguente generazione di un impulso di corrente detta di commutazione.

Figura 7

Curva di isteresi per un materiale ferroelettrico

La Comunicazione NR&N

Tale impulso di corrente è sufficientemente largo, e può essere facilmente

rilevato da un amplificatore per determinare lo stato di polarizzazione iniziale.

167 761

R. Marani, A. G. Perri

4. La magnetoresistenza gigante

La scoperta della magnetoresistenza gigante GMR (Giant MagnetoResistance),

avvenuta nel 1988, nelle strutture a strato ferromagnetiche, ha dato origine ad

una vera e propria rivoluzione nel mondo dell’elettronica, con interessanti ricadute nel settore delle memorie.

La GMR è la variazione della resistenza di una struttura complessa, costituita

dall’alternanza di strati magnetici e non-magnetici, quando l’orientazione relativa

delle magnetizzazioni in strati magnetici adiacenti commuta a seguito dell’applicazione di un intenso campo magnetico.

Nella Fig. 8 è mostrata la struttura base, costituita da due strati magnetici ed

uno strato metallico non magnetico. La magnetizzazione di ogni strato magnetico dipende, in assenza di campo, dal suo spessore. E’ dunque possibile scegliere

gli spessori dei due strati magnetici in modo da garantire, in assenza di campo

magnetico applicato, magnetizzazioni antiparallele degli strati magnetici adiacenti

(configurazione anti-ferromagnetica, AF).

La Fig. 8 si riferisce al caso di una struttura GMR in cui lo strato magnetico

superiore ha uno spessore maggiore di quello inferiore. In tale condizione la resistenza offerta dalla struttura multistrato al passaggio di corrente di elettroni,

perpendicolare alla direzione di accrescimento degli strati, è molto elevata.

Strato magnetico

Strato non magnetico

Strato magnetico

A seguito dell’applicazione di un campo magnetico sufficientemente intenso,

è possibile variare l’orientazione della magnetizzazione di uno dei due strati in

modo da ottenere una condizione di parallelismo delle due magnetizzazioni: tale

stato, detto ferromagnetico (FM), garantisce una bassa resistenza al passaggio

di corrente elettrica, costituita da elettroni aventi spin opportuno.

E’ possibile definire un fattore di merito, indicato con GMR, che indica la variazione relativa di conduttanza tra i due stati di funzionamento del dispositivo:

GMR =

G FM − G AF

3)

G AF

in cui GAF e GFM indicano rispettivamente la conduttanza della struttura in

condizioni di funzionamento antiparallela e parallela.

E’ ovviamente auspicabile che la GMR sia la più alta possibile, in modo che vi sia

la massima differenza possibile tra la conduttanza allo stato ferromagnetico (alta)

e la conduttanza allo stato anti-ferromagnetico (bassa).

I primi esperimenti sulla GMR sono stati effettuati imponendo un flusso di

corrente nel piano degli strati (Current In Plane) non ottenendo, tuttavia, valori

sufficientemente elevati del fattore GMR.

Un importante passo in avanti, verso il raggiungimento di GMR sempre più

168

Figura 8

Struttura base GMR

La Comunicazione NR&N

Memorie ferroelettriche e magnetiche: stato dell’arte e sviluppi futuri

Ferroelectric and magnetic memories : status and future challenges

elevate, è stato ottenuto imponendo un flusso di corrente nella direzione perpendicolare agli strati costituenti la struttura (Current Perpendicular Plane). Alcuni

autori hanno dimostrato l’effettiva maggiore efficienza di quest’ultima architettura rispetto alla prima, in termini di migliori valori di GMR, in quanto il trasporto

di carica interessa non un solo strato, come nel caso della prima struttura ipotizzata, ma tutti gli strati che compongono la struttura.

Una miglioria del sistema rispetto alla configurazione evidenziata nella Fig. 8

consiste nell’utilizzare un numero elevato di strati, alternativamente magnetici e

non magnetici, come mostrato in Fig. 9. Ciò permette di ottenere valori maggiori

di resistenza elettrica, soprattutto in condizione di anti-ferromagnetismo.

Tuttavia questa soluzione presenta alcuni inconvenienti, legati principalmente

alla complessità della struttura composita realizzata. In particolare la struttura

bulk rende disordinato e non omogeneo il trasporto di cariche.

5. Memorie magnetiche: le MRAM a valvole di spin

Una RAM magnetica (MRAM), mostrata in Fig.10, è costituita da due strati

magnetici separati da uno non magnetico (o barriera-tunnel). Quest’ultimo ha la

funzione di separare i due strati precedenti e di rendere indipendenti le rispettive magnetizzazioni M1 ed M2.

A

B

C

Strato M1

Strato M2

Figura 9

Configurazioni multistrato (a) anti-ferromagnetiche e (b) ferromagnetiche

Output

Figura 10

Valvola di spin

La Comunicazione NR&N

169 961

R. Marani, A. G. Perri

Tale struttura, detta anche valvola di spin (spin valve), basa il suo principio

di funzionamento sul concetto di magnetoresistenza gigante: la variazione della

magnetizzazione di uno dei due strati provoca una variazione della resistenza

elettrica al passaggio di una corrente. La codifica di uno dei due stati di un bit è

legata proprio alla resistenza della valvola di spin, che si mantiene anche in assenza di alimentazione.

La scrittura di un bit richiede, pertanto, un campo megnetico che possa ruotare la magnetizzazione di uno dei due strati.

Ciò può essere ottenuto tramite una corrente, di intensità opportuna, da inviare su una linea elettrica dedicata.

Con riferimento alla Fig. 10, una intensa corrente sulla linea A può essere in

grado di modificare lo stato di magnetizzazione M1 e di variare la resistenza

dell’intera struttura. La lettura può essere effettuata tramite la misura della resistenza della valvola, operazione che non distrugge l’informazione immagazzinata

e che non richiede il refresh, tipico delle memorie realizzate in tecnologia CMOS.

Ciò determina una maggiore velocità delle memorie magnetiche rispetto alle

corrispondenti memorie DRAM, oltre ad un maggior numero di operazioni che

è teoricamente possibile prevedere.

La struttura a valvola di spin permette, inoltre, di realizzare facilmente porte

logiche veloci.

Con riferimento sempre alla Fig. 10, una singola valvola con due linee di input

indipendenti (A e B) è in grado di memorizzare un bit e implementare le funzioni

logiche AND e OR. Le linee di input, A e B, sono attraversate da correnti positive

o negative ±IA e ±IB di uguale intensità. Ciascuna delle due correnti da sola non

è in grado di invertire la magnetizzazione M1, a meno che non agisca congiuntamente con la corrente sull’altro ingresso: le due correnti IA e IB insieme, sono in

grado di ruotare M1 ma non M2. Per ottenere la rotazione anche della magnetizzazione M2 è necessario ricorrere all’impiego di una ulteriore linea C di ingresso.

Nella Fig. 11 è rappresentata una valvola di spin impiegata per realizzare una

porta AND. Assumendo come positiva la magnetizzazione dello strato inferiore

M2, rappresentata con una freccia diretta verso destra, l’allineamento della magnetizzazione M1 verso destra determina la configurazione pa

rallela alla quale corrisponde un “1” logico.

Diversamente, l’allineamento della magnetizzazione M1 verso sinistra determina la configurazione antiparallela alla quale compete la massima magnetoresistenza e, quindi, uno “0” logico in uscita.

Da un punto di vista operativo si imposta la struttura perché essa inizialmente

sia in configurazione antiparallela (0 logico in uscita) mediante l’imposizione di

correnti negative su entrambi gli ingressi A e B (0 logico su entrambi gli ingressi).

170

Figura 11

Porta AND a valvola di spin

La Comunicazione NR&N

Memorie ferroelettriche e magnetiche: stato dell’arte e sviluppi futuri

Ferroelectric and magnetic memories : status and future challenges

Una volta in questa condizione, sarà possibile invertire lo stato di magnetizzazione di M1 (e quindi ottenere un “1” logico in uscita) solo imponendo entrambe

le correnti positive sugli ingressi A e B.

Diversamente, nel caso in cui almeno uno degli ingressi sia “0”, il campo magnetico coercivo prodotto non è sufficiente ad invertire la direzione di magnetizzazione M1 dello strato superiore.

La Fig. 12 rappresenta schematicamente quanto esposto.

Nella configurazione (a) le correnti sugli ingressi, essendo negative, non invertono lo stato di magnetizzazione M1, facendo permanere lo stato di elevata

magnetoresistenza tra gli strati magnetici.

Nel caso (b) le due correnti in ingresso, essendo contropropaganti, non generano un campo magnetico sufficiente a produrre l’inversione della magnetizzazione M1, producendo ancora uno “0” logico in uscita.

Nel caso (c) le due correnti, che scorrono entrambe verso destra, riescono a

produrre un campo coercitivo sufficientemente elevato da invertire la direzione

di magnetizzazione M1, producendo un abbassamento della GMR ed un “1” logico

in uscita.

Per realizzare porte NAND è necessario negare l’uscita della porta AND corrispondente (cfr. Fig. 13).

Figura 12

Porta AND a due ingressi

Ciò può essere ottenuto invertendo la direzione di magnetizzazione M2, mediante l’introduzione di un ulteriore linea elettrica in grado di potenziare il campo coercivo prodotto dalle linee A e B.

Figura 13

Porta NAND

La Comunicazione NR&N

171 171

R. Marani, A. G. Perri

6. Conclusioni

In questo articolo sono state esaminate le memorie di ultimissima generazione:

le Memorie Ferro-elettriche (FeRAM) e le Memorie Magnetiche (MRAM).

Entrambi questi tipi di memorie forniscono performance superiori rispetto

alle attuali FlashRAM e promettono di superare i limiti strutturali a cui le Flash

stanno attualmente andando in contro.

In particolare le RAM magnetiche (MRAM) possono raggiungere timings teorici di 2.3 nanosecondi in scrittura. Si tratta di un tempo 1,000 volte più veloce delle attuali FlashRAM e 20 volte maggiore delle più veloci FeRAM, che comunque

ma rappresentano un passo avanti non indifferente rispetto alle attuali memorie

Flash.

Inoltre le MRAM accedono in lettura in 3 ns, circa 20 volte più veloce della

memoria DRAM e consumano meno di 1/100 rispetto alle DRAM.

Riteniamo, in definitiva, che le MRAM potranno sostituire le celle di SRAM

essendo veloci, piccole e resistenti alle radiazioni.

Bibliografia e webgrafia di riferimento

A. G. Perri: “Fondamenti di Dispositivi Elettronici”; Ed. Progedit, 2010, ISBN

978-88-6194-080-2.

A. G. Perri: “Dispositivi Elettronici Avanzati”; Ed. Progedit, 2011, ISBN 978-886194-081-9.

J.R. Anderson, “Electrical circuits employing ferroelectric capacitors,” U.S. Patent No. 2,876,436, 1959.

C.A. Paz de Araujo et al., “Fatigue-free ferroelectric capacitors with platinum

electrodes”, Nature, vol. 374, no. 627, 1995.

Fujitsu Limited, FRAM GUIDE BOOK, Fujitsu Semiconductor Manual, 2005.

http://physics.unl.edu/~tsymbal/tsymbal_files/GMR/gmr.html

www.lithium.it

www.hwupgrade.it/memorie.hwu

172

La Comunicazione NR&N