ELETTRONICA PER L’INFORMATICA

ESERCITAZIONE DI LABORATORIO 2

Sede di IVREA

Esercitazione di laboratorio 2

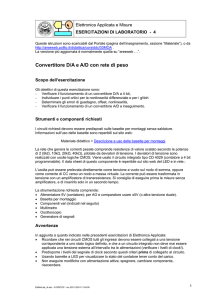

Convertitore D/A e A/D con rete di peso

Scopo dell’esercitazione

Gli obiettivi di questa esercitazione sono:

- Verificare il funzionamento di un convertitore D/A a 4 bit,

- Individuare i punti critici per la nonlinearità differenziale

- Individuare i punti critici per i glitch

- Determinare gli errori di guadagno, offset, nonlinearità,

- Verificare il funzionamento di un convertitore A/D a inseguimento.

Moduli e componenti da utilizzare

I circuiti richiesti devono essere predisposti sulle basette per montaggi senza saldature.

Informazioni sull'uso delle basette sono reperibili sul sito web:

Materiale didattico > Uso delle basette per montaggi senza saldature

La rete che genera le correnti pesate comprende resistenze di valore scalato secondo le

potenze di 2 (5k, 10k, 20k, 40k), pilotate da deviatori di tensione. I deviatori di tensione sono

realizzati con uscite logiche CMOS. Viene usato il circuito integrato tipo CD 4029 (contatore a

4 bit programmabile). Il data sheet di questo componente è reperibile sul sito web:

L'uscita può essere prelevata direttamente come tensione a vuoto sul nodo di somma,

oppure come corrente di CC verso un nodo a massa virtuale (morsetto di ingresso di un

amplificatore a transresistenza).

Strumenti richiesti

Alimentatore (5 V), generatore di clock (1 MHz compatibile CMOS), oscilloscopio, multimetro.

Le verifiche di funzionamento dei circuiti vanno eseguite con l’oscilloscopio.

Le misure di tensione vanno eseguite con il multimetro.

Avvertenze

Ricordare che nei circuiti CMOS tutti gli ingressi devono essere collegati a una tensione

corrispondente a uno stato logico ben definito, e che a un circuito integrato non deve mai

essere applicata una tensione esterna all’intervallo tra le alimentazioni.

Predisporre i livelli del segnale di clock secondo questi criteri.

ELINFlab2e - © DDC/CP - rev 20/05/2007 9:33 AM

0

ELETTRONICA PER L’INFORMATICA

ESERCITAZIONE DI LABORATORIO 2

Sede di IVREA

Convertitore D/A

Lo schema di sinistra è un convertitore D/A a correnti pesate con uscita in corrente, in cui il

dato digitale di ingresso proviene da un contatore binario a 4 bit (integrato CD 4029). Nel

circuito equivalente Thevenin di questo convertitore (sezione AA verso sinistra) la resistenza

equivalente di uscita è indipendente dalla posizione dei deviatori (cioè dallo stato delle uscite

del CD 4029), e quindi la tensione a vuoto è proporzionale alla corrente di cortocircuito in

uscita. Il circuito può quindi essere direttamente trasformato in convertitore con uscita in

tensione (schema di destra).

Nell’esercitazione viene utilizzato il circuito del D/A a 4 bit della figura di destra, con uscita in

tensione. La tensione va misurata a vuoto (solo oscilloscopio o multimetro). Per pilotare

eventuali carichi interporre un buffer, o usare il circuito di destra con amplificatore di

transresistenza.

CK

CD 4029

Q1 Q2 Q3 Q4

R1

R2

R3

R4

39 kΩ

20 kΩ

10 kΩ

5 kΩ

CD 4029

CK

Q1 Q2 Q3 Q4

R1 R2 R3 R4

R1 R2 R3 R4

A

A

Iu

Vu

1. Iniziare montando il contatore, configurato per conteggio modulo 16 a salire. Per

verificare il funzionamento applicare un segnale di clock a onda quadra, e controllare la

sequenza di stati sulle uscite del contatore.

Collegare tutti gli ingressi del contatore CMOS

Attenzione ai livelli del clock esterno !

2. Montare la rete di peso: la resistenza da 5 KΩ è ottenuta con due resistenze da 10 kΩ in

parallelo, e quella da 20 kΩ con due resistenze in serie. Applicando un segnale continuo

di clock verificare che in uscita compaia una gradinata di 16 livelli equispaziati.

3. Mantenendo il clock continuo all’ingresso, misurare con l’oscilloscopio i livelli di ciascun

gradino; determinare il fondo scala S e il valore del LSB.

4. Inserire sulle uscite del contatore i LED (con la basetta premontata o con una resistenza

serie da 1 kohm), per visualizzarne lo stato. Ripetere la verifica del punto 3); cosa è

cambiato e perchè ? Come possiamo collegare dei LED per visualizzare lo stato del

contatore senza introdurre errori nell’uscita analogica ?

5. Modificare del 15% circa le resistenze corrispondenti a MSB, MSB-1, MSB-2, LSB (solo

un ramo per volta - inserire un’altra resistenza in serie o in parallelo). Verificare l’effetto di

ciascuna modifica. Quale relazione c’è tra peso del ramo modificato e posizione in cui

viene alterata la caratteristica ?

6. Come e di quanto deve essere modificata la resistenza del MSB per introdurre errore di

non monotonicità ? Eseguire calcolo e verifica sperimentale.

ELINFlab2e - © DDC/CP - rev 20/05/2007 9:33 AM

0

ELETTRONICA PER L’INFORMATICA

ESERCITAZIONE DI LABORATORIO 2

Sede di IVREA

7. Inserire sulle uscite del contatore piccole capacità verso massa (da 50 pF a 1 nF), per

variare i ritardi di commutazione e introdurre dei glitch. Verificare la corrispondenza tra

posizione del condensatore e posizione/verso dei glitch.

8. Scollegare il generatore di clock, e dare singoli impulsi a mano (resistenza di pullup e

chiusura verso massa). Verificare che il numero di impulsi di clock forniti in questo modo

è casuale (conviene tenere i LED inseriti per visualizzare lo stato del contatore).

9. Inserire un circuito antirimbalzo con FF SR (come per l’ultima esercitazione di Sistemi

Elettronici), e verificare che con questo è possibile far avanzare il contatore uno stato alla

volta.

10. Facendo avanzare il contatore passo-passo con l’interruttore e circuito antirimbalzo

(oppure con il generatore esterno a frequenza molto bassa), misurare i livelli di ciascun

gradino con il tester; e verificare che l’intervallo tra gradini adiacenti corrisponde a 1 LSB.

Il risultato di questa misura è diverso a seconda che il gruppo di LED sia collegato o

meno. Con i LED collegati la corrente assorbita nello stato L alza il livello VOL. Per

confrontare le misure con la caratteristica ideale del convertitore D/A, occorre staccare i

LED (controllare lo stato con i LED, staccare il LED del ramo in cui si esegue la misura).

11. Trasformare il circuito inserendo l’amplificatore di transresistenza come indicato in figura.

Alimentare l0operazionale a +- 10 V. Progettare R5 per ottenere un fondo scala di–5V

(approssimativamente).

CK

CD 4029

Q1 Q2 Q3 Q4

R1

R2

R3

R4

39 kΩ

20 kΩ

10 kΩ

5 kΩ

R1 R2 R3 R4

R5

Vu

12. Usare al posto delle resistenze pesate una rete a scala R/2R. Quale deve essere il valore

R/2R per avere lo stesso fondo scala senza modificare R5 ?

13. Con la rete a scala, ripetere le verifiche sul funzionamento indicate al punto 2 e 3.

ELINFlab2e - © DDC/CP - rev 20/05/2007 9:33 AM

0

ELETTRONICA PER L’INFORMATICA

ESERCITAZIONE DI LABORATORIO 2

Sede di IVREA

Esperienza dimostrativa D/A

La figura indica (per un DAC a 4 bit) la

corrispondenza tra stati del contatore

e tensione di uscita (nel caso di

conteggio sequenziale una rampa).

Sono riconoscibili le posizioni

corrispondenti a metà del fondo scala

(commutazione del MSB), i quarti, e

così via. Verificare che introducendo

anomalie (ritardi, errori nella rete di

peso) su un determinato bit, gli effetti

sono evidenti nel punto in cui il bit

cambia stato.

Per osservare la rampa in uscita e i

segnali digitali conviene sincronizzare

l’oscilloscopio sul segnale digitale più

lento (uscita Q4).

ELINFlab2e - © DDC/CP - rev 20/05/2007 9:33 AM

0

ELETTRONICA PER L’INFORMATICA

ESERCITAZIONE DI LABORATORIO 2

Sede di IVREA

Nonlinearità differenziale

Le foto di questa pagina evidenziano errori di nonlinearità differenziale ottenuti modificando la

corrente di un ramo della rete di peso (o della rete a scala) con una resistenza inserita in

parallelo al ramo stesso. La rampa è formata da 64 gradini (convertitore a 6 bit).

La resistenza è in parallelo al ramo del MSB.

L’errore si manifesa come un incremento del

peso del MSB (dovuto all’incremento della

corrente nel ramo), che determina un

“innalzamento” della seconda metà della

caratteristica (corrispondente alla parte in cui

MSB = 1).

Inserendo la resistenza in parallelo al ramo del

MSB-1 si modificano il secondo e il quarto

“quarto”, in cui MSB-1 = 1. L’errore introdotto sul

ramo è sempre lo stesso; dato però che il peso

del ramo è metà rispetto al caso precedente,

l’effetto in uscita è dimezzato.

A metà del fondo scala la caratteristica diventa

non-monotona.

Spostando la resistenza sul ramo MSB-2 si nota

che l’errore interviene per “ottavi” del fondo

scala, con ampiezza ulteriormente dimezzata.

L’entità dell’errore non è più tale da determinare

non-monotonicità.

Ritardando la commutazione del MSB-1;

compaiono glitch in corrisponenza della

metà e dei quarti di fondo scala. La

direzione del glitch dipende dal verso della

commutazione del bit: ritardando il

passaggio da 0 a 1 si introduce uno stato

temporaneo 000.. (glitch verso massa);

ritardando il passaggio da 1 a 0 lo stato

transitorio è 111…, che determina un glitch

verso il fondo scala.

ELINFlab2e - © DDC/CP - rev 20/05/2007 9:33 AM

0

ELETTRONICA PER L’INFORMATICA

ESERCITAZIONE DI LABORATORIO 2

Sede di IVREA

Convertitore A/D

Trasformare il circuito in convertitore A/D, come indicato in figura (convertitore A/D a

inseguimento). L’operazionale viene usato come comparatore tra la tensione Vu generata

dalla rete di peso e la Vi di ingresso. Il contatore viene continuamente incrementato o

decrementato (comando U/D), a seconda che la tensione Vu ricostruita attraverso il D/A sia

maggiore o minore della Vi.

CK

CD 4029

U/D

Q1 Q2 Q3 Q4

R1 R2 R3 R4

Vu

Per adattare i livelli presenti in uscita

dell’operazionale ai livelli richiesti per il

comando up/down del contatore si usa la

rete formata dalla resistenza R6 e diodo

zener. Utilizzare uno zener da 3,9 o 4,1 V,

con R6 = 1 kΩ.

Va

In alternativa è possibile alimentare sia il contatore del D/A che il comparatore con una

tensione 0-7 V. In questo caso, per il comparatore, è preferibile usare amplificatori

operazionali con uscita “rail to rail”, ad esempio tipo TL081

Per questa esperienza occorrono due generatori;

- generatore del segnale Va (ingresso al convertitore A/D)

- generatore di onda quadra per il clock CK. Questo potrebbe essere realizzato con il

circuito oscillatore a onda quadra visto nell’esercitazione precedente.

Come comparatore conviene usare un operazionale veloce (ad esempio LM748), o un

comparatore vero e proprio. Il componente LM741 (operazionale compensato per essere

stabile a guadagno unitario) è molto lento, e i ritardi di commutazione dell’uscita possono

pregiudicare il funzionamento come convertitore A/D.

Visualizzare lo stato del contatore collegando alle uscite il gruppo di LED premontato, o

singoli LED con resistenze da 4,7 KΩ in serie (verso l’alimentazione).

Facendo variare molto lentamente l’ingresso analogico Va, verificare il funzionamento e

tracciare la transcaratteristica D(A).

ELINFlab2e - © DDC/CP - rev 20/05/2007 9:33 AM

0

ELETTRONICA PER L’INFORMATICA

ESERCITAZIONE DI LABORATORIO 2

Sede di IVREA

Esperienza dimostrativa A/D

E’ possibile verificare il funzionamento dinamico del convertitore applicando un segnale Vi di

ampiezza corrispondente al fondo scala e frequenza bassa, tale che lo slew rate massimo sia

inferiore allo slew rate ottenibile sulla Vu (pari ad Ad/Tck).

Nell’immagine compaiono

le tensioni Va e Vu: Va è

la tensione sinusoidale, e

Vu il segnale ricostruito

attraverso il D/A, che si

modifica in modo da

inseguire continuamente

Va. La differenza Va – Vu

è l’errore di

quantizzazione.

Espandendo l’asse tempi si

osservano i singoli passi

dell’inseguimento, a gradini

di ampiezza costante in

discesa o in salita. Quando

il segnale varia entro 1 LSB

(zona indicata dall’ellisse

gialla) si ha una sequenza

di passi in salita e discesa

alternati.

Nella zona a derivata massima (attraversamento del valor medio della sinusoide) il segnale

ricostruito varia alla massima velocità possibile (ellisse rossa, sequenza di gradini in salita)

Aumentando la frequenza del segnale

cresce lo slew rate, e la tensione Vu

non riesce a inseguire Va

determinando un errore di

sovraccarico. Il segnale ricostruito

diventa un’onda triangolare, con

pendenza corrispondente al massimo

slew rate, pari ad Ad/Tck (lo stesso

della zona entro l’ellisse rosso della

figura precedente).

ELINFlab2e - © DDC/CP - rev 20/05/2007 9:33 AM

0