Titolo:

Test progettazione “TP209816DO”

ID No:

QPTR-01

REV.: 1.0

PAGE: 1/7

Test progettazione “TP209816DO”

History

Rev

1.0

Date

APR 03

Description

Test progettazione TP209816DO

By

Parenzan

Author: Parenzan

Approved D.T.

Approved Q.A.

Date:

Date:

Date:

The reproduction, transmission or use of this document or its contents is

not permitted without express written authority. Offenders will be liable

for damages. All rights, including rights created by patent grant or

registration of a utility model or design, are reserved. Technical data

subject to change. Copyright © 2000-2001 Sitek Spa All Rights Reserved.

SITEK Confidential & Proprietary

File: 582825029

Titolo:

Test progettazione “TP209816DO”

ID No:

QPTR-01

REV.: 1.0

PAGE: 2/7

Indice

1. Scopo del test ............................................................................................ 3

2. Modalità di esecuzione .............................................................................. 3

3. Condizioni ambientali ed operative ............................................................ 4

3.1. Elenco strumentazione ........................................................................ 4

3.2. Operatore ............................................................................................ 4

3.3. Lista delle verifiche .............................................................................. 5

4. Registrazione risultati ................................................................................ 6

5. Valutazione dati ......................................................................................... 6

6. Tabella di approvazione ............................................................................. 7

SITEK Confidential & Proprietary

File: 582825029

Titolo:

Test progettazione “TP209816DO”

ID No:

QPTR-01

REV.: 1.0

PAGE: 3/7

1. Scopo del test

Lo scopo del test e’ quello di verificare il progetto del modulo TP209816DO avendo come riferimento

il documento di specifica.

2. Modalità di esecuzione

Le prove sono state condotte utilizzando un modulo Cpu TP4092ICU con software monitor per

TpWire e modulo TP209816DOsotto test.

I comandi al monitor TpWire sono stati forniti tramite PC con programma terminale ASCII settato a

115200,n,8,1 collegato alla scheda con relativo cavo seriale.

Il monitor TpWire e’ stato configurato per una velocita’ di 48Mbit/s.

Durante il test e’ stato utilizzato un modulo TP109916DI per rilevare lo stato delle uscite della

TP209816DO in test con un set di 16 cavi di richiusura 1:1 montati sulle morsettiere delle schede.

La tensione di alimentazione nominale e’ stata settata a 24Vdc.

La verifica delle commutazioni delle uscite e’ stata eseguita su ciascuna uscita tramite oscilloscopio

per tensione di alimentazione esterna variabile da 12 a 30V.

Ogni uscita e’ stata sovracaricata a 1A e verificato l’intervento della protezione termica con rilettura

da parte del master delle flag diagnostica. Ogni uscita e’ stata forzata bassa verificando che

applicandovi una tensione di 24V si attivasse la flag diagnostica.

E’ stato condotto il test di inversione della tensione esterna di alimentazione senza danneggiamento

dei drivers scheda.

I test sono stati condotti su tre esemplari di TP209816DO.

I test sotto riportati sono stati definiti in accordo ai criteri della norma IEC 1131-2, in particolare

“Verification Procedure 6.3.2.2”.

1) Durante I test non si devono verificare:

Distruzioni dell’hardware

Modifiche del sistema operativo e di programmi di test e/o alterazioni della loro esecuzione.

Modifiche dei dati in memoria o comunicati.

Comportamento anomalo del sistema PC o microprocessore.

Deviazioni delle uscite dai loro limiti di funzionamento.

2) Test di tutti gli I/O e dei canali di comunicazione

3) Test di tutte le condizioni di start-up e shut-down e reset.

4) Test di tutte le condizioni necessarie per il corretto funzionamento del modulo.

Con riferimento particolare alla scheda TP209816DO:

Si considera superato con successo ed indicato con PASSED un criterio di verifica di un test qualora:

Il test non comporti la distruzione fisica dell’hardware

La scheda non si porti in condizione di reset con indicazione visiva del led rosso acceso

Le logiche implementate vengano correttamente inizializzate al power-up.

La comunicazione tra scheda, master TP4092ICU ed eventuali altri slave presenti in rete non subisca

alterazioni o perdite di dati

Un determinato stato delle uscite non vari e venga correttamente riletta dal master durante tutta la

durata del test

I led che indicano lo stato degli ingressi non subiscano variazioni di stato rispetto alla condizione

forzata durante il test

I driver di uscita non subiscano danni termici, per tensione di alimentazione rovescia e limite di

corrente.

SITEK Confidential & Proprietary

File: 582825029

Titolo:

Test progettazione “TP209816DO”

3. Condizioni ambientali ed operative

Temperatura amb.

Umidità

24.5 °C

40-65%

3.1. Elenco strumentazione

Oscilloscopio HP 4chnl 150Mhz

Multimetro HP 34401A 6+1/2 digit

Alimentatore stabilizzato regolabile HP E3631A

Cavi richiusure ingressi – uscite digitali 1:1 per morsettiere

Scheda cpu TP4092ICU

Modulo TP209816DO sotto test

Modulo TP109916DI campione

PC con software di terminale ASCII

Software monitor TpWire

3.2. Operatore

Dipartimento incaricato:

Lab. Hardware

Persona incaricata:

Parenzan Giovanni

SITEK Confidential & Proprietary

File: 582825029

ID No:

QPTR-01

REV.: 1.0

PAGE: 4/7

Titolo:

Test progettazione “TP209816DO”

ID No:

QPTR-01

REV.: 1.0

PAGE: 5/7

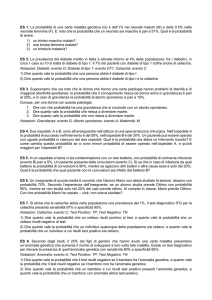

3.3. Lista delle verifiche

Criteri di verifica durante il Test

Assorbimento sul +5V

tutte uscite OFF

Assorbimento sul +5V

tutte uscite ON

Funzionamento 5V per 30’ 0C

Funzionamento 5V per 30’ 70C

Funzionamento 4.75V per 30’

Funzionamento 5.25V per 30’

Funzionamento dopo 1000 cicli

ON/OFF

Attivazione singola uscita per 30’

Vext=24V Iout=500mA

Attivazione singola uscita ed intervento

termico limitazione corrente. Rilettura

uscita diagnostica

Prova di cortocircuito con uscita ON

Rilettura uscita diagnostica. Vext=30V

Forzatura uscita bassa. Applicazione di

Vext=30V sull’uscita. Rilettura uscita

diagnostica

Inversione tensione di alimentazione

esterna

24V.

Attivazione tutte le 16 uscite con

Vext=24V e Iout=500mA

Test attivazione uscite digitali con

rilettura Vext=12V Temperatura=0C

Test attivazione uscite digitali con

rilettura Vext=12V Temperatura=70C

Test attivazione uscite digitali con

rilettura Vext=30V Temperatura=0C

Test attivazione uscite digitali con

rilettura Vext=30V Temperatura=70C

Verifica funzionamento led indicazione

stato ingressi digitali

Verifica pinout connettore segnali input

output modulo in test

Prove EFT Burster tester L+N+PE

SITEK Confidential & Proprietary

File: 582825029

Valori limite

Tolleranze

Max 140mA

Valore

misurato

120mA

Esito del

Test e note

PASSED

Max 300mA

190mA

PASSED

Nessuna

anomalia

Nessuna

anomalia

Nessuna

anomalia

Nessuna

anomalia

Nessuna

anomalia

Min 500mA

Nessuna

anomalia

Nessuna

anomalia

Nessuna

anomalia

Nessuna

anomalia

Nessuna

anomalia

Nessuna

anomalia

Iout = 1A

PASSED

Test su 16

uscite

Test su 16

uscite

Nessuna

anomalia

Nessuna

anomalia

PASSED

Maggiore di

30V

35V

PASSED

Durata 100s

Nessuna

anomalia

Nessuna

anomalia

Nessuna

anomalia

Nessuna

anomalia

Nessuna

anomalia

Nessun

Errore

Nessun

errore

2500V

PASSED

Maggiore

800mA

Nessuna

anomalia

Nessuna

anomalia

Nessuna

anomalia

Nessuna

anomalia

Nessun

Errore

Nessun errore

2000V

PASSED

PASSED

PASSED

PASSED

PASSED

PASSED

PASSED

PASSED

PASSED

PASSED

PASSED

PASSED

PASSED

PASSED

Titolo:

Test progettazione “TP209816DO”

fronte + e Prove EFT Burster tester / fronte + e -

1000V

1200V

ID No:

QPTR-01

REV.: 1.0

PAGE: 6/7

PASSED

4. Registrazione risultati

Tensione alimentazione campo a 12Vdc:

Carico resistivo I=500mA su ogni uscita.

Test ok. Temperatura 46º C in prossimita’ driver potenza.

Tensione alimentazione campo a 24Vdc:

Carico resistivo I=500mA su ogni uscita.

Test ok. Temperatura 63º C in prossimita’ driver potenza.

Tensione alimentazione campo a 24Vdc:

Carico resistivo I=800mA su ogni uscita.

Test ok. Intervento protezione dopo 40 secondi partendo con scheda a temperatura ambiente 20º

Temperatura 90º C in prossimita’ driver potenza mantenendoli in protezione.

Verificati livelli segnale di fail sui driver di potenza e corrispondente optoisolatore verso fpga

Le temperature sono state misurate con sistema in contenitore TH a 1cm dalla superfice della scheda

disposta in posizione orizzontale.

Pwm settato con freq uscita a 100hz .

Verificato possibilita’ inversione polatita’ ciclo pwm

Verificata regolazione da 1% a 100% con risoluzione a 12bit

Vista la risposta in frequenza degli optoisolatori il limite di frequenza del pwm e’ di 500hz per valori

compresi tra il 10% ed il 90%.

Il test di richiusura I/O digitale e’ stato ripetuto con temperatura ambientale di –20° C e

successivamente di +70° C.

Il test di richiusura I/O digitale e’ stato ripetuto alimentando il sistema tramite EFT500 a 2500V

sull’alimentazione in accoppiamento L, N, PE con polarita’ + e -. Inoltre e’ stato condotto il test

sempre con EFT500 sui cavi di richiusura I/O a 1200V con polarita’ + e -.

5. Valutazione dati

I risultati ottenuti confermano i dati della progettazione

SITEK Confidential & Proprietary

File: 582825029

Titolo:

Test progettazione “TP209816DO”

6. Tabella di approvazione

Test n°

Data di esecuzione

Operatore

Ente incaricato esecuzione test.

Procedura utilizzata

SI

NO

Ulteriori test (spiegazione)

Approvazione finale

SITEK Confidential & Proprietary

File: 582825029

Azioni finali ed approvazione

ID No:

QPTR-01

REV.: 1.0

PAGE: 7/7