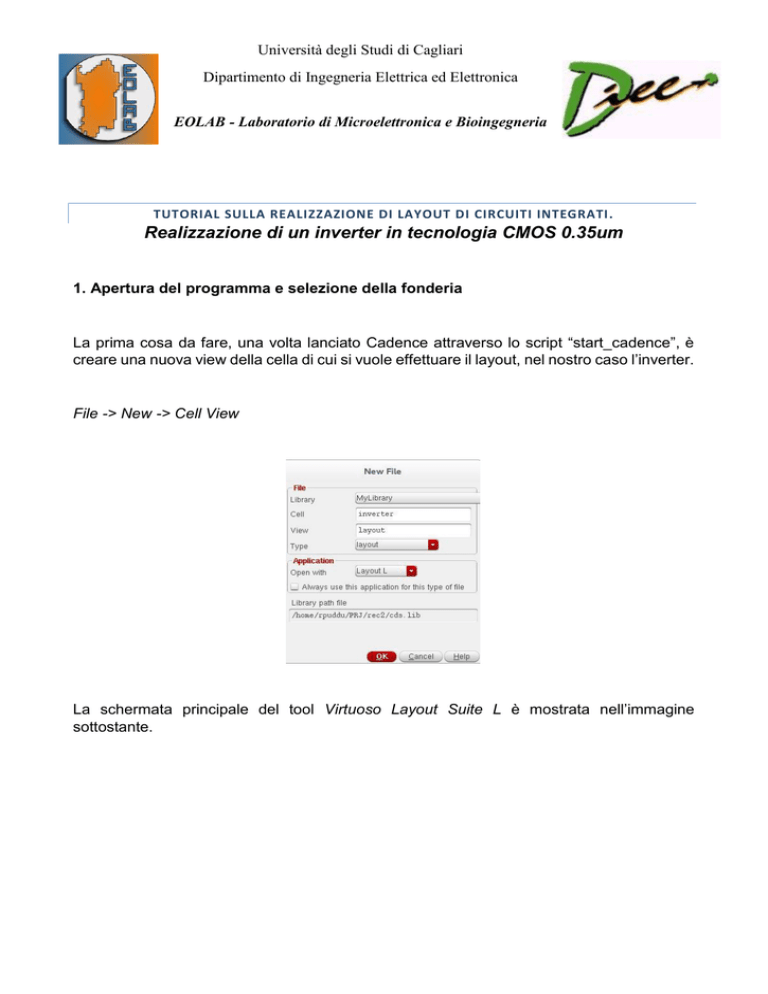

Università degli Studi di Cagliari

Dipartimento di Ingegneria Elettrica ed Elettronica

EOLAB - Laboratorio di Microelettronica e Bioingegneria

TUTORIAL SULLA REALIZZAZIONE DI LAYOUT DI CIRCUITI INTEGRATI.

Realizzazione di un inverter in tecnologia CMOS 0.35um

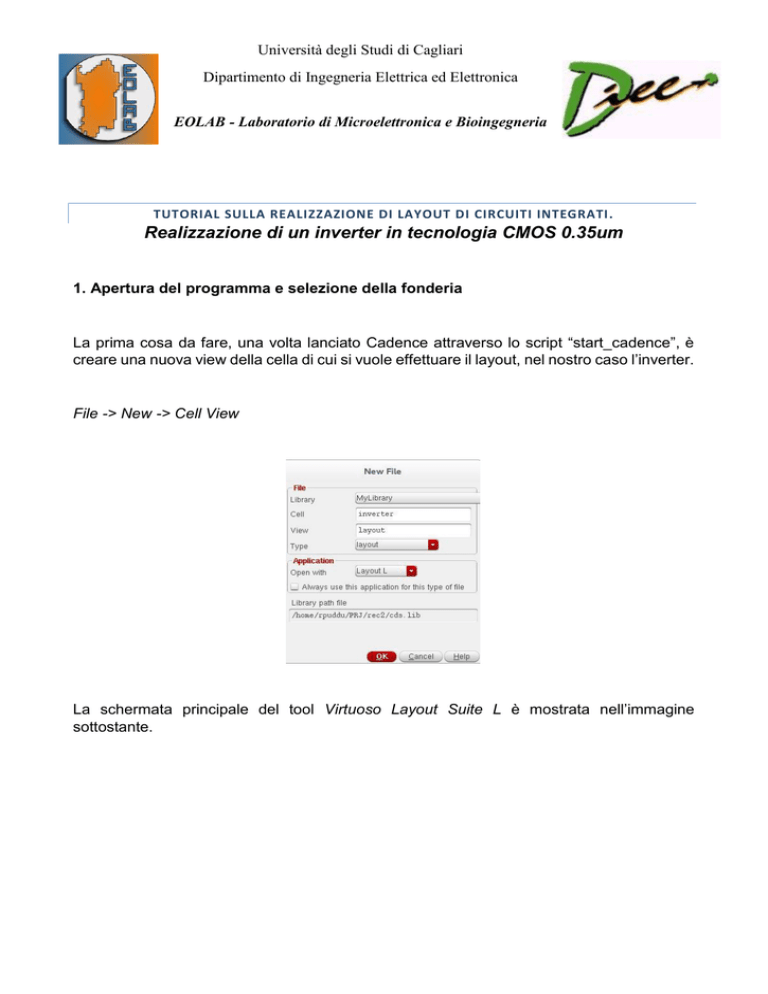

1. Apertura del programma e selezione della fonderia

La prima cosa da fare, una volta lanciato Cadence attraverso lo script “start_cadence”, è

creare una nuova view della cella di cui si vuole effettuare il layout, nel nostro caso l’inverter.

File -> New -> Cell View

La schermata principale del tool Virtuoso Layout Suite L è mostrata nell’immagine

sottostante.

Sulla sinistra è visibile la palette con tutti i layer disponibili nel processo selezionato, un

segno di spunta nella casellina affianco ad un layer nella colonna V significa che il layer

stesso è visibile. Un segno di spunta nella casellina affianco ad un layer nella colonna S

significa che il layer stesso è selezionabile (può essere utile in certe situazioni non

visualizzare o non selezionare alcuni layer).

2. Inserimento MOS

Per generare un MOS di una data W e L:

Create -> Instance (o attraverso il pulsante

)

Comparirà una finestra da cui sarà possibile scegliere le dimensioni del mos (espresse in

micron):

16 Febbraio 2016

Massimo Barbaro e Roberto Puddu

2

In questo caso si disegna un nMOS con W=1u e L=0.35u, premendo poi sul tasto Hide si

ha la possibilità di piazzare il MOS sul layout. Analogamente è possibile inserire il PMOS

(che posizioneremo al di sopra del NMOS):

PMOS

NMOS

16 Febbraio 2016

Massimo Barbaro e Roberto Puddu

3

Ovviamente il MOS può anche essere realizzato interamente usando le opportune

intersezioni di layer di poly e diffusione, la cosa può essere utile quando si vuole

personalizzare il MOS, ad esempio non mettendo il contatto di drain perché si vuole

collegare quel drain al source di un altro MOS dello stesso tipo (in serire) direttamente con

la diffusione.

3. Realizzazione interconnessioni

Per collegare i drain dei due transistor si può disegnare un pezzo di metallo (Create ->

Wiring -> Wire. Oppure tasto p) che connetta le due diffusioni. Per iniziare a disegnare la

connessione cliccare sul punto di partenza e se richiesto scegliere con quale metallo

effettuare l’interconnessione.

L’aspetto finale del layout risulterà il seguente dopo aver connesso anche i gate per mezzo

del polisilicio:

16 Febbraio 2016

Massimo Barbaro e Roberto Puddu

4

E’ ora necessario introdurre un contatto per potere accedere al gate di polisilicio arrivando

dall’esterno con una pista di metal. Questo può essere fatto tramite il menù:

Create -> Via

Bisogna scegliere il tipo di contatto (fra metal e poly P1_C, metal1 e metal2 VIA1_C, metal1

e diffusione N ND_C e così via):

16 Febbraio 2016

Massimo Barbaro e Roberto Puddu

5

In questo caso inseriamo un contatto P1_C e posizioiamolo sopra la pista di polisilicio come

mostrato in Figura:

4. Contatti di bulk (body)

Il passo successivo consiste nell’inserire i contatti di body. La prima cosa che faremo è

contattare la well, per fare questo si cercano di mettere il maggior numero di contatti

possibile per fare in modo che le cadute di potenziale all’interno della well siano minime, si

usa ancora il menu

Create -> Via

16 Febbraio 2016

Massimo Barbaro e Roberto Puddu

6

La via ND_C identifica un contatto tra il metal1 e una diffusione di tipo N mentre la via PD_C

tra metal1 e una diffusione P.

Inseriamo 5 contatti ND_C in parallelo come mostrato in Figura

E’ ormai opportuno effettuare una verifica delle regole di progetto per essere sicuri di non

avere violato nessuna Design Rule.

Assura -> Run DRC

Il risultato è il seguente:

16 Febbraio 2016

Massimo Barbaro e Roberto Puddu

7

Sono state violate alcune regole di progetto.

BAD_SUBSTR_SUBTAP_FLOAT_ERC -> questa regola ci avvisa che non abbiamo

ancora inserito alcun contatto verso il substrato.

INFO: hot nwell -> ci informa che la nwell non è connessa alla tensione di alimentazione.

Per eliminare questa info dovremmo in seguito inserire una label sul contato della nwell che

faccia capire al software che quel nodo sarà connesso alla VDD.

OD_C_1 Minimum NTUB enclosure of NDIFF = 0.2 -> questa regola ci dice che la NTUB,

cioè il layer che identifica l’area in cui verrà realizzata la nwell, deve racchiudere la diffusione

di almeno 0.2 um. Abbiamo violato questa regola nell’inserire i contatti della nwell in quanto

una parte di essi è stata inserita fuori dalla nwell. Per risolvere l’errore dovremmo creare un

rettangolo di nwell e affiancarlo alla nwell già presente. Ai fini del layout due aree

consecutive dello stesso layer sono interpretate come un’unica area.

OD_C_3 Minimum NDIFF to HOT_NTUB spacing (no PTAP in between) = 2.6 -> questa

regola ci dice che la distanza tra una diffusione di tipo N e la HOT_NTUB deve essere di

almeno 2.6 um. In questo caso l’errore è dovuto al fatto che la diffusione di tipo N utilizzata

per realizzare l’nmos dista meno di 2.6 um dalla nwell. Tuttavia questa regola impone la

minima distanza tra NDIFF e HOT_NTUB ma la nostra nwell è considerata una HOT_NTUB

solo perchè ancora non abbiamo inserito la label che identifica la VDD. Tuttavia esisterà

una regola simile anche per una NTUB non HOT ma la minima distanza sarà meno

ristrettiva.

MINIMUM DENSITY OF ... -> Tutti i messaggi relativi alla minima densità dei vari livelli di

metal possono essere al momento ignorati in quanto non rappresentano una violazione di

16 Febbraio 2016

Massimo Barbaro e Roberto Puddu

8

regole di design. Avere una determinata percentuale di utilizzazione di tutti i livelli di metal

garantisce in fase di realizzazione del dispositivo una migliore riprodubilità. Tuttavia questi

livelli possono essere raggiunti in ultima istanza per mezzo di strutture dummy.

ERC WARNING: floating ... -> Questa regola ci avvisa della presenza di alcune piste

flottanti. Per eliminare questo WARNING sarà sufficiente inserire una label per ognuno dei

pin del componente.

ERC WARNING: Latchup rule LAT3 distance s/d diff ngate

net_subtap > 20 ->

Questa regola ci dice che la massima distanza tra i contatti di drain e source e il substrato

deve essere inferiore a 20 um per evitare problemi di latchup.

Per visualizzare l’area del layout corrispondente ad un dato errore è possibile una volta

evidenziato l’errore nella parte sinistra della finestra “Erorr Layer Window” cliccare sulla

freccia evidenziata in rosso nella Figura sottostante. A questo punto nella finestra contente

il layout verrà evidenziata l’area corrsipondente all’errore.

Per risolvere i problemi evidenziati dal DRC allarghiamo la nwell in modo che si estenda

oltre la nwell per almeno 0.2 um. Aggiungiamo poi analogamente a quanto fatto per i contatti

della nwell i contatti di substrato che questa volta saranno di tipo PD_C. Il risultato finale

dovrebbe essere quello mostrato nella Figura sottostante. Questo dovrebbe aver risolto gli

errori BAD_SUBSTR_SUBTAP_FLOAT_ERC e OD_C_1 Minimum NTUB enclosure of

NDIFF = 0.2. Gli altri errori come detto precedentemente potranno essere risolti soltanto

16 Febbraio 2016

Massimo Barbaro e Roberto Puddu

9

successivamente alla definizione delle porte del componente in modo da indicare le

connessioni di massa e alimentazione e i terminali di ingresso e uscita.

5. Assegnamento delle porte

Daremo ora il nome ai terminali del dispositivo. L’inverter ha 4 terminali (VDD, VSS, vin e

vout). E’ possibile inserire una porta dal menu

Create -> Label

definendo poi i parametri della porta attraverso la finestra che comparirà a schermo

16 Febbraio 2016

Massimo Barbaro e Roberto Puddu

10

E’ necessario specificare il nome della porta e il layer corrispondente al contatto che si vuole

realizzare. Il layer da utilizzare per i vari livelli di metal inizia sempre con la dicitura PIN e

contiene poi l’indicazione del livello di metal da utilizzare. Nel nostro caso dovendo

contattare delle porte realizzate con il metal 1 il layer da utilizzare sarà PIN metal 1. Una

volta definiti i parametri si può cliccare “Hide” per andare a piazzare la label sopra il terminale

che si vuole contattare. Aggiungiamo quindi i terminali “vin”, “vout” e poi le due tensioni di

alimentazione. Per la tensione di alimentazione la label da utilizzare sarà “vdd!” mentre

utilizzeremo la label “gnd!” per la massa. E’ fondamentale che le label scelte per definire le

porte nel layout abbiano i medesimi nomi assegnati alle porte nello schematico in modo tale

che quando andremo a effettuare la verifica di corrsipondenza tra layout e schematico (LVS)

i nomi coincidano.

Una volta definite tutte le porte si dovrebbe avere una situazione equivalente a quella

riportata in Figura. Se si effettuasse un DRC a questo punto tutti gli errori dovrebbero essere

stati risolti

16 Febbraio 2016

Massimo Barbaro e Roberto Puddu

11

6. Verifica LVS

Per verificare la corrsipondenza tra il layout realizzato e lo schematico del circuito:

Assura -> Run LVS

16 Febbraio 2016

Massimo Barbaro e Roberto Puddu

12

Si aprirà la finestra mostrata sopra e cliccando OK si farà partire l’LVS. Una volta terminato

una finestra riporterà l’esito della comparazione indicando eventualmente gli errori. Nel

nostro caso quello che otteniamo è il messaggio di errore mostrato in Figura.

Cliccando OK si aprirà poi il “Debug Environment” dal quale è possibile ricavare informazioni

più dettagliate sulla tipologia dell’errore

16 Febbraio 2016

Massimo Barbaro e Roberto Puddu

13

Andando poi ad aprire i vari tool “Devices, Nets, Rewires” è possibile identificare l’errore.

Nel nostro caso l’errore consiste nel non aver connesso i terminali di source dei due

transistor ai contatti di source e alimentazione rispettivamente per l’nmos e il pmos.

Risolviamo il problema creando la connessione e rilanciamo l’LVS che questa volta

dovrebbe terminare con la seguente schermata

che ci informa che lo schematico e il layout coincidono.

16 Febbraio 2016

Massimo Barbaro e Roberto Puddu

14

7. Estrazione capacità parassite

Per avere l’estrazione di tutte le capacità parassite per prima cosa è necessario effettuare

un LVS dopo aver selezionato dalla schermata delle impostazione lo switch “resimulate

extracted” come mostrato in Figura

Una volta terminato LVS selezionare

16 Febbraio 2016

Massimo Barbaro e Roberto Puddu

15

Assura -> Run Quantus QRC

e si aprirà la schermata mostrata sotto. L’unica cosa da definire risulta essere nella Tab

“Extraction” il nodo di riferimento che andrà impostato uguale al terminale di massa, cioè

“gnd!”

A questo punto una volta cliccato OK avrà avvio il processo di estrazione dei parassiti che

terminerà con la creazione automatica di una nuova view del componente chiamata

“av_extracted” e questa sarà la view da utilizzare ogni qual volta si vorranno effettuare delle

simulazioni post-layout che includono cioè gli effetti parassiti. Aprendo la view si aprirà una

sorta di layout in cui sono presenti anche tutti i componenti parassiti

16 Febbraio 2016

Massimo Barbaro e Roberto Puddu

16

7. Simulazione Post-Layout

La simulazione si effettua in modo simile alla simulazione circuitale normale, servirà quindi

un testbench in cui istanziare il simbolo dell’inverter da simulare e inserire i generatori di

segnale. Il testbench conterrà in questo caso solo due generatori: il generatore di tensione

di alimentazione per generare la VDD e il generatore di segnale che fornisce la tensione di

ingresso. Trattandosi di un circuito digitale useremo uno stimolo digitale, quindi una forma

ad onda quadra che generi sequenza di 1 (vin=VDD) e 0 (vin=0). Il generatore è disponibile

nella analogLib e si chiama vpulse. I parametri da fornire al pulse sono la tensione iniziale

(0), la tensione dell’impulso (VDD), il periodo, la durata dell’impulso, il tempo di salita e

discesa e il ritardo iniziale. Metteremo ad esempio il periodo a 4ns, la durata dell’impulso a

2ns (duty cycle 50%), il ritardo iniziale a 2ns e i tempi di salita e discesa a 1ps, in modo che

siano trascurabili.

Questa è la form per la scelta dei parametri del pulse:

16 Febbraio 2016

Massimo Barbaro e Roberto Puddu

17

Il circuito finale avrà l’aspetto in figura:

Della cella inverter abbiamo a disposizione 2 view simulabili, quella originale con il solo

circuito (schematic) e quella ottenuta a partire dal layout tramite l’estrazione dei componenti

parassiti (av_extracted). Dobbiamo quindi potere simulare (utilizzando il solito tool ADE)

scegliendo una di queste view al momento della simulazione. Ini questo esempio proveremo

anche a confrontare direttamente le prestazioni ideali dello schematico con le prestazioni

16 Febbraio 2016

Massimo Barbaro e Roberto Puddu

18

del circuito post-layout quindi dobbiamo potere definire per alcune parti del circuito l’uso

della view schematic e per altre della view av_extracted. Modifichiamo lo schematico

inserendo 2 diversi percorsi per il segnale:

I componenti DUT1 e LOAD saranno simulati usando l’estratto post-layout mentre i

componenti DUT2 e LOAD2 saranno simulati usando lo schematico originale. Per fare

questo dobbiamo creare una nuova view del testbench che possa essere usata per

descrivere la gerarchia dei componenti e decidere, per ogni componente, quale tipo di view

utilizzare. Questo tipo di view si chiama config. Creeremo quindi una nuova cellview per la

cella di testbench (che si chiama tb_inverter) di tipo config.

Creando il config compare una finestra come questa:

16 Febbraio 2016

Massimo Barbaro e Roberto Puddu

19

Cliccando su “Use Template” si può scegliere uno dei template per popolare i campi del

form, noi faremo una simulazione analogica quindi utilizzeremo il template “spectre” che

modificheremo come in figura aggiungendo la view “av_extracted” fra quelle disponibili nella

View List (in prima posizione). A questo punto cliccando su OK si ottiene la form in figura:

Di default la form si apre con la Tab “Table View” in evidenza ma noi selezioneremo la tab

“Tree View” che ci consente di decidere per ciascuno dei componenti quale view utilizzare.

Adesso, cliccando con il tasto destro su uno dei componenti della gerarchia possiamo

scegliere quale view utilizzare. Avendo messo “av_extracted” come primo elemento della

View List di default ci viene proposta tale view ma si può optare, sottocircuito per

sottocircuito, per una scelta diversa. In questo caso, come detto precedentemente, useremo

la view dell’estratto per DUT1 e LOAD e la view schematico per DUT2 e LOAD2. Dalla figura

si vede come la view estratto contiene più componenti perché ci sono tutte le capacità

parassite che mancano nello schematico.

16 Febbraio 2016

Massimo Barbaro e Roberto Puddu

20

A questo punto aggiorniamo e salviamo e possiamo passare alla simulazione. Lanceremo

ADE L dalla view config anzi che dalla view schematic come siamo abituati a fare.

Selezioneremo una simulazione in transitorio che dovrà durare almeno alcuni periodi della

forma d’onda di ingresso. Il risultato è quello in figura:

Come si vede, i tempi di propagazione ottenuti per la view estratto sono leggermente più

lunghi dei tempi di propagazione dello schematico proprio perché tengono conto delle

capacità parassite presenti nel layout.

16 Febbraio 2016

Massimo Barbaro e Roberto Puddu

21