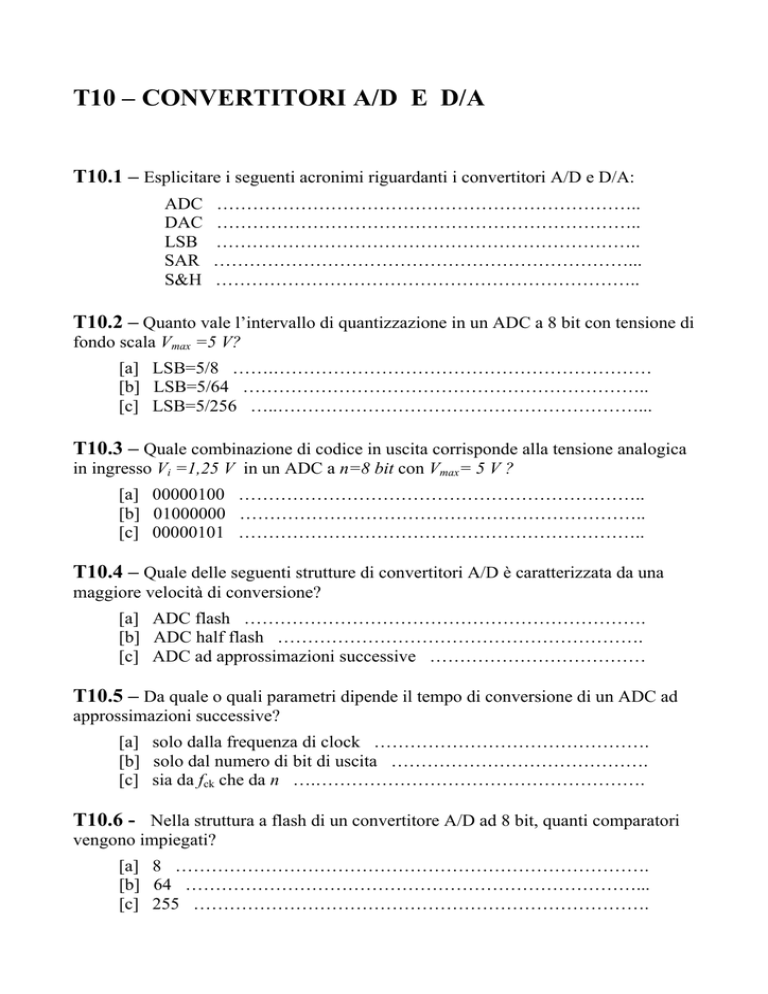

T10 – CONVERTITORI A/D E D/A

T10.1 – Esplicitare i seguenti acronimi riguardanti i convertitori A/D e D/A:

ADC

DAC

LSB

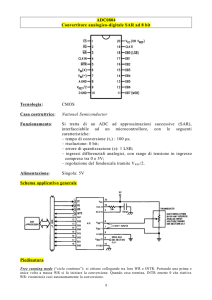

SAR

S&H

……………………………………………………………..

……………………………………………………………..

……………………………………………………………..

……………………………………………………………...

……………………………………………………………..

T10.2 – Quanto vale l’intervallo di quantizzazione in un ADC a 8 bit con tensione di

fondo scala Vmax =5 V?

[a] LSB=5/8 …….………………………………………………………

[b] LSB=5/64 …………………………………………………………..

[c] LSB=5/256 …..……………………………………………………...

T10.3 – Quale combinazione di codice in uscita corrisponde alla tensione analogica

in ingresso Vi =1,25 V in un ADC a n=8 bit con Vmax= 5 V ?

[a] 00000100 …………………………………………………………..

[b] 01000000 …………………………………………………………..

[c] 00000101 …………………………………………………………..

T10.4 – Quale delle seguenti strutture di convertitori A/D è caratterizzata da una

maggiore velocità di conversione?

[a] ADC flash ………………………………………………………….

[b] ADC half flash …………………………………………………….

[c] ADC ad approssimazioni successive ………………………………

T10.5 – Da quale o quali parametri dipende il tempo di conversione di un ADC ad

approssimazioni successive?

[a] solo dalla frequenza di clock ……………………………………….

[b] solo dal numero di bit di uscita …………………………………….

[c] sia da fck che da n ….……………………………………………….

T10.6 - Nella struttura a flash di un convertitore A/D ad 8 bit, quanti comparatori

vengono impiegati?

[a] 8 …………………………………………………………………….

[b] 64 …………………………………………………………………...

[c] 255 ………………………………………………………………….

T10.7 – In un ADC a 8 bit, quanti comparatori sono necessari se si adotta una

struttura half-flash?

[a] 4 …………………………………………………………………….

[b] 16 …………………………………………………………………...

[c] 30 …………………………………………………………………...

T10.8 – Quanto può valere il tempo di conversione di un tipico ADC flash?

[a] 1 ms …………………………………………………………………

[b] > 10 µs ……………………………………………………………...

[c] < 100 ns …………………………………………………………….

T10.9 – Calcolare la massima frequenza di un segnale analogico accettabile da un

ADC a 8 bit, privo di circuito S&H, avente un tempo di conversione Ts=10µs.

…………………………………..…………………………………………….

T10.10 – Il circuito S&H (Sample and Hold, campiona e mantieni) impiega come

elemento di memoria:

[a] un condensatore ………..…………………………………………...]

[b] un flip-flop JK ……………….……………………………………..

[c] uno registro parallelo ………………...……………………………...

T10.11 – Dove si può impiegare il circuito S&H ?

[a] a monte di un ADC ……………………………………………..

[b] a valle di un DAC ………………………………………………

[c] in entrambi i casi ……………………………………………….

T10.12 – Qual è la minima frequenza di campionamento per la conversione A/D di

un segnale analogico in banda fonica 300÷3400 Hz ?

[a] 300 Hz …………………………………………………………..

[b] 3400 Hz …………………………………………………………

[c] 6800 Hz …………………………………………………………

T10.13 – La struttura a rete R-2R dei convertitori D/A (con gli interruttori

elettronici che collegano i resistori 2R alla massa del circuito o alla massa virtuale

dell’AO) è caratterizzata da:

[a] una elevata risoluzione ……………………………………………....

[b] un basso tempo di assestamento ……………………………………..

[c] una bassa velocità di risposta ………………………………………..

T10.14 – I convertitori D/A a moltiplicazione (multiplying DAC) eseguono il

prodotto fra:

[a] due segnali analogici ………………………………………………..

[b] un segnale analogico ed un numero binario ………………………...

[c] due numeri binari …………………………………………………...

T10.15 – Indicare se le seguenti affermazioni riguardanti i convertitori A/D e D/A

sono Vere o False:

a) La rapidità di conversione SPS (Samples Per Second) di un ADC coincide con

l’inverso del tempo di conversione Ts.

[V] ………………………………………………………………………….

[F] …………………………………………………………………………

b) Un convertitore A/D flash a n bit richiede n cicli di clock per generare la

combinazione di codice in uscita.

[V] ………………………………………………………………………….

[F] ………………………………………………………………………….

c) La struttura dei convertitori A/D ad approssimazioni successive comprende

anche un convertitore D/A.

[V] ……………………………………………………………………….

[F] ……………………………………………………………………….

d) In un DAC la tensione di uscita è proporzionale al valore numerico espresso

dal codice di ingresso.

[V] ……………………………………………………………………….

[F] ………………………………………………………………………..

e) In un dac la tensione di uscita può assumere qualunque valore compreso fra 0

e Vmax.

[V] ……………………………………………………………………….

[F] ………………………………………………………………………..

f) L’errore di offset di un DAC altera la pendenza della caratteristica di

trasferimento.

[V] ………………………………………………………………………..

[F] ………………………………………………………………………..

g) I glitch sono impulsi di breve durata che si producono all’uscita di un DAC

negli istanti di commutazione del codice di ingresso.

[V] ………………………………………………………………………..

[F] ………………………………………………………………………..

h) Per convertire in digitale un segnale analogico a due componenti armoniche

f1=1 kHz, f2=2 kHz, è possibile adottare una frequenza di campionamento di

3 kHz.

[V] …………………………………………………………………………

[F] ………………………………………………………………………….

Risposte

T10.1 – ADC = Analog to Digital Converter

DAC = Digital to Analog Converter

LSB = Least Significant Bit

SAR = Successive Approximation Register

S&H = Sample and Hold

T10.2- [a] Si ha: 1 LSB = Vmax/2n = 5/28 = 5/256.

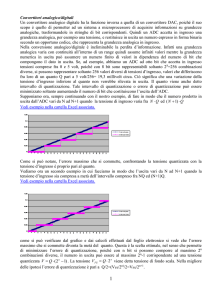

T10.3 – [b] Il codice di uscita esprime in binario il numero di intervalli di quantizzazione

contenuti nella tensione d’ingresso. Quindi:

Vi

V ⋅ 2n 1,25 × 256

= i

=

= 64 = (01000000) 2

LSB Vmax

5

T10.4 – [a] Il funzionamento in parallelo degli ADC flash consente di ridurre fortemente il tempo

di conversione, rispetto ai convertitori ad approssimazioni successive. La variante half-flashi

semplifica la struttura, ma aumenta il tempo di conversione.

T10.5 – [c] La serie di approssimazioni successive impegna n cicli di clock, per cui, detto Ts il

tempo di conversione e Tck il periodo di clock, si ha: Ts=nTck.

T10.6 - [c] Occorrono tanti comparatori quanti sono i (2n-1) livelli di tensione prelevati dalla

tensione di riferimento mediante il partitore resistivo. Nel nostro caso: (28-1) = 256-1 = 255.

T10.7 - [c] Con due ADC flash a 4 bit ciascuno, il numero di comparatori risulta: 2ּ(24-1) = 30.

T10.8 - [c] Gli ADC flash funzionano secondo il metodo della comparazione diretta o in

parallelo, che consente di ottenere una velocità di risposta molto elevata.

T10.9 - Oltre che da Ts, la fmax dipende dal numero n di bit in uscita. Si applica la (18.4):

f <

1

2 πTs

n

=

1

= 124 Hz.

2 π 10 − 5

8

T10.10 - [a] Il circuito S&H costituisce una memoria analogica basata sulla carica di un

condensatore alla tensione che si vuole mantenere cotante durante il tempo intercorrente tra due

campionamenti successivi.

T10.11 - [c] In un ADC con tensione d’ingresso variabile, il circuito S&H evita errori di

conversione durante il tempo di conversione Ts. In un DAC il circuito S&H evita i glitch (impulsi di

breve durata che si sovrappongono all’uscita analogica negli istanti di commutazione dell’ingresso

digitale) durante il tempo di assestamento Ta.

T10.12 - [c] Per rispettare il limite di Shannon (18.5), deve essere:

f c ≥ 2 f max = 2 × 3400 = 6800 Hz

In pratica si adotta una f c = 8 kHz.

T10.13 - [b] Il valore di Ta può essere molto piccolo perché la circolazione delle correnti rimane

praticamente invariata al variare del codice in ingresso, e quindi non si hanno limitazioni dovute a

menomi transitori nelle capacità parassite del circuito.

T10.14 - [b] L’uscita di un multiplying DAC è proporzionale al prodotto tra la tensione analogica

Vr applicata all’ingresso di riferimento ed il valore decimale della combinazione di codice in

ingresso.

T10.15 – a) [F] Generalmente si ha SPS < 1 / Ts [ s ] perché tra due successive conversioni è

richiesto un tempo di attesa per il ripristino del circuito.

b) [F] Gli A/D flash operano in parallelo, confrontando la Vi con 2n tensioni di soglia.

A seguito del confronto un encode genera il codice binario di uscita.

c) [V] Gli ADC ad approssimazioni successive sono formati essenzialmente da un

registro SAR, un DAC ed un comparatore.

d) [V] Fissato il valore di n (numero di bit del codice) e di Vr (tensione di riferimento),

tra il valore numumerico N della combinazione di codice in ingresso e la tensione analogica in

uscita Vu sussiste la relazione:

Vu =

Vr

N.

2n

e) [F] Per un DAC ad n bit la Vu può assumere solo valori multipli di

1 LSB =

Vmax

2 n −1

f) [F] L’errore di offset (= tensione costante che si somma alla tensione analogica in

uscita) fa spostare parallelamente a se stessa la caratteristica ideale di trasferimento (= insieme

discreto di punti allineati su una stessa retta).

g) [V] I glitch sono impulsi di breve durata che si producono all’uscita dei DAC negli

istanti di commutazione del codice d’ingresso.

h) [F] La frequenza di campionamento non può essere inferiore alla frequenza limite

di Shannon: fmin =2 f2 = 6 kHz.

_____________________