ESERCIZIO 12

Si simuli in transitorio un ringo oscillator in logica CMOS statica a 5 stadi. Si

assume VDD=3.3 V ed i transistori a dimensioni minime (2/0.8). In particolare, si

valutino la frequenza di oscillazione ed il ritardo di ciascuno stadio, e si confronti

quest’ultimo con quello di un inverter con fan-out unitario (v. esercizio n. 5). Si

commentino eventuali differenze tra i due risultati.

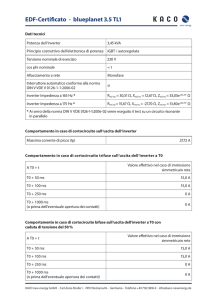

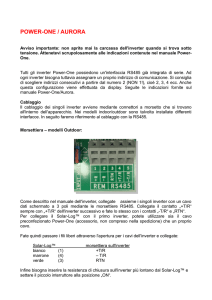

Si consideri un ring oscillator a 5 stadi, il cui disegno è di seguito riportato:

M2

M4

M6

0A

Mbreakp

Mbreakp

M8

Mbreakp

M10

0A

Mbreakp

Mbreakp

3.3Vdc

1.554V

M1

1.554V

M3

0A

Mbreakn

Mbreakn

1.554V

M5

1.554V

M7

0A

Mbreakn

M9

V

0A

Mbreakn

Mbreakn

0V

0

0

0

V1

0

0

0

1.554V

Come è noto, un ring oscillator presenta un solo punto di equilibrio, che è quello in

cui tutte le tensioni di ingresso e di uscita sono pari alla soglia logica dell’inverter.

Da un’analisi in DC, come mostrato dalla figura precedente, tale tensione è pari a

1.554 V. Tale punto di equilibrio è certamente instabile, pertanto ci si attende che il

circuito oscilli immediatamente. Tuttavia, l’oscillazione inizia solo se lo stato del

circuito è perturbato rispetto al punto di equilibrio, ed in assenza di sollecitazioni le

tensioni ai nodi di ingresso e di uscita degli inverter rimangono inalterate. Per

questa ragione, anche una simulazione in transitorio mostra un andamento costante

dell’uscita del quinto inverter:

In un circuito reale, sarebbero certamente presenti delle sollecitazioni che

determinano l’inizio dell’oscillazione, tra le quali si ricordano il rumore generato

dai dispositivi e dai circuiti adiacenti.

Per simulare un ring oscillator ed osservare l’oscillazione, è necessario

introdurre una sollecitazione che allontani il circuito dal punto di equilibrio. Tale

considerazione vale per qualunque circuito che abbia almeno un punto di equilibrio

instabile, come discusso più in dettaglio nell’ipertesto a proposito dei problemi di

simulazione in transitorio.

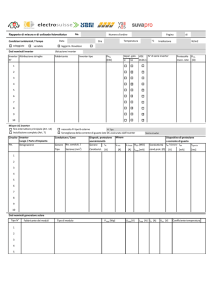

Una possibile maniera per introdurre una sollecitazione è quello di inserire un

generatore di corrente lineare a tratti, che generi inizialmente una corrente di entità

comparabile con quella dei transistori (dell’ordine delle centinaia di µA), e che

successivamente generi una corrente nulla, in modo da non perturbare

ulteriormente il funzionamento dell’oscillatore. Inoltre, affinchè abbia effetto,

l’impulso di corrente deve avere una durata sufficiente, almeno dell’ordine del

ritardo di ciascun inverter (in questo caso di un centinaio di ps, come visto

nell’esercizio n. 5). Pertanto, il circuito da simulare diventa:

M2

M4

M6

0A

Mbreakp

Mbreakp

M8

Mbreakp

M10

0A

Mbreakp

Mbreakp

3.3Vdc

1.554V

M1

1.547V

1.761V

M3

M5

0A

Mbreakn

Mbreakn

M7

0A

Mbreakn

M9

V

0A

Mbreakn

Mbreakn

0V

0

0

0

0

0

0

1.554V

100.0uA

I1

0

Il generatore di corrente IPWL deve essere impostato secondo i seguenti parametri:

T1=0

T2=100p

T3=10n

I1=100u

I2=0

I3=0

dove la corrente iniziale è pari a I1=100 µA, la durata dell’impulso è pari a T2=

100 ps, e per gli istanti di tempo successivi la corrente è pari a I3=0 A. Infatti,

come noto, i generatori lineari a tratti (PieceWise Linear) interpolano in maniera

lineare i valori I1,I2, … che sono stabiliti in corrispondenza degli istanti di tempo

T1, T2, …

La simulazione in transitorio per visualizzare la forma d’onda dell’oscillazione

deve comprendere un discreto numero di periodi, per dare modo al circuito di

raggiungere il regime. Come noto, il periodo di oscillazione Tosc di un ring

oscillator ad n stadi è pari a

Tosc=2n⋅τPD

V1

193.8mV

(12.1)

dove τPD rappresenta il ritardo di propagazione (pari alla media aritmetica dei

valori relativi ai transitori basso-alto e alto-basso) di ciascuno stadio. In particolare,

tale ritardo coincide con quello di un inverter con fan-out unitario. Dato che tale

ritardo (v. esercizio n.5) è dell’ordine del centinaio di ps, il periodo di oscillazione

atteso è dell’ordine del ns. Per visualizzare una decina di periodi, impostiamo a 10

ns la durata della simulazione

La forma d’onda di uscita che si rileva all’uscita di un qualunque inverter è

riportata di seguito:

Il periodo Tosc rilevato mediante il cursore (definito come l’intervallo di tempo tra

due attraversamenti successivi del valore VDD/2=1.65 V) è pari a 1.52 ns. Tale

valore conduce ad un ritardo di propagazione per stadio di 152 ns, dalla (12.1).

Tuttavia, il valore ricavato nell’esercizio n. 5 risulta pari alla media aritmetica tra

116.9 ps e 74.6 ps, che è di 95.7 ps. Tale valore risulta sensibilmente inferiore a

quello di ciascuno stadio del ring oscillator, nonostante ciascuno di questi sia

circuitalmente identico all’inverter dell’esercizio n. 5 e sia caricato in maniera

identica. L’unica differenza risiede nella forma d’onda della tensione di ingresso

dell’inverter, che nell’esercizio n. 5 era praticamente un gradino, mentre nel ring

oscillator è una forma d’onda che varia meno bruscamente.

Per comprendere l’effetto di una forma d’onda d’ingresso che varia più

lentamente sul ritardo di propagazione, si consideri il transitorio di scarica da parte

del transistore NMOS. Applicando un ingresso che varii in maniera più lenta di un

gradino ideale, nella fase iniziale del transitorio la VGS dell’NMOS non raggiunge

istantaneamente il valore VDD, e la corrente generata dall’NMOS è quindi inferiore

a quella che si avrebbe con ingresso a gradino. Pertanto, ci si attende che il ritardo

di propagazione sia maggiore di quello con ingresso a gradino. Analoghe

considerazioni valgono per il PMOS durante il transitorio di carica. Tali

osservazioni giustificano la difformità tra il ritardo di propagazione di ciascuno

stadio del ring oscillator e quello di un inverter identico con ingresso a gradino.