ESERCIZIO 17

Si simuli una cella SRAM a 6 transistori nella fase di scrittura, assumendo che la

capacità di bitline CBL sia di 1 pF e la tensione di alimentazione sia di 3.3 V. In

particolare, dopo aver generato gli opportuni segnali di precarica e di attivazione

della wordline, si valuti il ritardo di propagazione assumendo che i transistori della

cella siano di dimensioni minime ed i PMOS che effettuano la precarica delle

bitline abbiano dimensioni 20/0.8.

Il circuito da simulare è il seguente

V10

3.3Vdc

0

WL

WL

M4

M2

M8

precharge

Mbreakp

Mbreakp

M3

V

C1

Mbreakp

M1

C3

M5

V

M6

0.0001p

Mbreakn

Mbreakn

0

C2

0

1p

1p

0

0

0

0

0

0

V6

precharge

WL

V5

0

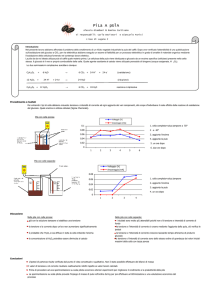

dove le bitline sono schematizzate mediante due capacità equivalenti CBL che

modellizzano la capacità parassita di ciascuna bitline e delle celle ad essa collegate.

In fase di scrittura, le bitline sono precaricate a valori differenti, quella a sinistra

al valore di 0 V (impostando IC a 0 V nella capacità C1), e quella a destra al valore

di 3.3 V mediante il transistore PMOS M8 pilotatato dal segnale precharge. Tale

segnale deve essere mantenuto al valore basso durante la precarica, e

successivamente deve passare al valore alto per consentire la lettura. Tanto per

fissare le idee, imponiamo che il tempo disponibile alla precarica sia di 50 ns (in

pratica i tempi consentiti sono considerevolmente più bassi). La forma d’onda del

segnale precharge è illustrata mediante la curva in blu nella figura seguente:

Per effettuare la scrittura, è necessario attivare i transistori M5-M6 imponendo che

la tensione della wordline WL effettui la transizione basso-alto dopo la fase di

precarica. Supponiamo che tale transizione avvenga all’istante t=100 ns, come

illustrato mediante la curva in verde nella figura precedente.

Prima della attivazione della wordline, la cella SRAM è isolata rispetto alle

bitline, e la coppia di inverter mantiene la tensione memorizzata in precedenza. Se

il valore memorizzato precedentemente è uguale al valore che deve essere scritto

nella cella, la scrittura è caratterizzata da un ritardo nullo. Il caso più significativo è

quello in cui il valore da scrivere è opposto a quello memorizzato precedentemente.

Per questo motivo, si impone che la tensione di gate di M3-M4 sia bassa (inserendo

la capacità fittizia C3, come spiegato nell’esercizio n.16) inizialmente.

A causa della transizione dei segnali di precarica e di WL, e del fatto che le

capacità CBL sono piuttosto elevate, le tensioni di bitline permangono ai valori di 0

V e 3.3 V, rispettivamente. Successivamente, a causa dell’attivazione della

wordline, le tensioni della cella SRAM vengono aggiornate. Più esplicitamente, la

capacità C1 (carica a 0 V) impone che la tensione di gate di M3-M4 si porti allo

stesso valore di 0 V, mentre la capacità C2 (carica a 3.3 V) impone che la tensione

di gate di M1-M2 si porti al valore di 3.3 V. In altri termini, come desiderato, viene

scritto nella cella SRAM un valore differente da quello memorizzato in

precedenza.

Il transitorio delle tensioni della cella SRAM (ovvero le tensioni di gate di M3M4 e di M1-M2) è descritto nella seguente figura

Dall’analisi di questa figura, si deduce che il ritardo di propagazione in scrittura,

ovvero il tempo necessario affinchè la tensione di gate di M1-M2 e di M3-M4

abbianona tensione pari a VDD/2, è pari a 218 ps. Ciò conferma che la fase di

scrittura nella cella SRAM richiede un intervallo di tempo molto breve, e in pratica

la velocità dell’intera operazione è limitata dalla precarica della bitline, oltre che

dalle consuete operazioni di decodifica.