Consig[io 9\[pziona[e de[[e ricercne

ISTITu-ro DI ELABORAZIONE

DELLA INFORMAZIONE

PISA

Contratto di collaborazione Tecnico-Scientifica

Centro Leonardo Spa-IEl/CNR

Scheda

LeonardC25-02. Descrizione

realizzazione

della

G. Bertini, A. Landucci,M. Moretto, A. Moretto

Nota tecnica B4-58 novembre '92

Contratto di collaborazione Tecnico-Scientifica

Centro Leonardo Spa-IEI/CNR

Scheda

LeonardC25-02.

Descrizione

della

realizzazione

G. Bertini, A. Landucci, M. Moretto, A. Moretto

Nota tecnica B4-58 novembre '92

l

Indice

In trod uzione

l)

Descrizione scheda LeonardC25, schema del circuito e criteri per

il progetto del PCB.

2)

Realizzazione del PCB.

a) inserimento di componenti mancanti In libreria.

b) Posizionamento dei componenti

c) programma di sbroglio.

d) controllo e completamento dei layer.

e) specifiche per il fotoplottaggio e per gli stampati.

3)

Montaggio prototipi e test hardware.

4)

Bibliografia

4)

Appendici

A - Schema elettrico

B - .Pinout componenti aggiunti.

C - Layout degli stampati

D - Squadretta di sostegno

2

Introduzione

Nell'ambito di una collaborazione dell'lEI (Reparto di Elaborazione Segnali ed

Immagini e Laboratorio Elettronico) e il Centro Leonardo Spa sono stati realizzati

alcuni prototipi di schede per PC IBM compatibili, per l'elaborazione digitale di

segnali in tempo reale basati sul TMS320C25, un microprocessore di tipo DSP della

Texas Instruments, descritti nella nota tecnica (1).

Successivamente la suddetta societa, che è titolare del Progetto ARIETE (abbattimento

di rumori acustici con tecniche di controllo attivo), ha stipulato con l'lEI un contratto

di collaborazione tecnico-scientifica e di ricerca nel quale uno dei temi riguarda per

l'appunto il progetto e lo sviluppo di strumentazione utilizzabili per lo studio e la

sperimentazione d.i tecniche di controllo attivo del rumore. Nell'ambito di tale lavoro

è stato deciso di mettere a punto una versione opportunamente modificata e

migliorata della scheda a cui è stata attribuita la sigla LeonardC25-02: il progetto e le

caratteristiche funzionali di quest'ultima versione sono riportate in (2)

In questa nota vengono descritti i particolari realizzativi della versione LeonardC2502 per quello che riguarda lo schema elettrico il progetto del PCB e altri dettagli

costruttivi dei prototipi ingegnerizzati.

3

l)

Schema del circuito e specifiche di progetto del peB.

Dopo aver effettuato diverse esperienze con i due prototipi di schede descritte

in (1) é stato deciso di ingegnerizzare un modulo definitivo prendendo come base uno

di questi, la LeonardC25/D, ampliandone però le prestazioni specie per consentire il

trattamento di segnali analogici di varia provenienza sia col convertitore a bordo,

che con altri tipi di convertitori.

In particolare le modifiche introdotte sono le seguenti:

-un circuito di condizionamento in ampiezza, con guadagno programmabile via

software, sui due canali analogici di ingresso del convertitore A/D e D/A (TLC32040

sempre della Texas) montato internamente sulla scheda.

-un circuito di commutazione comandato via software che consente di connettere la

porta seriale del TMS320C25 al convertitore interno

oppure, tramite un connettore,

all'esterno della scheda.

-la possibilità di inviare delle richieste di interrupt verso il PC.

-la possibilità di utlizzare dall'esterno un certo numero di segnali di controllo in

ingresso ed in uscita del TMS320C25, selezionabili via software e con dei ponticelli.

-introduzione di microswicth sugli indirizzi di selezione della scheda da parte del PC

per poterne gestire comodamente fino ad un massimo di otto.

Alcune di queste parti aggiunte sono state realizzate prima con dei circuiti a

wire-wrap e testate opportunamente in laboratorio collaudo dell'IEI dai progettisti;

dopodiché le varianti sono state riportate nel disegno elettrico riportato in appendice.

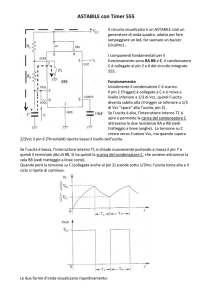

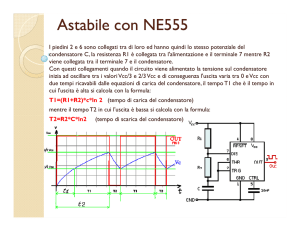

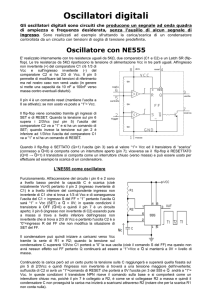

I componenti pricipali del modulo visibili sia nello schema a blocchi di fig. 1.

La descrizione dettagliata del funzionamento delle varie parti del sistema è

riportata in (2); per comodità riportiamo qui una breve descrizione delle parti

principali del modulo:

-Microprocessore TMS320C25 (3): è un dispositivo programmabile con un set di

istruzioni adatte all'elaborazione digitale di segnali in tempo reale, con precisione di

16bit, è molto diffuso in ambito telecomunicazioni (modem, cellulari, ecc.); funziona

con un oscillatore a 40Mhz, esegue la maggior parte delle istruzioni con un tempo di

ciclo di 100ns (impulso di strobe di 50ns) e possiede una porta seriale ad alta velociui

per il colloquio con altri dispositvi, tipicamente con moduli di conversione A/D e D/A

oppure con altri moduli DSP.

- un banco di memoria di 64 Kbyte (32 kwords) allocata nello spazio programma del

micro, così suddivisa: una sezione di 4Kwords eprom contiene il firmware

(monitor,

tabelle, ecc.) ed una sezione di Ram di 28 Kwords viene utilizzata per allocare

programmi e per bufferizzare dati. Le memorie Ram sono state implementate con i

chip MC6206 della Motorola (32kbyte per ogni chip, 28 pin DIP) e le memorie eprom

57C43B della Waferscale (4kbyte per ogni chip, 24 pin DIP), entrambe disponibili con

tempi di accesso tali da non richiedere cicli di wait-states.

un'interfaccia parallela di comunicazione bidirezionale con l'elaboratore ospite.

Essendo compatibile con i modelli XT, il bus dati del PC è a 8 bit; il bus dati del TMS è

invece a 16 bit, di conseguenza le operazioni da parte del PC vengono eseguite in due

tempi.

una rete composta da latches e buffers che permette la commutazione dei

collegamenti della porta seriale del TMS320C25 sul convertitore interno TLC32040

oppure verso l'esterno della scheda. La commutazione avviene tramite una

operazione di I/O del micro ed é specificabile ovviamente con appositi comandi

software inviati dall'elaboratore ospite al momento della configurazione iniziale od in

qualsiasi altro momento.

- una porta seriale esterna: la scheda può comunicare con dispositivi esterni tramite

un collegamento bidirezionale a 5 Mbit/s, che permette l'implementazione del

protocollo seriale offerto dal microprocessore. Sui collegamenti dell'interfaccia

sono

interposti dei buffers per provvedere al disaccoppiamento elettrico del TMS con il

mondo esterno, realizzato tramite un connettore di tipo Canon a 15 poli.

4

BusPC-IBM

4 KWord

EPROM

I

Masler

Rese!

--"-~...!>..

I'-.,-:>'

I

I

I

Parallel

..-

110

Dala Bus

PC

16/

.....

RDlr

y

/16 li' 16

j~

AdJ2 + AdIS

*

IM!;k

BIO\

III

2,

t~

~cz:

&

,

1OW\

I

IIRQi~

~

Ao + Ad!'

,

l'

J

Masler

.Rese!

/Y, T!\lS

--

r=

2/

Power

J/

...

l'

XF

Breakers

INTEXT

INTl\

Enable

--{>

.;;

YJI

Y1I

7

/

Dala Bus

7

Buffers

.;--{:'

Control

&

Switch

Enable

~

110

TMS

Ex! Serial Bus •

4/

7

I<l-

7

Serial Bus'

>

/

Serial Bus'

~

Yo

Y, PC

j-12

Rese!

,..

f-F

12

7

ìerial Bus' 8

IS\

,

RD\

WR\

Control

Logic

- ...

7

/

3/

1ii~

Memory

Selection

XF "

Y 4 TMS

:!f:::;;

1OR\

STRB\

~

~c

Switch

fo

TMS320C25

INT2_~

M

...

WR\

~

AJ + Ag

Ao + Al

PS\

I r j- r

S

~

~/L

DS\

Canon

15 pin

S

4

Address Bus

~

lLfL:

Card

Selection

1~

ft

/

\

I

I

12

V

,

--P

I

16

~e

16

Dala Bus

AEN\

I

I

28 KWord

P-RAM

Enable

~6 ~

ftTMs

WR\

r.

Converter

TLCJ2040

/44/46

AlD & D/A

I<J-

~

gIN

ux IN

~

og

Analog OUT

t>

Reset

CircuiI

RCA

JACK

Masler Resel

I Y 6, Y7

I

~

Progammable

GainAmp

INTPC

Breakers

I

I

I

I

I

I

I

I

I,

• TI DSPs Serial Bus

I

Leonard C25 - ReI. 02

1Fig_ l Schema a blocchi dcI modulo Lconard C25 ~Ol

- il convertitore integrato TLC32040 già citato; su tale chip sono implementati oltre

alle parti di conversione vere e proprie anche gli opportuni circuiti di filtraggio

passa basso (vedi manuali Texas).

- una sezione di condizionamento in ampiezza sui segnali di ingresso, realizzata con

amplificatori operazionali a guadagno controllabile a scatti via software, sempre

tramite una operazione di I/O del TMS.

La scheda è provvista di due ingressi ed una uscita analogica su prese RCA, più

altri collegamenti disponibili sui poli del connettore Canon, utilizzabili in diverso

modo tramite brackers, per alcuni segnali di controllo da e verso il TMS.

Per quanto riguarda la realizzazione pratica del circuito, l'uso di ram statiche e

di eproms ad accesso veloce ha permesso di evitare circuiti di wait states snellendo

così la logica di controllo. In base alla relativa semplicita delle reti di decodifica e

assieme ad altre valutazioni, per questa versione è stato deciso di non utilizzare

dispositivi PLD. L'implementazione delle reti di logica e degli altri componenti è stata

fatta con integrati della serie TTL FAST o FACT ed LS dove è necessario raggiungere

una elevata velocita, negli altri casi sono utilizzati dispositivi della serie HC o HCT.

L'assorbimento della scheda LeonardC25, con tutti i banchi di memoria completi

è di circa 500 mA sul +5 v fornito dal Bus del PC.

In base a valutazioni delle frequenze di lavoro, della complessita' e del numero

dei componenti del sistema ed in base all'esperienza delle precedenti realizzazioni e'

stato deciso di impostare il lavoro distribuendo i collegamenti sui due strati esterni

(lato componenti e lato saldatura), cercando di non introdurre piste sugli strati

interni riservati alla massa e alla tensione; tale obiettivo consente di raggiungere un

buon compromesso fra un ottima schermatura e il costo degli stampati.

Una richiesta ulteriore fatta dai progettisti è quella di riuscire ad avere una

densità dei componenti

maggiore rispetto a quella della LeonardC25/D.

2) Realizzazione del PCB

Il progetto del circuito stampato e' stato fatto con l'ausilio del sistema P-CAD

corredato di un plotter HP DraftPro DXL Mod 7575A in dotazione al laboratorio

elettronico dell'lEI. Si elencano di seguito i passi con i quali normalmente viene

sviluppato un progetto di circuito stampato:

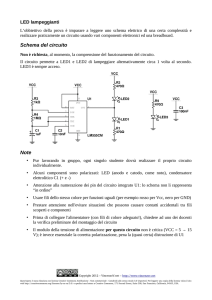

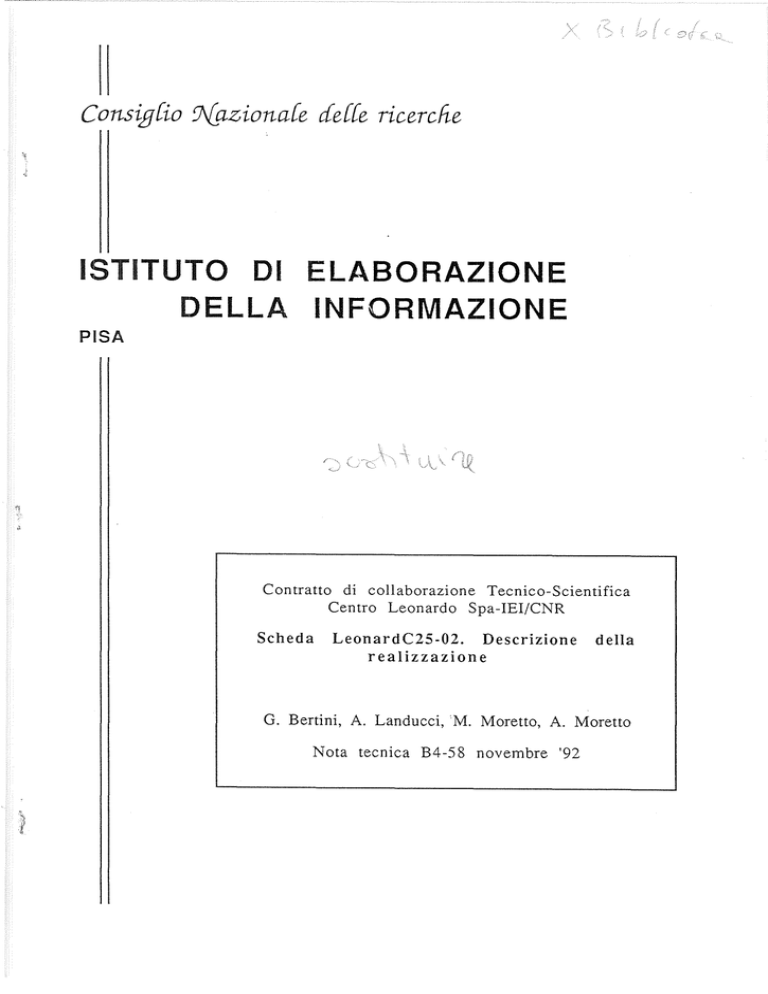

a) la prima operazione da fare è quella di controllare che tutti i componenti del

circuito siano presenti nella libreria del P-CADo Nel nostro caso sono mancanti il

TMS320C25, il TLC32040 le ram MC6206 versione slim, prese RCA ecc ..

Di tali componenti sono stati rilevati dai rispettivi manuali le dimensioni fisiche

e le sigle associate ai pin (abbreviazioni della funzione espletata); dopodichè questi

sono stati inseriti a far parte della libreria stessa (vedi app B).

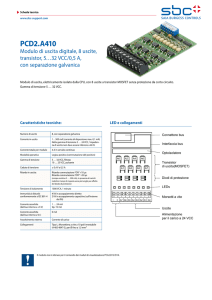

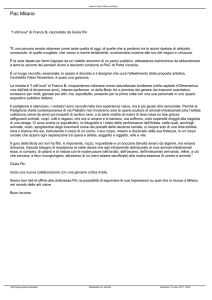

b) Il posizionamento dei componenti può essere fatto eseguire automaticamente

al P-CAD oppure manualmente; nel nostro caso in base alle funzioni svolte da alcuni

componenti e in base ai tipi di segnali da connettere con l'esterno della scheda si è

ritenuto necessario eseguire manualmente tale operazione; il risultato finale è stato

raggiunto ovviamente dopo varie prove tese ad ottimizzare i diversi aspetti del

problema (vedi Fig. 2).

Per quanto riguarda i tratti di pista da tracciare a mano

nel nostro caso sono

molto limitati, essendo unicamente costituiti dalle tensioni +5, -5, +12, -12 provenienti

dal bus del PC e da un tratto di massa, cosiddetta analogica, intorno al TLC32040 e alle

prese RCA.

Un particolare da tener presente è quello di provare con un fac-simile delle

dimensioni previste della scheda negli alloggiamenti di Personal di diverse ditte,

5

onde evitare errori per quanto riguarda la centratura dei connettori e delle prese

RCA nelle apposite finestre disponibili nel retro del rack e per il posizionamento

della squadretta metallica necessar.ia al fissaggio della scheda stessa sul telaio del PC.

c) dopodichè viene lanciato il programma di sbroglio vero e proprio, la durata

del quale dipende ovviamente dal tipo di personal computer impiegato e dagli

algoritmi a disposizione nel sistema di CAD. Nel nostro caso con le dimensioni imposte

della scheda (25x10 cm), nonostante l'impiego dell'algoritmo di RIP-PAP il sistema

non è riuscito a completare il 100 % del lavoro, bensì sono rimaste da stendere ina

quindicina di piste. Dopo aver esaminato la situazione si è deciso di posizionare tali

piste sullo strato interno riservato inizialmente alla sola tensione +5. Dopo aver

completato la stesura delle piste si è definito lo strato della tensione come un

reticolato con maglia di 1mm x 1mm, anzichè come uno strato omogeneo: tale

accorgimento consente un risparmio nel costo del fotoplottaggio senza peraltro

diminuire l'efficacia della schermatura.

d) Riassumendo alla fine del lavoro si sono ottenuti quattro strati così utilizzati:

-uno strato esterno con le piste (lato componenti);

-un primo strato interno per la massa, senza nessuna pista;

-un secondo strato interno per la tensione di alimentazione con un limitato

numero di piste;

-uno strato esterno per le piste (lato saldatura).

Sullo strato interno di massa ci sono definite solo le corone per i contatti sui fori

passanti; l'assenza di piste su di uno strato viene opportunamente sfruttata per avere

un costo minimo di fotoplottatura dello strato sulla relativa pellicole.

Facciamo infine osservare che, rispetto al disegno elettrico del circuito in

oggetto, sono stati insenti i condensatori di filtro VICInO alle tensioni di

alimentazione dei chip e sono stati aggiunti e distribuiti, dove ritenuto necessario, dei

cosiddetti "punti di prova" che tramite la saldatura

di pin, consentono l'ancoraggio

delle sonde degli oscolloscopi ecc .. Tali punti sono etichettati con sigle

opportune,

(segnali BIO\, Reset\, CLKOU1\, ecc.).

e) l'ultima operazione da. fare per poter predisporre l'esecuzione del circuito

stampato presso ditte esterne. specializzate in questo tipo di realizzazioni, è la

preparazione dei dischetti dei file Gerber, o altro formato richiesto, contenente tutte

le informazioni per la fotoplottatura dei layout degli sbrogliati sulle pellicole. Altre

specifiche da fornire, necessarie. per la costruzione degli stampati, sono lo spessore

della scheda, il tipo di supporto, il grado di isolamento, il tipo di trattamento (sold

resist

), serigrafia, doratura eventuale dei connettori, il controllo visivo o elettrico

degli stampati,

Le dimensioni della scheda Leonard C25-02 ottenute sono di 25 x lO cm (è chiaro

che dimensioni più piccole si potrebbero ottenere facendo il PCB con più di quattro

strati, in tal caso aumenta però)i costo degli stampati ), lo spessore dello stampato è

quello standard richiesto dal bus I?C IBM cioe di 1,6 mm ed il connettore e' dorato. Per

la connessione del bus seriale del TMS320C25 verso l'esterno e' stato impiegato un

connettore a 15 contatti di tipo Cannon, di norma utilizzato da schede PC IBM.

In app. C) sono riportati i layer corrispondenti ai vari strati della scheda

Leonard C25-02.

I prototipi delle sbarrette metalliche per il fissaggio sui cabinet sono stati

preparati nell'officina dell'lEI mentre a quelle definitive ha provveduto la Leonardo

facendole costruire da una ditta esterna (vedere in app. D

particolari della

squadretta).

6

cs

O

CI

o

Cl

U24

ft;n

c'u

lI3

U2

U?

+1-.

et

U6

PUH

'-{38

U5

JPI

I

...

'-l'

li 17

PO

D

D-d-

8~!x

(1

PF

D

Ul

~

4-

SWI .

U9

UlO

Ull

Ul2

'52-1

otfXI X)

8

RI

P)

1

U14

0000 Il~l

P2

PI PS Ali

o

Il

Cl

I

)I

7)

Montaggio prototipi e test hardware.

Una volta ottenuti gli stampati ed avere eseguito un controllo della lavorazione,

sono stati montati un paio di prototipi impiegando zoccoli per alloggiare tutti i chip

del circuito. Per la rilevazione di errori e anomalie di funzionamento ci siamo avvalsi

di un generatore di forme d'onda, un oscilloscopio analogico Tektronics 2465B

400Mhz e un Logic Analyzer HP 16500 100Mhz, 80 canali. Quest'ultimo strumento, in

mancanza di emulatore, si dimostra essenziale per la ricerca degli errori di progetto

del PCB e di quelli di montaggio dei componenti; le modalità di utilizzo sono già state

indicate nella (1).

Per eseguire le prove iniziali della scheda è stata approntata e caricata sulla

Eprom una versione del monitor con alcune particolarità studiate appositamente per

facilitare il controllo delle funzioni di base del sistema ad esempio la trasmissione e la

ricezione di dati tra PC e la scheda. Inoltre sono stati inseriti nell'archivio dell'Editor

e quindi richiamabili a piacere, alcuni programmi di ausilio per la verifica del

corretto funzionamento della scheda: ad es. invio e lettura di costanti, programmi di

generazione di particolari forme d'onda. Alcuni di questi programmi sono riportati

nella già citata nota tecnica (1); altri programmi di utilità e applicativi saranno

raccolti in una apposita nota tecnica (3).

Attraverso vari controlli sono stati rilevati alcuni errori che in un circuito

complesso come quello in oggetto è quasi impossibile evitare. Sono stati corretti di

conseguenza i layer e ordinata di nuovo l'esecuzione degli stampati.

E' stato infine verificato il corretto funzionamento di un paio di prototipi relativi agli

stampati definitivi anche su diversi tipi di personal compatibili IBM: dopodichè il

lavoro di realizzazione hardware si può considerare concluso.

7

9) Bibliografia

1) Bertini G., Landucci A., Marani M.,: Moduli di acquIsIzIOne ed elaborazione di

segnali in tempo reale LeonardC25-01: descrizione della realizzazione dei prototipi",

nota tecnica B4-43, Dic '91.

2) Bertini G.:"Progetto, funzionamento e prestazioni dei moduli LeonardC25-02"

Contratto di collaborazione tecnico-scientifica Leonardo Spa-IEI/CNR, nota interna

lEI B4-57, nov. '92.

3) TMS 320C25 U ser's Guide, Texas Instruments, 1989

4) P-CAD User's Guide

8

Appendici

9

------_.

---,...P EPROM

UI

U2

U3

U9

U5

RB

A7

R34

CI2

,\1 i!~

J6

..'

P2

>--'''''--:,..,...:;;; I

P3

C4+

R9

UI6

U24

..

'

C 2.5'. 02

APP. sci)

MECHANICAL DATA

68-pin GB pin grid array ceramic package

TOP VIEW

28.448 11 . 1 2 0 ) = 0

27.432 (1.080)

1,

117.0~6~670)t

THERMAL RESISTANCE CHARACTERISTICS

- - 1 8 . 4 4 8 (1.120)

PARAMETER

ROJA

J une tion ·to·t ree·air

thermal resistanee

RUJC

Junetion·to·case

thermal resistanee

MAX

UNIT

36

°C/W

6

°C/W

27.432 Il.080)

17.02 (0.670)

'------J_~

4.953 (0.1951 M A X t T I

\

3.302 (0.1301

2.794 (0.1101

I

~-~

I

r] ]] ~ ~ ~ ffi-~t

~

1.397 (0.0551

(0.0201

L.,[- 0.508

0.508 (O 0201-110.406 (0.016)

1.575 (0.062) DIA

1.473 (0.058)

2,5410.1001-r---1

BOTTOM VIEW

T.P.

1""+-1_1,'--__._________-.

L

K

J

IOGGGGGGG8-t

00G G

G G

G

G

G

G

G 0 8 · - t 2 , 5 4 10.1001

G G

T.P.

HGG

GG

GGG

GG

FGG

GG

EGG

GG

DGG

GG

C G

B

A

G

G

t'f'::'I.

0

G

G

G

G

G

G

G

G

G

0)

GG

=i

1 ,524 (0.060)

NOM

4 PLACES

GGGGGGGG8-J..

2

3

4

56

7

8

91011 L1,27 (0.0501

NOM

ALL LlNEAR DIMENSIONS ARE IN MILLIMETERS AND PARENTHETICALL Y IN INCHES .

Printed in U.S.A.

SPRZ039

9 8

VSS

07

06

05

04

03

02

01

DO

SYNC

INTO

INn

INT2

VCC

DR

FSR

AO

7 6 5 4 3 2

lO

16867666564636261

60

11

12

59

58

57

13

14

56

55

54

15

16

17

18

53

52

51

50

49

48

47

19

20

21

22

23

24

25

46

45

26

44

2728293031323334353637383940414243

IACK

MSC

CLKoUTl

CLKOUT2

XF

H5Ti5A

OX

FSX

X2/CLKIN

Xl

BR

STRB

R/W

PS

iS

OS

VSS

~~NM~~~~U~~O~NM~~

~~~~~~~~~~~~~~~~~

Figure 2-2. TMS320C25 Pin Assignments

PIN ASSIGNMENTS

PIN

PIN

FUNCTION

PIN

A2

FUNCTION

08

CII

CLKOUT 1

J10

FUNCTION

PS

PIN GRIO ARRAY CERAMIC PACKAGE I

A3

010

01

04

Jll

iS

(TOP VIEWI

A4

02

03

Kl

AO

A5

012

014 '

010

CLKOUT2

K2

Al

A6

MP/MC

011

XF

K3

A3

A

A7

HOLD

El

02

K4

A5

B

A8

RS

E2

01

K5

A7

A9

CLKX

EIO

ROL5A

K6

A8

AIO

VCC

ElI

OX

K7

AIO

D

BI

VSS

07

F1

DO

K8

A12

E

82

F2

SYNC

K9

A14

83

09

FIO

FSX

K10

QS

F

B-l

011

fIl

X2/CLKIN

K 11

VSS

G

85

013

Gl

INTO

L2'

015

G2

INTI

L3

VSS

A2

H

86

B7

BIO

GIO

Xl

L4

A4

J

08

REAOY

GlI

aH

L5

A6

K

B9

CLKR

1\1

INT2

L6

L

ilIO

VCC

112

VCC

L7

VCC

MI

1111

IACR

1110

~rnii

lO

Ali

Cl

06

III 1

H/W

19

AI:l

C2

\)5

.11

\)/\

L Hl

A15

CIO

MSC

-- . . .P.

rSR

-'

6B·PIN GB

2

C

3

4

5

6

7

8

9

lO 11

• • • • • • • • •

,,-,

•

• (~ • • • • • • • tè'

• •

• •

• •

• •

• •

• •

• •

• •

• •

• •

• •

• •

• •

• •

re,

(!;

•

•

•

• • • • •

•

• • • • • • • • •

,~

t Sce Pln Assignmenls Table (Pogo II end Pin Nomenclelure Table

(Pago 21 lor locallon and dascripllon 01 ali pins.

JjJ'

TEXAS

{ INSTRUMENTS

SPRZ039

TlL 320 ~O jlti

FN PACKAGE

ITOP VIEWl

N PACKAGE

ITOP VIEWl

55 J8

NU

EODA

FSA

DR

MSTR CLK

4

:::> :::> :::> +

3

2

1 28 27 26

'DR

5

25

MSTA CLK

6

24

23

VOD

OUT+

OUT-

VDD

REF

DGTL GND

SHIFT CLK

l§

1U-UJa:zzz!!;

i"iESET

VCC+

VCCANLG GND

ANLG GND

NU

-<..._-,...,- NU

INAUX IN+

AUX IN":

REF

B

22

DGTL GND

SHIFT CLK

EODX

9

21

OUT+

OUT-

10

11

20

19

VCC+

VCC-

121314151617 18

:::>:::> Cl Cl

XI~IX

Cl>-~ zz z z

<.:J <.:J

<.:J <.:J

-' -'

cc

è5

a:

o

zz

<:<:

~

NU - Nonusable; no external connection should be made

to these pins.

Terminai Assignments

N PACKAGE

(TOPVIEW)

t FSD/WORO-BYTE

RESET

t0110UT/EOOR

FSR

DR

MSTRCLK

VDO

REF

OGTLGND

SHIFTCLK

t0100UT/EOOX

OX

tOATA-OR/CONTROL

FSX

FN PACKAGE

(TOPVIEW)

NU

NU

IN+

INAUXIN+

AUXINOUT+

OUTVCC+

VCC_

ANLG GNO

ANLG GNO

NU

NU

l

~

O

UJ

i==

UJ

~o

a::

O

'. (/) Ci5\tiil~

a:: ~ (/) (/)

UJ L.L.:::l :::l +

L.L. .... a:: .... z z:1!:

l

4 321 282726

25

6

24

7

23

8

22

9

5

lO

11

19

121314 1516 1718

x

-'r

Cl O(/)

a::L.L.

z zz z

<.:J

O

9

9

z z

Q

a::

O

VCC+

VCC-

:::l :::lO O

f-

Z

OUT+

OUT-

~

C)

<:

~

~

E

NU - Nonusable; no external connection should be made IO Ihese pins.

t The portion of Ihe pin name IO Ihe left of Ihe slash is used for Ihe TELEPHONE INTERFACE mode. The portion of

Ihe pin name to Ihe righI of Ihe slash is used 10r WORD-BYTE mode.

MCM6206C

PIN ASSIGNMENT

A14

VCC

W

BLOCK DIAGRAM

A13

AO

A8

VCC

A3

A9

VSS

All

A4

A6

A?

G

MEMORY MATRIX

256 ROWS x

128 x 8 COLUMNS

ROW

DECODER

A8

A9

Al1

000 .

A2

AlO

Al

E

AO

DO?

000

006

001

005

002

004

VSS

003

COLUMN 110

INPUT

DATA

CONTROL

COLUMN DECODER

Al

A2

PIN NAMES

AO-A14 .............. Address Input

DOO-DO? .... Data InpuVData Output

W .................... Write Enable

G .................... Output Enable

E ...................... Chip Enable

VCC .......... Power Supply (+ 5 V)

VSS ....................... Ground

A5 AlO A12 A13 A14

6

.

10

....., -1-t

-- .-

r-t-

-~--_

.._..

~

@

]1

\O

----,

\O

".,

I

~

PRESA ReA A 90 0

MONTAGGIO:

c.s.

ottone

ISOLAMENTO:,'

bachelite

ADATTA PER SPINE 4/20004/1970-4/2014

conpo:

•

••_________o~~

• D

o

••________

o

~

o

o

OD

~.~~.~O~,----.

.

\

o

o

O

•

•

-

000,.000·00000

•

•O

•

•

•

a

o

.:jq.

o .

o

o

Il

o

O

o

~

o

o

O

o

O

O

O

t""

:x>'

.....

O

()

O

iB