CNR-ISSIA u.o.s. di Palermo

Istituto di Studi sui Sistemi Intelligenti per l'Automazione

Via Dante, 12 - 90141 Palermo (Italy)

Tel. +39 091 6113513 Fax +39 091 6113028

Rapporto tecnico n. 413 anno 2011

Risultato di valorizzazione applicativa:

implementazione su piattaforma FPGA di un controllore per inverter trifase

con tensione del DC-link regolabile per azionamenti elettrici automotive

Autori:

M. C. Di Piazza, M. Luna, G. Vitale

“Esemplare fuori commercio per il deposito legale agli effetti della Legge 15 aprile 2004, n. 106”

Gli autori sono i soli responsabili del contenuto di questo rapporto tecnico

Data di creazione: 22 giugno 2011

Prima distribuzione al pubblico e deposito legale: 18 luglio 2011

C.F. 80054330586

P.I. 02118311006

Sede legale: Via G. Amendola 122/D-I – 70126 Bari (Italy) Tel. +39 080 5929429 Fax +39 080 5929460

INDICE

Introduzione ....................................................................................................................................... 3

1. Il controllo a V/f costante............................................................................................................... 4

1.1 Richiami sul controllo scalare .......................................................................................... 4

1.2 Implementazione nell’inverter SINUS/IFDE-F 400T-5.5kW Elettronica Santerno........ 5

2. Specifiche e componenti del sistema realizzato............................................................................. 7

2.1 Specifiche del sistema ...................................................................................................... 7

2.2 Kit didattico Semikron Semiteach ................................................................................... 8

2.3 Schede Altera Cyclone III FPGA e Nial Stewart GPIB................................................... 9

2.4 Scheda SSD .................................................................................................................... 10

2.5 Altri componenti ............................................................................................................ 10

3. Implementazione del sistema di controllo ................................................................................... 11

4. Procedura di messa in servizio..................................................................................................... 15

4.1 Esecuzione dei collegamenti elettrici............................................................................. 15

4.2 Modifica dei parametri e ricompilazione ....................................................................... 16

4.3 Programmazione............................................................................................................. 17

4.4 Stand-by, avviamento, marcia e arresto; visualizzazione display SSD.......................... 17

4.5 Reset ............................................................................................................................... 17

Conclusioni e sviluppi futuri............................................................................................................ 18

Riferimenti bibliografici .................................................................................................................. 19

Appendice A .................................................................................................................................... 20

Appendice B..................................................................................................................................... 22

All rights reserved. Part of this paper may be reproduced with the authorization of the authors and quoting the source.

Tutti i diritti riservati. Parti di questo rapporto possono essere riprodotte previa autorizzazione citando la fonte.

Rapporto Tecnico RT – ISSIA – PA – N. 413 – 2011

2

INTRODUZIONE

Oggetto del lavoro è stata l’implementazione su piattaforma FPGA di un inverter completo

con tensione del DC-link regolabile esternamente, per il controllo V/f di motori asincroni trifase a

bassa tensione di alimentazione, da integrare al banco di prova su filtri automotivi già esistente

all’interno del laboratorio Interferenze Elettromagnetiche Condotte e Power Quality in dotazione

all’ISSIA-CNR u.o.s. di Palermo. Tale intervento era stato già prospettato nel rapporto tecnico

n. 407 [1].

La necessità di tale realizzazione scaturisce dall’esigenza di verificare le prestazioni di filtri

attivi EMI per la soppressione di disturbi di modo comune su motori asincroni trifase per uso in

ambito automotive, con tensione nominale pari a 42 V, secondo lo schema riportato in fig. 1 [2].

Pur disponendo, infatti, di inverter commerciali di varia marca, non risulta possibile utilizzarli, in

quanto essi presentano una tensione minima di uscita non inferiore a 50 V.

Si è deciso, pertanto, di replicare le principali funzionalità di un inverter commerciale su un

nuovo sistema che non presenti restrizioni sulla tensione minima di uscita in modo che, regolando

opportunamente la tensione del DC-link fornita da un alimentatore esterno ed aggiornando

conseguentemente uno specifico parametro dell’inverter configurabile dall’utente, sia possibile

alimentare sia motori automotive, sia motori per azionamenti industriali.

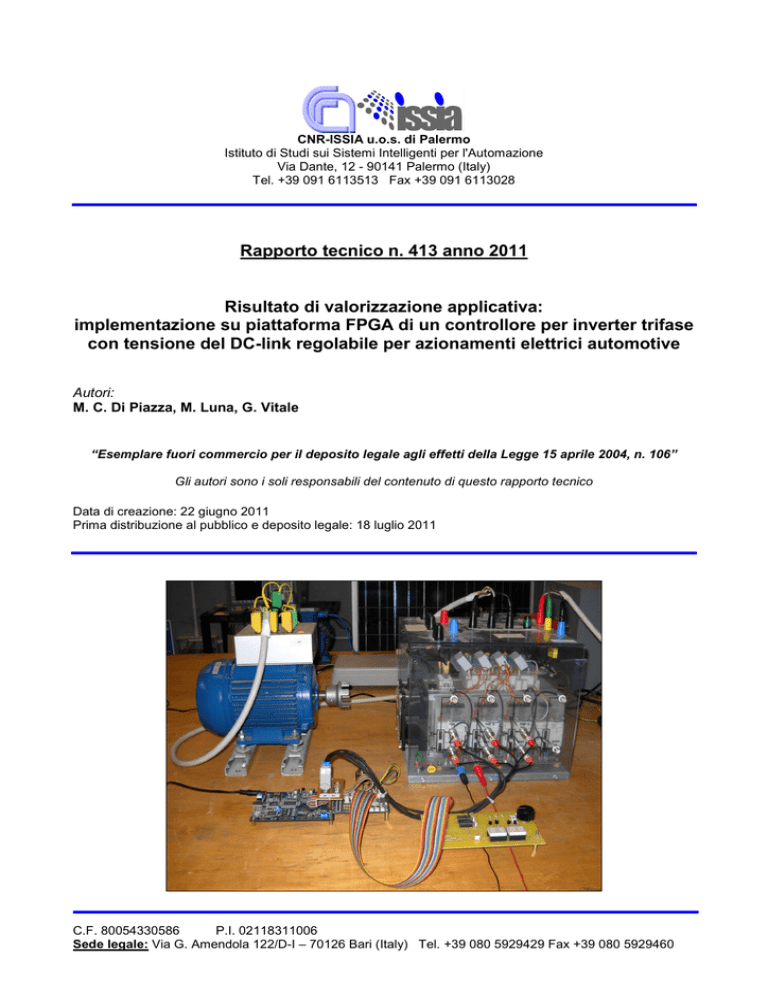

Il sistema è costituito principalmente per la sezione di potenza da un kit didattico Semikron e

per l’implementazione dell’algoritmo di controllo da una scheda FPGA della Altera. Quest’ultima

costituisce una piattaforma digitale a basso costo ed elevate prestazioni, che consente di

implementare una vasta gamma di progetti, dai più semplici a quelli multimediali. Essa è stata

opportunamente programmata in linguaggio VHDL utilizzando anche alcuni dei componenti

precedentemente creati, validati e inseriti nella libreria ISSIA_package.vhd.

Il presente documento descrive i componenti e le funzionalità del sistema realizzato ed è

suddiviso nei seguenti capitoli.

L’introduzione inquadra la tematica affrontata e descrive brevemente l’obiettivo del progetto.

La tecnica di controllo V/f è richiamata nel primo capitolo, dove viene anche discussa la sua

implementazione negli inverter commerciali. Nel capitolo successivo sono presentate le specifiche

del sistema realizzato e la descrizione dei componenti hardware utilizzati.

Il capitolo 3 è dedicato alla descrizione dello schema di implementazione su FPGA, mentre il

capitolo successivo illustra la procedura di messa in servizio del sistema. Infine, vengono presentate

le conclusioni su quanto realizzato e la possibilità di sviluppi futuri.

Fig. 1. Schema di verifica di filtri EMI per la soppressione di disturbi di modo comune su motori a induzione

Rapporto Tecnico RT – ISSIA – PA – N. 413 – 2011

3

1. IL CONTROLLO A V/F COSTANTE

1.1 Richiami sul controllo scalare

Il controllo del motore asincrono può essere effettuato in modo semplice variando la

frequenza della tensione trifase di alimentazione [3]. In tal modo, infatti, la caratteristica meccanica

di tale macchina trasla orizzontalmente sul piano coppia-velocità, per cui è possibile variarne

l’intersezione con la caratteristica del carico meccanico resistente, cioè il punto di funzionamento.

Inoltre, l’alimentazione a frequenza variabile consente di risolvere anche i problemi che

caratterizzano il motore asincrono in fase di avviamento alla frequenza nominale: l’elevata corrente

di spunto e l’incapacità di inseguire il campo magnetico rotante in caso di elevata inerzia rotorica.

Tuttavia, per un funzionamento regolare del motore occorre che i valori di flusso Ψn,

corrente In e tensione Vn nominali non siano superati. In particolare, il flusso del campo magnetico

rotante Ψ all’interno di un motore asincrono è proporzionale al rapporto tra la tensione V e la

frequenza di alimentazione f. Pertanto, per fare in modo che la variazione di frequenza non influenzi

il flusso, occorre variare proporzionalmente anche la tensione di alimentazione, cioè mantenere il

rapporto V/f costante e pari al valore corrispondente al rapporto tra tensione nominale Vn e

frequenza nominale fn.

Il piccolo valore di scorrimento s che caratterizza il funzionamento del motore asincrono dà la

possibilità di un controllo accettabile anche ad anello aperto. L' errore di velocità dipende dal

carico: indicando con p il numero di coppie polari, la velocità impostata con il riferimento di

frequenza f è quella sincrona, ovvero n0 = 60 f p , ma la velocità effettiva sarà n = n0 ⋅ (1 − s ) , con s

dipendente dalla coppia resistente del carico. La precisione di regolazione è in questo modo di

qualche percento.

Se la frequenza supera il valore nominale, però, il flusso non può essere più mantenuto al

valore nominale perché si dovrebbe aumentare la tensione oltre il suo valore nominale. Il flusso

pertanto deve essere diminuito (deflussaggio). In questo caso si mantiene la tensione costante e pari

al suo valore nominale, pur aumentando la frequenza, senza però arrivare a valori troppo elevati.

Solitamente non ci si spinge oltre un valore fM pari a 1,5 volte la frequenza nominale. Per quanto

detto, il flusso rimane costante nella prima zona del campo di funzionamento e decresce in modo

inversamente proporzionale alla velocità nella seconda, come mostrato in fig. 2. Conseguentemente,

finché il flusso mantiene il valore nominale è possibile avere la coppia nominale; quando, invece, il

flusso diminuisce, anche la coppia continuativa erogabile dal motore necessariamente dovrà

diminuire.

Fig. 2. Caratteristica del controllo V/f

Rapporto Tecnico RT – ISSIA – PA – N. 413 – 2011

4

Mantenere il rapporto V/f costante è altrettanto inadeguato alle basse frequenze, perché ciò

non garantisce la costanza della coppia erogabile legata alla costanza del flusso. Infatti, la

proporzionalità del flusso rispetto al rapporto tensione/frequenza è accettabile finché la caduta di

tensione resistiva sugli avvolgimenti statorici è trascurabile. Ciò che occorre mantenere costante è,

in realtà, il rapporto tra la tensione applicata diminuita della caduta resistiva, e la frequenza.

Pertanto, a frequenze molto basse (ad es. inferiori a fs= f n 5 ) è indispensabile aumentare la tensione

applicata per contrastare l'indebolimento del flusso dovuto alla caduta ohmica; la tecnica è nota

come “low-speed voltage boosting” e il corrispondente valore di tensione Vs è detto tensione di

boost. In definitiva la relazione V/f è espressa dalla caratteristica mostrata in fig. 2.

Se le accelerazioni richieste all'azionamento non sono particolarmente gravose, come capita

per la maggior parte delle applicazioni, è sufficiente il tipo di controllo descritto, detto anche

controllo scalare in quanto modifica, oltre alla frequenza, il valore efficace della tensione, ma non

interviene attivamente sulla fase delle grandezze elettriche. Non si occupa, cioè, delle relazioni di

fase tra tensioni e correnti che si riflettono nella posizione relativa dei campi magnetici di statore e

di rotore, e che influenzano sensibilmente la coppia per elevati scorrimenti.

Quando, invece, le esigenze dinamiche diventano notevoli, il controllo scalare non è più

sufficiente e risulta necessario l’utilizzo del controllo vettoriale, in cui le variazioni della frequenza

e del valore efficace della corrente avvengono unitamente ad una variazione della fase, per poter

effettuare il controllo del flusso magnetico. Tale tipo di controllo, che consente prestazioni di alto

livello a fronte di un’implementazione di maggiore complessità, non risulta necessario per le

verifiche su filtri attivi EMI descritte nell’introduzione.

1.2 Implementazione nell’inverter SINUS/IFDE-F 400T-5.5kW Elettronica Santerno

Al fine di offrire una maggiore versatilità di funzionamento, negli inverter commerciali la

curva V/f viene implementata in modo leggermente diverso da quanto riportato in fig. 2. In

particolare nel seguito si farà riferimento all’inverter a controllo digitale SINUS/IFDE-F 400T5.5kW prodotto dalla ditta Elettronica Santerno [4], che è un inverter trifase per motori asincroni

fino a 5.5 kW (7.5 CV), con uscita 0÷460V a 0÷800 Hz, 9 kVA, 13 A, ed alimentazione

380÷460 V, 50÷60 Hz, 14.5 A.

Esso implementa la curva V/f riportata in fig. 3, che l’utente può adattare alle proprie esigenze

applicative modificando i parametri indicati dalle sigle C5÷C10.

Fig. 3. Curva V/f implementata nell’inverter Elettronica Santerno

Rapporto Tecnico RT – ISSIA – PA – N. 413 – 2011

5

E’ immediato comprendere che il punto che ha come coordinate la frequenza nominale

(parametro C5) e la tensione nominale del motore (C8) rappresenta il confine tra la zona di

funzionamento a flusso (e coppia) costante e quella a tensione (e potenza) costante, e che in

quest’ultima la frequenza possa essere innalzata fino al valore individuato dal parametro C6. E’

prevista la possibilità di applicare mediante il parametro C9 un boost positivo (per aumentare la

coppia di spunto) o anche negativo (per ridurre il consumo energetico a basso numero di giri, nel

caso di carico con coppia quadratica). La differenza principale rispetto alla curva in fig. 2 è che tale

boost non è limitato ai valori di frequenza inferiori ad 15 della frequenza nominale, ma va

diminuendo gradualmente man mano che la frequenza si avvicina al suo valore nominale.

Considerando la caratteristica di fig. 3, occorre notare che a frequenza nulla si avrebbe una

tensione non nulla (parametro C10), cioè si alimenterebbe la macchina con una tensione continua.

Pertanto, è prevista anche la possibilità di impostare una frequenza minima di funzionamento (C7).

Un’altra funzionalità offerta dal suddetto inverter è la possibilità di variare la frequenza della

portante della modulazione PWM tra un valore minimo (parametro C1) ed un massimo (C2), come

indicato in fig. 4; in tal modo è possibile realizzare una modulazione sincrona, in cui la frequenza

della portante è proporzionale alla frequenza di uscita, oppure asincrona, se la frequenza della

portante è costante. Abbassando la frequenza della portante aumentano le prestazioni del motore a

basso numero di giri, a scapito di una maggiore rumorosità.

I due valori di frequenza che delimitano il tratto a modulazione sincrona sono dati

rispettivamente da:

C1

C2

f1 =

e f2 =

,

C3

C3

dove C3 rappresenta il numero costante di impulsi generati in uscita in tale modalità di

funzionamento. Nei tratti a modulazione asincrona, invece, il numero di impulsi prodotti è variabile

e può essere calcolato mediante la relazione:

f

n p = CARRIER .

f

Fig. 4. Variazione della frequenza della portante PWM in funzione della frequenza di uscita

Rapporto Tecnico RT – ISSIA – PA – N. 413 – 2011

6

2. SPECIFICHE E COMPONENTI DEL SISTEMA REALIZZATO

2.1 Specifiche del sistema

La struttura del sistema realizzato nei laboratori del CNR-ISSIA prevede che la tensione del

DC-link VDC venga fornita da un alimentatore esterno e che il controllo software tenga in

considerazione il suo valore mediante un apposito parametro programmabile dall’utente. In tal

modo, diversamente dagli inverter commerciali, il sistema non presenta restrizioni sulla tensione

minima di uscita per cui, regolando opportunamente la tensione del DC-link, consente di alimentare

motori asincroni sia per uso automotive, sia per uso industriale. Pertanto, esso presenta una

maggiore versatilità di impiego rispetto alle soluzioni commerciali e si adatta maggiormente

all’utilizzo per prove di laboratorio, in condizioni operative non usuali.

Il sistema replica le principali funzionalità offerte dall’inverter Elettronica Santerno descritto

in precedenza e, in particolare, presenta le seguenti caratteristiche:

• completa configurabilità della curva V/f, conformemente alla fig. 3;

• variazione della frequenza della portante PWM in funzione della frequenza di uscita

(modulazione sincrona o asincrona), secondo la fig. 4;

• avvio e arresto mediante rampe di accelerazione e decelerazione con tempi configurabili,

che consentono di far variare gradualmente la frequenza anche in seguito ad improvvise

modifiche del riferimento;

• pulsanti START e STOP con indicazione a LED;

• pulsante RESET per la rapida disalimentazione del motore collegato;

• ingresso analogico per riferimento di frequenza con range 0÷5 V, che può essere fornito da

un potenziometro esterno o da un convertitore digitale-analogico comandato da computer;

• visualizzazione su display a 7 segmenti (SSD) delle seguenti informazioni: set-point di

frequenza, frequenza di uscita effettiva, tensione di uscita, indice di modulazione, frequenza

della portante, indicazione di blocco sovramodulazione, indicazione di overflow.

Il prototipo realizzato è stato collaudato positivamente ed ha consentito di alimentare un

motore asincrono per uso automotive da 1,1 kW con tensione nominale pari a 42 V per poter

realizzare le misure necessarie a verificare le prestazioni di un filtro attivo EMI oggetto di ricerca

[2]. Il sistema ha consentito l’avviamento del motore già a partire da un riferimento di frequenza

pari a 4 Hz ed un buon controllo della forma d’onda d’uscita. Pertanto, esso è stato integrato al

banco di prova su filtri automotivi già esistente all’interno del laboratorio Interferenze

Elettromagnetiche Condotte e Power Quality in dotazione all’ISSIA-CNR u.o.s. di Palermo.

I componenti del sistema sono riportati in tab. 1 e sono di seguito descritti. Una fotografia del

sistema realizzato, connesso al motore automotive a 42 V, è mostrata invece in fig. 5.

Quantità

1

1

1

1

1

1

Descrizione

Kit didattico Semikron Semiteach (raddrizzatore trifase a diodi + inverter

trifase a IGBT + chopper di frenatura)

Scheda di sviluppo Altera Cyclone III FPGA, con cavo di alimentazione e

cavo USB di programmazione

Scheda di espansione Nial Stewart GPIB

Scheda con display SSD e relativo cavo flat di collegamento

Cavo DB15-RCA a 6 uscite

Potenziometro lineare multigiri da 1 kΩ

Tab. 1. Componenti del sistema

Rapporto Tecnico RT – ISSIA – PA – N. 413 – 2011

7

Fig. 5. L’inverter V/f realizzato, collegato ad un motore automotive a 42 V

2.2 Kit didattico Semikron Semiteach

La sezione di potenza dell’inverter è stata realizzata mediante il kit didattico Semiteach della

Semikron, mostrato in fig. 6, il quale è costituito da un gruppo raddrizzatore trifase a diodi e da un

inverter trifase a IGBT con chopper di frenatura, racchiusi all’interno di un contenitore trasparente

in plexiglass. Esso è dotato di 12 connettori a banana o BNC che consentono di effettuare le

connessioni elettriche necessarie:

• per il collegamento di terra (connettore 0);

• per il collegamento agli ingressi (connettori 1, 2 e 3) e alle uscite (connettori 4) del

raddrizzatore trifase;

• per la connessione al DC-link (connettori 5);

• per la connessione al carico trifase (connettori 6);

• per l'invio degli impulsi di commutazione agli IGBT dell’inverter (connettori 7);

• per l'invio degli impulsi di commutazione all’IGBT del chopper (connettore 8);

• per i segnali di errore provenienti dai driver IGBT (connettori 9);

• per l’alimentazione dei driver IGBT (connettori 10, 11 e 12).

Il kit presenta i seguenti limiti in tensione e corrente: Irms=30 A e Vac/Vdc max=440/750 V;

ulteriori dati caratteristici sono riportati in tab. 2.

Il sistema proposto utilizza soltanto il modulo inverter del kit Semiteach, quindi richiede

soltanto i collegamenti ai connettori 5÷7 e 10÷12. Tale inverter è equipaggiato con tre moduli di

potenza SKM50GB123D, ciascuno comprendente una coppia di IGBT con i rispettivi diodi in

antiparallelo, comandati da altrettanti doppi driver SKHI22AR, che includono funzionalità di

implementazione del tempo morto, interblocco top-bottom, protezione da corto circuito, protezione

undervoltage, segnale di uscita ERROR di tipo latch e isolamento galvanico. In Appendice A sono

riportate le tabelle A.1, A.2 e A.3 con le caratteristiche del modulo di potenza SKM50GB123D e la

tabella A.4 con i parametri del driver SKHI22AR.

Rapporto Tecnico RT – ISSIA – PA – N. 413 – 2011

8

Fig. 6. Il kit didattico Semiteach della Semikron

Tab. 2. Caratteristiche del kit didattico Semiteach

2.3 Schede Altera Cyclone III FPGA e Nial Stewart GPIB

Per l’implementazione del sistema di controllo è stata scelta una scheda di sviluppo Altera

Cyclone III FPGA [5], mostrata in fig. 7, a sinistra. Essa ospita un FPGA Altera EP3C25F324

pilotato da un oscillatore a 50 MHz e presenta le seguenti caratteristiche principali:

• 25K elementi logici;

• 66 blocchi di memoria M9K (0.6 Mbits);

• quattro PLL;

• 214 porte di I/O.

La scheda è facilmente programmabile in linguaggio VHDL e rappresenta una piattaforma a

basso costo ed alte prestazioni che consente di implementare una vasta gamma di progetti, dai più

semplici a quelli multimediali. Le sue caratteristiche più importanti sono il basso consumo di

potenza, la disponibilità di memoria SSRAM ed EEPROM e l’espandibilità mediante il connettore

HSMC (High Speed Mezzanine Card), che consente la connessione di schede di espansione con

diverse funzionalità. Nel caso in esame è stato necessario collegare una scheda di espansione Nial

Stewart GPIB [6], dotata di diversi connettori di I/O con i relativi level-shifter per interconnettere

logica CMOS a 2.5V con logica CMOS a 3.3V e TTL, e di convertitori A/D e D/A a 10 bit con 8

canali ciascuno. Tale scheda di espansione è mostrata in fig. 7, a destra.

Fig. 7. Scheda Altera Cyclone III FPGA con la scheda di espansione Nial Stewart GPIB

Rapporto Tecnico RT – ISSIA – PA – N. 413 – 2011

9

Un ulteriore vantaggio della scheda Altera è costituito dal fatto che ospita a bordo anche il

programmatore USB-Blaster che, mediante connessione USB e protocollo JTAG, consente la

programmazione dell’FPGA. Per le fasi di scrittura e compilazione del codice, simulazione, debug e

programmazione del dispositivo è stato utilizzato il software Quartus II Web Edition, che

rappresenta un valido ambiente grafico di sviluppo fornito gratuitamente dalla Altera [7].

2.4 Scheda SSD

Si tratta di una scheda appositamente realizzata, che ospita a bordo un commutatore rotativo a

4 posizioni ed un display a 7 segmenti a 4 cifre (display SSD), come mostrato in fig. 8, nonché tutta

la circuiteria necessaria per il pilotaggio in multiplex.

Essa consente di visualizzare informazioni provenienti dalla scheda Altera, selezionandole

mediante il commutatore, e si collega allo zoccolo DIP24 della scheda Nial Stewart mediante un

apposito cavo flat a 26 poli in dotazione. In caso di overflow, il display visualizza “0.0.0.0.”. Il

LED di segno è utilizzato come indicatore di blocco sovramodulazione, come descritto nel

capitolo 3.

Fig. 8. Scheda per la visualizzazione su display SSD

2.5 Altri componenti

Il sistema comprende anche i seguenti componenti:

• un cavo DB15-RCA a 6 uscite, necessario per connettere la scheda Nial Stewart agli ingressi

di pilotaggio degli IGBT dell’inverter Semikron;

• un potenziometro lineare multigiri da 1 kΩ, da collegare all’ingresso ADC0 del convertitore

A/D a bordo della scheda Nial Stewart, necessario per impostare il riferimento di frequenza.

Rapporto Tecnico RT – ISSIA – PA – N. 413 – 2011

10

3. IMPLEMENTAZIONE DEL SISTEMA DI CONTROLLO

Il sistema di controllo dell’inverter proposto è stato realizzato programmando la scheda FPGA

Altera in linguaggio VHDL [8] all’interno dell’ambiente di sviluppo Quartus II Web Edition.

Come già fatto in altre occasioni, il codice è stato sviluppato con un’architettura modulare per

consentire di riutilizzare componenti software già messi a punto e di crearne altri per la specifica

applicazione. In questo caso sono stati creati due componenti per l’interfaccia utente

(UI_buttons_and_leds.vhd e UI_SSD_display.vhd) che sono stati connessi ad altri componenti

VHDL precedentemente validati, quali i modulatori PWM che implementano la tecnica nota come

symmetrical regular sampling [9], la look-up-table (LUT) per la generazione di una terna

simmetrica diretta di sinusoidi [10] e il componente che implementa le curve delle fig. 3 e 4 [11].

Dal momento che i numeri reali definiti dal linguaggio VHDL non sono sintetizzabili, è stato

scelto di lavorare in notazione a virgola fissa a 32 bit con segno, mediante l’applicazione di

opportuni fattori di scala che, per maggiore chiarezza, vengono indicati anche nel nome di ciascun

segnale.

Lo schema a blocchi relativo all’intero progetto è mostrato in fig. 9 e trova corrispondenza

nella struttura del file principale (inverter_V_f.vhd). Esso mostra i diversi componenti VHDL

utilizzati, le cui estensioni .vhd sono state omesse per sintesi.

Il processo inizia con la lettura, mediante il componente VHDL denominato AD7918, del

segnale ch_0 presente sul canale 0 dell’omonimo convertitore A/D [12], collegato al potenziometro

esterno per l’impostazione del riferimento di frequenza. Tale segnale, insieme al segnale ops_valid

che indica il termine del processo di conversione, viene processato dal blocco synch_inputs, che lo

sincronizza con la frequenza di lavoro del sistema e lo scala opportunamente per fornire il

riferimento di frequenza moltiplicato per dieci (segnale f_x10_ref). Questo viene elaborato dal

componente accel_and_decel_ramps della libreria ISSIA_package.vhd, che implementa le rampe di

accelerazione e decelerazione secondo la programmazione dell’utente e in base al valore del flag

ramp_up_down, opportunamente settato dal blocco UI_buttons_and leds in base allo stato dei

pulsanti START e STOP. Il segnale di uscita del blocco accel_and_decel_ramps rappresenta il

valore istantaneo della rampa di frequenza moltiplicato per dieci (segnale f_x10_ramp) e viene

processato dal componente principale (V_f_control), già presente in libreria, che implementa le

curve delle figure 3 e 4, fornendo i seguenti segnali:

1. il valore della frequenza d’uscita effettiva, moltiplicato per dieci (f_x10);

2. la frequenza della portante (f_pwm);

3. il valore della tensione di uscita, moltiplicato per dieci (V_x10);

4. l’indice di modulazione moltiplicato per 1000 (m_a_x1000);

5. il flag di blocco sovramodulazione (block_overmod);

6. il rapporto di divisione (f_x1000_ratio) per la generazione del clock per lo scorrimento dei

valori della look-up-table (LUT) della funzione y=sin(x), di frequenza pari a 1000 volte la

frequenza da generare, dal momento che tale è il numero di punti della LUT;

7. il rapporto di divisione (f_pwm_x4R_ratio) per la generazione del clock che costituisce la

base dei tempi dei modulatori PWM relativi alle tre fasi, di frequenza pari a quella della

portante moltiplicata per 4R, dove ±R è l’escursione massima dei segnali in ingresso a

ciascun modulatore.

Il funzionamento del componente VHDL principale (V_f_control.vhd) e il modo in cui in esso

sono implementate le curve delle figure 3-4 sono stati già descritti nel rapporto tecnico n. 412 [11].

Rapporto Tecnico RT – ISSIA – PA – N. 413 – 2011

11

Si evidenzia soltanto che, per semplicità di implementazione, è stato deciso di impedire al

sistema il funzionamento in sovramodulazione; in tal caso, infatti, non sarebbe semplice prevedere

il valore della tensione di uscita a partire dalla conoscenza dell’indice di modulazione.

Pertanto, determinato il valore della tensione di uscita V_x10, è possibile ricavare l’indice di

modulazione mediante la seguente equazione, valida in zona lineare:

m _ a _ x1000 =

V

(V _ x10) ⋅ 1634 (V _ x10) ⋅ 1634

⋅ 1,634 ⋅ 1000 =

=

V DC

V DC ⋅ 10

M6

in cui il parametro M6 indica la tensione del DC-link moltiplicata per 10.

Viene, quindi, verificato se il valore precedentemente calcolato è maggiore di 1000, ovvero se

al riferimento di frequenza impostato corrisponde una tensione di usita che comporta un

funzionamento al di fuori della zona lineare della modulazione PWM. In caso affermativo, il nuovo

riferimento di frequenza non viene impostato e viene portato a 1 il livello del segnale di uscita

block_overmod, che sarà utilizzato in seguito per far lampeggiare il corrispondente LED.

Tale segnale viene attivato anche in base all’esito di una seconda verifica. Per evitare distorsioni

della forma d’onda generata, si valuta se i valori impostati comportano una modulazione PWM con

impulsi di durata inferiore al parametro A1, quindi non generabili dai driver IGBT a bordo

dell’inverter Semikron; di essi è stata fatta una preventiva caratterizzazione che ha consentito di

scegliere il valore di default del parametro A1, cioè 5µs. La suddetta verifica viene effettuata

valutando se:

m a ≤ (1 − f pwm ⋅ 2 ⋅ t min )

ovvero se:

MAIN_CLK_FREQ

2 ⋅ A1

m _ a _ x1000 ≤ 1000 ⋅ 1 −

⋅

4 R ⋅ f_pwm_x 4 R_ratio 1.000.000

Per quanto concerne i parametri dei modulatori PWM, è stato scelto per R ed S il valore 500,

mentre la LUT fornisce in uscita i riferimenti per la generazione delle tre sinusoidi moltiplicati per

1000, cioè nel range [-1000; 1000]. Inoltre, i riferimenti vanno moltiplicati per l’indice di

modulazione anch’esso moltiplicato per 1000. Pertanto, il valore ref_sine da applicare all’ingresso

del modulatore di ciascuna fase potrà essere ottenuto mediante la seguente equazione:

ref_sine =

sin X _ x1000 m _ a _ x1000 sin X _ x1000 ⋅ m _ a _ x1000

⋅

=

2

1000

2000

Le uscite dei tre modulatori PWM sono, quindi, portate all’esterno dell’FPGA e costituiscono

i segnali di pilotaggio per gli IGBT dei rispettivi rami dell’inverter Semikron.

Parallelamente, il blocco denominato UI_SSD_display riceve in ingresso i segnali 1÷5 generati

dal blocco principale V_f_control e il valore del riferimento di frequenza impostato, moltiplicato per

dieci (f_x10_ref). Leggendo lo stato del commutatore rotativo ABCD, esso formatta

opportunamente il valore della grandezza selezionata (segnale item_sampled) e la posizione del

punto decimale (segnale dp_vector) e li trasferisce al blocco SSD_driver per l’effettiva

visualizzazione sul display SSD, pilotato in multiplex con frequenza di scansione pari a 250 Hz e

frequenza di aggiornamento del valore pari a 2 Hz.

Rapporto Tecnico RT – ISSIA – PA – N. 413 – 2011

12

Per quanto concerne i clock, a bordo della scheda Altera è presente un oscillatore a 50 MHz

che, tramite software, è stato collegato al PLL interno per la generazione del clock principale a

120 MHz. Gli altri clock necessari sono ottenuti da quest’ultimo sotto forma di segnali di clock

enable mediante opportuni divisori di frequenza con rapporto fisso o variabile e sono i seguenti:

• il clock per la gestione dell’interfaccia utente (UI_clk_en);

• il clock per la generazione delle rampe di accelerazione e di decelerazione

(upd_ramp_clk_en);

• il clock per lo scorrimento dei valori della look-up-table (LUT) per la generazione di una

terna simmetrica diretta di sinusoidi (clk_f_x1000_en);

• il clock che costituisce la base dei tempi dei modulatori PWM relativi alle tre fasi

(clk_fpwm_x4R_en).

Rapporto Tecnico RT – ISSIA – PA – N. 413 – 2011

13

Fig. 9. Schema a blocchi dell’implementazione in linguaggio VHDL

Rapporto Tecnico RT – ISSIA – PA – N. 413 – 2011

14

4. PROCEDURA DI MESSA IN SERVIZIO

Il flowchart di seguito riportato illustra la procedura di messa in servizio del sistema; le diverse fasi

sono di seguito descritte.

Fig. 10. Flowchart della procedura di messa in servizio

4.1 Esecuzione dei collegamenti elettrici

L’operazione preliminare da effettuare per la messa in servizio dell’inverter è la realizzazione dei

collegamenti elettrici. Dopo aver collegato l’insieme costituito dalla scheda FPGA Altera e dalla

scheda di espansione Nial Stewart GPIB all’alimentatore fornito in dotazione, occorre collegare il

potenziometro lineare multigiri da 1 kΩ all’ingresso analogico ADC0 della scheda GPIB.

Successivamente è necessario collegare mediante il cavo flat il modulo display SSD allo zoccolo

DIP24 presente sulla scheda GPIB. Quindi si deve connettere la scheda GPIB ai 6 ingressi di

pilotaggio dell’inverter Semikron mediante il cavo DB15-RCA in dotazione. Infine, occorre

collegare i due ingressi del DC-link dell’inverter ad un alimentatore in continua di potenza

opportuna e le tre uscite al motore asincrono da alimentare.

Rapporto Tecnico RT – ISSIA – PA – N. 413 – 2011

15

4.2 Modifica dei parametri e ricompilazione

Se la scheda risulta già programmata in precedenza e non si ravvisa la necessità di variare i

parametri di configurazione, è possibile saltare direttamente al passo 4.4.

In caso contrario, collegare la scheda Altera mediante un cavo USB ad un PC dotato del software

Quartus II. Avviare il suddetto programma e caricare il progetto inverter_V_f.qpf nell’ambiente di

lavoro. Editare il file inverter_parameters.vhd, modificando i parametri desiderati. La tab. 3 riporta

per ciascun parametro la sua descrizione, il range di variazione, il valore di default e l’eventuale

fattore di scala. Si evidenzia il fatto che i parametri C1÷C10 sono relativi alle curve caratteristiche

riportate nelle figure 3 e 4.

Tab. 3. Parametri di configurazione

Parametro

A01

M06

P05

P06

C01

C02

C03

C05

C06

C07

C08

C09

C10

W01

Descrizione

Campo di valori

ammessi

Valore

di

default

5 µs

Durata minima degli impulsi PWM generabili dai driver IGBT

0-10 µs

dell’inverter

Valore della tensione del DC-link

0-3·C08

560 V

Durata della rampa di accelerazione da 0 a f_max (parametro

0-6500 s

10 s

C06)

Durata della rampa di decelerazione da f_max (parametro C06) a

0-6500 s

10 s

0

Valore minimo della frequenza di modulazione PWM

0.6-12.8 kHz

10 kHz

Valore massimo della frequenza di modulazione PWM

0.6-12.8 kHz

10 kHz

Numero di impulsi generati dalla modulazione PWM nel

12-384 secondo

24

passaggio dalla minima alla massima frequenza di modulazione

multipli pari di 12

PWM

Frequenza nominale del motore relativa alla curva tensione3.5-800 Hz

50 Hz

frequenza. Determina il passaggio dal funzionamento a V/f

costante al funzionamento a V costante

Frequenza massima d’uscita relativa alla curva tensione3.5-800 Hz

50 Hz

frequenza. Frequenza in uscita dall’inverter in corrispondenza del

massimo valore di riferimento

Frequenza minima di uscita relativa alla curva tensione0.5-5 Hz

0.5 Hz

frequenza. Minima frequenza generata all’uscita dall’inverter

Tensione nominale del motore. Determina la tensione d’uscita

1-460 V

380 V

alla frequenza nominale del motore

Boost di tensione a bassi giri. Determina l’incremento della

0-100%

0

tensione di uscita a basse frequenze rispetto al rapporto tensionefrequenza costante

Pre-boost di tensione a bassi giri. Determina la tensione di uscita

0-5%

2.5%

teorica a 0 Hz.

Errore in fase di compilazione se non è possibile generare la

0-1

0

tensione nominale del motore (C08) con indice di modulazione

m_a≤1

Fattore

di

scala

x10

x10

x10

x10

x10

Dopo aver modificato i parametri desiderati, ricompilare il progetto premendo la combinazione di

tasti CTRL-L. Opportune righe di codice VHDL verificheranno automaticamente la coerenza dei

parametri immessi. Se la tensione del DC-link risulta maggiore del triplo della tensione nominale

del motore, la compilazione sarà interrotta con il seguente messaggio di errore: “DC-link voltage is

too high”. Se, invece, il parametro W01 è impostato a 1 e la tensione del DC-link è insufficiente a

consentire l’alimentazione del motore alla tensione nominale rimanendo nella zona lineare della

modulazione PWM, ovvero con indice di modulazione ma≤1, la compilazione sarà interrotta con il

seguente messaggio di errore: “DC-link voltage is too low”. In ogni caso, al termine della

compilazione verrà salvato un file denominato inverter.sof nella cartella del progetto.

Rapporto Tecnico RT – ISSIA – PA – N. 413 – 2011

16

4.3 Programmazione

Per trasferire il codice compilato sulla EEPROM a bordo della scheda Altera, è necessario dapprima

convertire il file inverter.sof in formato .pof mediante i controlli della finestra “Convert

Programming Files” richiamabile tramite la relativa voce del menu “File”. I parametri da utilizzare

sono i seguenti:

• configuration device: CFI_128MB

• mode: active parallel

• input file: inverter.sof

• SOF data properties: address mode=start, start address=0x020000

Ottenuto il file .pof, aprire l’interfaccia del programmatore mediante la voce “Programmer” del

menu “Tools”, caricare il suddetto file e trasferirlo sulla EEPROM premendo il pulsante “Start”

presente sulla barra posta a sinistra dell’interfaccia o la corrispondente voce del menu “Processing”.

L’operazione dura meno di un minuto.

4.4 Stand-by, avviamento, marcia e arresto; visualizzazione display SSD

Accendere la scheda Altera mediante l’apposito interruttore. Il sistema si troverà in stato di

stand-by: tutti i segnali di pilotaggio saranno nulli e il display SSD si accenderà. Posizionare il

selettore ABCD presente sulla scheda SSD sulla posizione A in modo da visualizzare il riferimento

di frequenza impostato mediante il potenziometro. E’ possibile agire sul potenziometro e

contemporaneamente leggere la corrispondente indicazione sul display SSD.

Scelto il valore desiderato per la frequenza di riferimento, premere il pulsante START,

corrispondente al pulsante “Button 4” della scheda Altera. Il relativo LED, posizionato

immediatamente sopra il pulsante, si accenderà per conferma e il motore si avvierà seguendo la

rampa di accelerazione preimpostata. E’ possibile visualizzare sul display SSD le seguenti

informazioni, aggiornate in tempo reale:

• frequenza di riferimento, impostata mediante il potenziometro;

• frequenza effettiva di alimentazione;

• tensione concatenata di uscita in valore efficace;

• frequenza della portante;

• indice di modulazione.

E’ da segnalare che è possibile variare il riferimento di frequenza anche a motore già avviato.

Come precedentemente specificato, l’inverter lavora solo nella zona lineare della modulazione

PWM; pertanto, se il parametro W01 è impostato a zero e si scelgono valori di frequenza che

implicano il funzionamento in sovramodulazione, essi non verranno attuati; si avrà comunque un

funzionamento con indice di modulazione unitario e il LED di segno del display SSD lampeggerà.

Diminuendo il valore del riferimento di frequenza, il LED smetterà di lampeggiare.

Volendo arrestare il motore, sarà sufficiente premere il pulsante STOP, corrispondente al pulsante

“Button 3” della scheda Altera; il relativo LED si accenderà per conferma e il motore si arresterà

seguendo la rampa di decelerazione preimpostata.

4.5 Reset

Qualora nel corso delle operazioni si rilevi un allarme o un’anomalia, agendo sul pulsante RESET

della scheda Altera sarà possibile togliere immediatamente tensione in uscita all’inverter, per cui il

motore si arresterà per inerzia. Il sistema si riporterà nello stato di stand-by; pertanto, per far

ripartire il motore sarà sufficiente premere nuovamente il pulsante START.

Rapporto Tecnico RT – ISSIA – PA – N. 413 – 2011

17

CONCLUSIONI E SVILUPPI FUTURI

Il sistema realizzato costituisce un inverter completo per il controllo V/f di motori asincroni

trifase, con possibilità di fornire esternamente la tensione del DC-link, senza restrizioni sulla

tensione minima di uscita. Pertanto, regolando opportunamente la tensione del DC-link ed

aggiornando conseguentemente uno specifico parametro dell’inverter configurabile dall’utente, è

possibile alimentare sia motori automotive, sia motori per azionamenti industriali.

L’algoritmo di controllo è stato codificato in linguaggio VHDL e programmato su una scheda

FPGA Altera. Per la sezione di potenza è stato usato un kit Semikron Semiteach.

Il sistema implementa le rampe di accelerazione e di decelerazione e le curve V/f e f_carrier/f

tipiche degli inverter commerciali e, in particolare, del modello SINUS/IFDE-F 400T-5.5kW della

ditta Elettronica Santerno. Le curve sono completamente configurabili mediante una serie di

parametri programmabili dall’utente.

L’inverter lavora nella zona lineare della modulazione PWM e fornisce un’indicazione visiva

qualora il riferimento di velocità impostato richieda il funzionamento in sovramodulazione o

comporti la generazione di impulsi PWM di durata inferiore al minimo valore consentito dai driver

IGBT impiegati.

Il prototipo realizzato è stato collaudato positivamente ed ha consentito di alimentare un

motore asincrono per uso automotive da 1,1 kW con tensione nominale pari a 42 V per poter

realizzare le misure necessarie a verificare le prestazioni di un filtro attivo EMI oggetto di ricerca. Il

sistema ha consentito l’avviamento del motore già a partire da un riferimento di frequenza pari a

4 Hz ed un buon controllo della forma d’onda d’uscita. Pertanto, esso è stato integrato al banco di

prova su filtri automotivi già esistente all’interno del laboratorio Interferenze Elettromagnetiche

Condotte e Power Quality in dotazione all’ISSIA-CNR u.o.s. di Palermo.

Per quanto concerne gli sviluppi futuri, è stata iniziata la fase di progettazione di una scheda

dotata di 5 pulsanti e di un display a cristalli liquidi 16x2, da sostituire alla scheda SSD attualmente

impiegata. Essa consentirà non soltanto la visualizzazione delle grandezze di interesse, ma anche la

riprogrammazione on-line dei parametri dell’inverter, senza la necessità di modificare il file

sorgente, né di dover collegare la scheda Altera ad un PC. A tale scopo è in corso di scrittura un

ulteriore componente VHDL che implementerà il menu interattivo di configurazione del sistema.

Inoltre, sarà implementato un comando di inversione di marcia attraverso tre fasi distinte:

rampa di decelerazione fino a velocità nulla; inversione del verso di rotazione; rampa di

accelerazione fino alla velocità impostata.

Rapporto Tecnico RT – ISSIA – PA – N. 413 – 2011

18

RIFERIMENTI BIBLIOGRAFICI

[1]

M. Luna, A. Sauro, S. G. Scordato. Rapporto tecnico RT-ISSIA-PA-N. 407-2011. “Analisi

dei laboratori del CNR-ISSIA u.o.s. di Palermo ed individuazione di possibili interventi

migliorativi”. Data di creazione: 05/11/2010. Prima distribuzione al pubblico e deposito

legale: 18/07/2011 presso Biblioteca Nazionale Centrale di Roma, Biblioteca Nazionale

Centrale di Firenze, Biblioteca Centrale della Regione Siciliana.

[2] M.C. Di Piazza, M. Luna, A. Ragusa, G. Vitale. “An Improved Common Mode Active Filter

for EMI Reduction in Vehicular Motor Drives”. IEEE Vehicle Power and Propulsion

Conference, VPPC 2011, 6-9 Sept 2011. Chicago, USA (accepted for presentation).

[3] B.K. Bose. “Modern Power Electronics and AC Drives”. 2002. Prentice Hall PTR.

[4] Manuale d’uso dell’inverter a controllo digitale SINUS/IFDE-F 400T-5.5 kW. Versione

software 2.01. Dicembre 1996. Elettronica Santerno s.p.a. Imola (Italy).

[5] Altera. Cyclone III FPGA Starter Board Reference Manual. October 2007.

http://www.altera.com/products/devkits/altera/kit-cyc3-starter.html

[6] Nial Stewart Developments Ltd. HSMC General Purpose Interface Board (GPIB) User Guide.

http://www.nialstewartdevelopments.co.uk/products.htm

[7] Altera. Introduction to the Quartus® II Software. Version 9.1.

http://www.altera.com/products/software/quartus-ii/web-edition/qts-we-index.html

[8] VHDL Standard - IEEE Standard for VHDL Register Transfer Level (RTL) Synthesis

(1076.6-1999).

[9] M. Luna, M. Pucci, G. Vitale. Rapporto tecnico RT-ISSIA-PA-N. 409-2011. “Libreria VHDL

di componenti per il laboratorio Energie Rinnovabili ed Azionamenti Elettrici del CNR-ISSIA

u.o.s. di Palermo. Revisione 1.1: implementazione di un modulatore PWM deterministico e

random”. Data di creazione: 14/12/2010. Prima distribuzione al pubblico e deposito legale:

18/07/2011 presso Biblioteca Nazionale Centrale di Roma, Biblioteca Nazionale Centrale di

Firenze, Biblioteca Centrale della Regione Siciliana.

[10] M. Luna. Rapporto tecnico RT-ISSIA-PA-N. 410-2011. “Libreria VHDL di componenti per il

laboratorio Energie Rinnovabili ed Azionamenti Elettrici del CNR-ISSIA u.o.s. di Palermo.

Revisione 1.2: implementazione delle look-up table (LUT) per il calcolo delle funzioni

trigonometriche sin(x) e cos(x)”. Data di creazione: 03/02/2011. Prima distribuzione al

pubblico e deposito legale: 18/07/2011 presso Biblioteca Nazionale Centrale di Roma,

Biblioteca Nazionale Centrale di Firenze, Biblioteca Centrale della Regione Siciliana.

[11] M. C. Di Piazza, M. Luna, G. Vitale. Rapporto tecnico RT-ISSIA-PA-N. 412-2011. “Libreria

VHDL di componenti per il laboratorio Energie Rinnovabili ed Azionamenti Elettrici del

CNR-ISSIA u.o.s. di Palermo. Revisione 1.4: implementazione dei componenti necessari per

il controllo V-f”. Data di creazione: 10/05/2011. Prima distribuzione al pubblico e deposito

legale: 18/07/2011 presso Biblioteca Nazionale Centrale di Roma, Biblioteca Nazionale

Centrale di Firenze, Biblioteca Centrale della Regione Siciliana.

[12] Analog Devices. AD7908/AD7918/AD7928 datasheet. Rev. C. November 2008.

Rapporto Tecnico RT – ISSIA – PA – N. 413 – 2011

19

APPENDICE A

Tab. A.1. Caratteristiche del modulo SKM50GB123D (1)

Tab. A.2 e A.3. Caratteristiche del modulo SKM50GB123D (2)

Rapporto Tecnico RT – ISSIA – PA – N. 413 – 2011

20

Tab. A.4. Caratteristiche del driver SKHI22AR

Rapporto Tecnico RT – ISSIA – PA – N. 413 – 2011

21

APPENDICE B

A mero titolo informativo, la sottostante tabella riporta l’associazione tra il nome di ciascun segnale

del codice VHDL e il corrispondente pin del chip FPGA, da impostare mediante l’interfaccia Pin

Planner, accessibile richiamando la corrispondente voce del menu Assignments. Si tratta comunque

di un’operazione normalmente non richiesta, in quanto tali assegnazioni sono state già specificate

nel file del progetto.

Tab. B.1. Assegnazioni segnale-pin nel Pin Planner

adc_cs_n

adc_din

adc_dout

adc_sclk

master_clk

rst_n

probe_ops_valid

probe_sclk

ssd_addr[1]

ssd_addr[0]

ssd_digit[0]

ssd_digit[1]

ssd_digit[2]

ssd_digit[3]

ssd_dp

ssd_sign

output_PWM_T1A

output_PWM_T1B

output_PWM_T1C

output_PWM_T2A

output_PWM_T2B

output_PWM_T2C

sync

start_btn_n

stop_btn_n

selector_ABCD[1]

selector_ABCD[0]

btn_leds_n[1]

btn_leds_n[0]

PIN_A1

PIN_E1

PIN_N10

PIN_J13

PIN_V9

PIN_N2

PIN_L4

PIN_L3

PIN_H18

PIN_L17

PIN_M18

PIN_P17

PIN_N13

PIN_L14

PIN_N6

PIN_M13

PIN_K1

PIN_N15

PIN_C1

PIN_H16

PIN_T16

PIN_H1

PIN_L5

PIN_B10

PIN_A10

PIN_T3

PIN_P1

PIN_N9

PIN_N12

Rapporto Tecnico RT – ISSIA – PA – N. 413 – 2011

22