Esercitazione 2

ELETTRONICA PER LE TELECOMUNICAZIONI

AA 2004-05

ESERCITAZIONE DI LABORATORIO B

Sede di IVREA

(B6)

PLL: campi di aggancio e sintetizzatore di frequenza

Scopo dell’esercitazione

Gli obiettivi di questa esercitazione sono:

- Verificare il comportamento di un PLL

- Determinare i campi di cattura e di mantenimento del PLL

- Verificare il funzionamento di sintetitizzatori di frequenza di vario tipo

Moduli e componenti da utilizzare

I circuiti richiesti devono essere predisposti sulle basette per montaggi senza saldature.

Informazioni sull'uso delle basette sono reperibili sul sito web:

Materiale didattico > Uso delle basette per montaggi senza saldature

Per il PLL viene usato un circuito integrato CD 4046; il sintetizzatore richiede due circuiti

integrati tipo CD 4029 (contatore a 4 bit programmabile). I data sheet di entrambi i

componenti sono reperibili sul sito web:

Materiale didattico > Data sheet

Altro materiale: R e C per il VCO e il filtro di anello, R di pull-up e SW per i comandi ai

contatori.

Strumenti richiesti

Alimentatore (5 V), generatore di segnale (50 kHz compatibile CMOS), oscilloscopio,

frequenzimetro, multimetro.

Le verifiche di funzionamento dei circuiti vanno eseguite con l’oscilloscopio.

Le misure di frequenza vanno eseguite con il frequenzimetro.

Avvertenze

Ricordare che nei circuiti CMOS tutti gli ingressi devono essere collegati a una tensione

corrispondente a uno stato logico ben definito, e che a un circuito integrato non deve mai

essere applicata una tensione esterna all’intervallo tra le alimentazioni.

ETLClab2d - © DDC - rev 19/10/2004 7:31 PM

Page 1 of 4

ELETTRONICA PER LE TELECOMUNICAZIONI

AA 2004-05

ESERCITAZIONE DI LABORATORIO B

Sede di IVREA

2.1 – Specifiche

Realizzare il montaggio con riferimento allo schema

indicato nel data sheet e i componenti:

VCO:

R1 = 15kΩ

Filtro RRC:

R2 = 1 MΩ

R3 = 100 k

C1 = 68 pF;

R4 = 10 k C2 = 4,7 nF;

C3 (ingresso) = 270 nF

2.2 – Caratteristica del VCO

Questo punto richiede di tracciare la caratteristica del VCO (ad anello aperto), per verificare il

campo di frequenze su cui può lavorare il PLL.

-

montare il circuito senza collegare l'ingresso del VCO

applicare al VCO una tensione esterna Vc variabile tra GND e Vdd (usare un

potenziometro collegato tra massa e alimentazione Vdd)

variare Vc e misurare la frequenza,

tracciare fo(Vc)

2.3 – Campi di cattura e di mantenimento

Per questa parte e in tutti i punti seguenti, controllare l'aggancio visualizzando

sull'oscilloscopio i segnali Vi e Vo. Ad anello agganciato devono essere isofrequenziali e

stabili. Se sono stabili ma con frequenza diversa, il PLL è in un campo di aggancio

secondario. Per verificare l'effettivo aggancio fare piccoli spostamenti della Fr; il segnale del

VCO deve spostarsi di conseguenza.

2.3.1 Anello con DF II

Obiettivo della prima misura è determinare gli estremi dei campi di cattura e di mantenimento.

- Chiudere l'anello usando il demodulatore II.

- Applicare segnale attraverso il condensatore C3. Usare segnale sinusoidale oppure a

onda quadra con Vpp = Vdd/2.

- Spostare la frequenza di ingresso in modo da coprire un intervallo poco più ampio del

campo di funzionamento del VCO (ricavato al punto 2.2), e determinare il campo di

cattura e quello di mantenimento.

Il DFII è un circuito a pompa di carica, e determina un guadagno di anello infinito. In questa

condizione i campi di cattura e di mantenimento coincidono, e l’errore di fase è sempre nullo.

ETLClab2d - © DDC - rev 19/10/2004 7:31 PM

Page 2 of 4

ELETTRONICA PER LE TELECOMUNICAZIONI

AA 2004-05

ESERCITAZIONE DI LABORATORIO B

Sede di IVREA

2.3.2 Anello con DF I

Per ottenere campi di cattura e di mantenimento distinti occorre utilizzare il demodulatore I.

La frequenza di taglio del filtro di anello usata in precedenza determina un campo di cattura

molto stretto; calcolare il filtro in base alle indicazioni del data sheet.

-

Spostare la richiusura dell'anello sul DF I

Determinare i campi di cattura e di mantenimento

Verificare la variazione dell'errore di fase al variare della frequenza entro il campo di

mantenimento.

(la misura con il DF I non è legata ai punti successivi, e la misura dell’errore di fase richiede

un certo tempo. Se l’obiettivo principale è verificare il funzionamento del sintetizzatore, questo

passo può essere saltato).

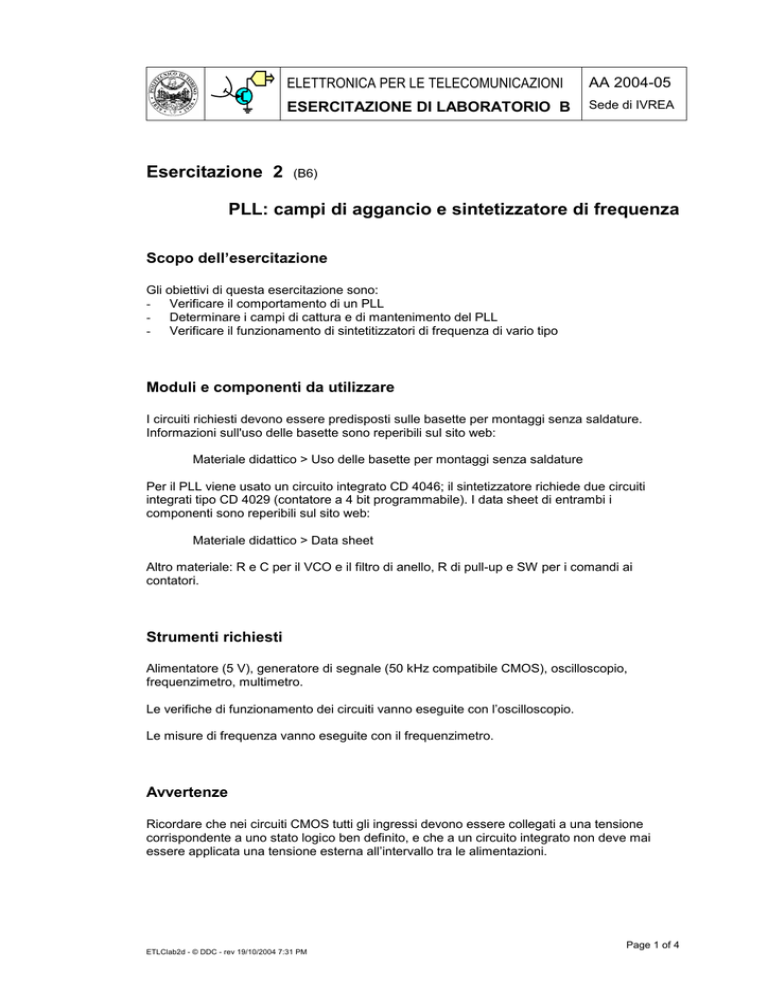

2.4 – Moltiplicatore di frequenza

In questa misura e nelle successive utilizzare sempre il DF II, con filtro di anello R3-R4-C2

(rete con polo e zero), dimensionando R3*C2 con il criterio fmin/10, e R4 = R3/10.

Il primo punto prevede la realizzazione di un moltiplicatore di frequenza a fattore fisso.

-

Montare un divisore modulo 4 usando il contatore programmabile CD4029, e verificarne il

funzionamento (impostare conteggio continuo modulo 16, e utilizzare l'uscita del secondo

FF).

Inserire nell'anello, tra uscita del VCO e ingresso del DF, il divisore modulo 4.

applicare all'ingresso un segnale a frequenza Fr = 25 kHz.

verificare l'aggancio del PLL (anche per piccole variazioni di Fr) e la frequenza generata

dal VCO.

E’ possibile variare il fattore di moltiplicazione

secondo potenze di 2 (2, 4, 8, 16), spostando l’uscita

del divisore su altri stadi del contatore. Occorre

impostare una frequenza di riferimento tale che la

frequenza di uscita rientri nel campo coperto dal VCO.

Verificare che variando la frequenza di riferimento la

frequenza del VCO varia secondo il rapporto di

moltiplicazione.

ETLClab2d - © DDC - rev 19/10/2004 7:31 PM

Fr

Fi

DF

Fo

F(s)

:2 4 8 16

VCO

Fu

Page 3 of 4

ELETTRONICA PER LE TELECOMUNICAZIONI

AA 2004-05

ESERCITAZIONE DI LABORATORIO B

Sede di IVREA

2.5 Sintetizzatore con moltiplicazione variabile (modulo N)

Questo punto prevede la realizzazione di un semplice sintetizzatore di frequenza a modulo

variabile. Per dare i comandi al CD4029 conviene inserire delle resistenze di pull-up sugli

ingressi, e collegarli a massa per dare uno stato L (senza rimuovere il pull-up). Se disponibili,

collocare sugli ingressi da comandare dei DIP-SW (gruppo di più interruttori in contenitore

dual-in-line - DIL) verso massa, oppure utilizzare il modulino SW/R/LED premontato.

-

-

modificare il circuito del CD4029 in modo da

poter variare il modulo di conteggio N tra 2 e 15,

e verificarne il funzionamento al di fuori del PLL.

Per ottenere i diversi moduli di divisione utilizzare

gli ingressi di preset e l'uscita Q4 (divisione fino a

7).

Inserire il divisore programmabile nell'anello, tra

uscita del VCO e ingresso del DF.

verificare che il PLL mantiene l'aggancio per tutto

il campo di N.

Misurare le frequenze ottenute dal VCO per

diversi moduli di conteggio N (almeno 4 casi)

Fr

F1

DF

Fo

:N

F2

F(s)

VCO

2.6 Sintetizzatore a interi M/N

Questo punto permette di verificare il funzionamento di un sintetizzatore a rapporti interi

(M/N).

-

P

inserire un divisore binario (modulo M = 2 ) sul segnale di riferimento (Frequenza 1 MHz).

Inserire il divisore modulo N tra VCO e DF.

Verificare il segnale Vi e l'uscita Vo del VCO per P = 1, 2, 3, 4, con divisore N = 2.

Verificare il segnale Vi e l'uscita Vo del VCO per P = 1, 2, 3, 4, con divisore N = 16. Viene

mantenuto l'aggancio per tutti i valori di P ?

Verificare il segnale Vi e l'uscita Vo del VCO per P = 1, 2, 3, 4, con divisore N variabile tra

1 e 7. Verificare per quali combinazioni (P,N) viene mantenuto l'aggancio.

Trasformare il divisore del segnale di riferimento in divisore modulo M (stesso circuito

inserito nell'anello al punto 2.4).

Verificare le combinazioni estreme e alcuni casi intermedi per M e N.

Per M e N variabili tra 2 e 16:

•

•

Quale è il campo di frequenze

complessivamente coperto dal sintetizzatore ?

Quale è il passo del sintetizzatore (spaziatura tra

i canali) ?

F1

Fr

:M

Fo

:N

DF

F2

F(s)

VCO

ETLClab2d - © DDC - rev 19/10/2004 7:31 PM

Page 4 of 4