Esercitazione : REALIZZAZIONE IMPIANTO SEMAFORICO

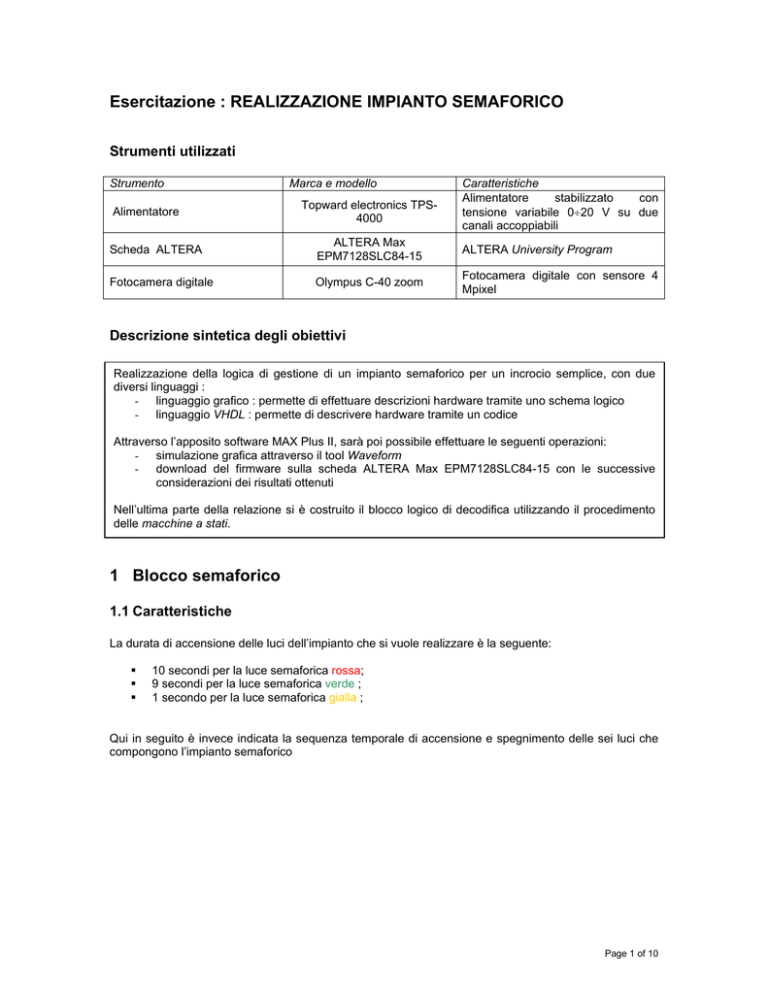

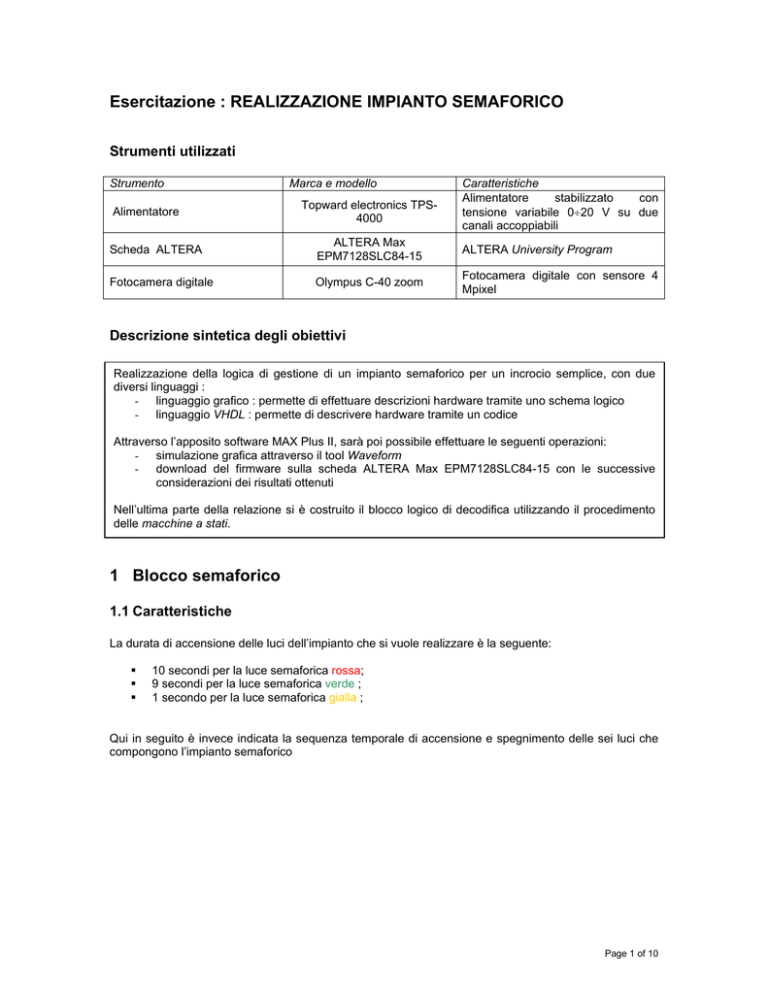

Strumenti utilizzati

Strumento

Alimentatore

Marca e modello

Topward electronics TPS4000

Caratteristiche

Alimentatore

stabilizzato

con

tensione variabile 0÷20 V su due

canali accoppiabili

Scheda ALTERA

ALTERA Max

EPM7128SLC84-15

ALTERA University Program

Fotocamera digitale

Olympus C-40 zoom

Fotocamera digitale con sensore 4

Mpixel

Descrizione sintetica degli obiettivi

Realizzazione della logica di gestione di un impianto semaforico per un incrocio semplice, con due

diversi linguaggi :

- linguaggio grafico : permette di effettuare descrizioni hardware tramite uno schema logico

- linguaggio VHDL : permette di descrivere hardware tramite un codice

Attraverso l’apposito software MAX Plus II, sarà poi possibile effettuare le seguenti operazioni:

- simulazione grafica attraverso il tool Waveform

- download del firmware sulla scheda ALTERA Max EPM7128SLC84-15 con le successive

considerazioni dei risultati ottenuti

Nell’ultima parte della relazione si è costruito il blocco logico di decodifica utilizzando il procedimento

delle macchine a stati.

1 Blocco semaforico

1.1 Caratteristiche

La durata di accensione delle luci dell’impianto che si vuole realizzare è la seguente:

10 secondi per la luce semaforica rossa;

9 secondi per la luce semaforica verde ;

1 secondo per la luce semaforica gialla ;

Qui in seguito è invece indicata la sequenza temporale di accensione e spegnimento delle sei luci che

compongono l’impianto semaforico

Page 1 of 10

1.2 Divisione in frequenza

La scheda utilizzata possiede un Global Clock, interno, ad una frequenza elevata pari a 25MHz.

Poiché bisogna gestire la durata dell’accensione e dello spegnimento delle singole luci semaforiche in

termini di secondi, si è dovuta ridurre la frequenza di Global Clock e adattarla il più possibile alle nostre

esigenze.

Si è dovuto realizzare un rapporto di riduzione pari a:

25MHz

n

≅2

1

Hz

dove una frequenza di 1Hz corrisponde ad un periodo di un secondo, e n indica il numero di flip-flop

necessari da collegare in cascata.

Il numero di flip-flop risultante che realizza il divisore di frequenza, è stato approssimato per difetto ed è

pari a ventiquattro. Inizialmente si è creato un divisore che riduce la frequenza di sedici volte, mediante

quattro flip-flop.

Per comodità poi, questi quattro flip-flop sono stati racchiusi in un unico blocco logico che è stato

successivamente utilizzato sei volte.

Page 2 of 10

Page 3 of 10

1.3 Logica combinatoria

Per determinare gli istanti di accensione e spegnimento delle luci semaforiche, si è utilizzato un

contatore il quale viene incrementato ad ogni colpo di clock.

In uscita da questo si ottiene una codifica del tempo trascorso su cinque bit come segue:

Cod. DECIMALE

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

Rosso_1

Si è pensato di codificare il

periodo dei 10 secondi iniziali

analizzando solo i due bit più

significativi per i primi otto a

intervalli ai quali si è aggiunta

l’intera codifica del nono e del

decimo

Rosso_2

Negazione della fase di

accensione di Rosso_1

Cod. BINARIA

00000

00001

00010

00011

00100

00101

00110

00111

01000

01001

01010

01011

01100

01101

01110

01111

10000

10001

10010

10011

10100

Semaforo #1

Giallo_1

Verde_1

Si sono codificati gli intervalli

undicesimo e dodicesimo per

intero; gli intervalli dal dodicesimo

escluso al sedicesimo compreso

Si è codificata la sequenza di bit

considerando i tre bit più

corrispondente al diciannovesimo

significativi; gli ultimi tre intervalli

intervallo temporale

sono codificati con il bit più

significativo, curandosi di

escludere il diciannovesimo

intervallo

Semaforo #2

Giallo_2

Si è codificata la sequenza di bit

corrispondente al decimo

intervallo

Verde_2

Si sono codificati i primi otto

intervalli considerando i due bit

più significativi, e il nono a parte

2 Circuito

A questo punto si è passati alla realizzazione del sistema semaforico in due differenti modi:

Metodo 1: attraverso le normali funzioni logiche offerte da MAX Plus II

Metodo 2: attraverso l’utilizzo del linguaggio hardware VHDL che ha reso possibile la

realizzazione in tempi ridotti del medesimo progetto

Page 4 of 10

2.1 Circuito logico (I)

Page 5 of 10

2.2 Circuito logico (II)

Da ricordare è che nello schema finale, sono state aggiunte delle porte not davanti a tutte le sei uscite

per tener conto del fatto che i diodi led, implementati sulla scheda ALTERA, sono realizzati con una

configurazione di tipo pull-up.

Il blocco INCROCIO, è stato realizzato a partire dal seguente file .vhd

Page 6 of 10

dove:

Entity

Architecture

Tale funzione descrive l’interfaccia esterna del

blocco logico incrocio.

Num è l’ingresso che può assumere un valore

compreso tra 0 e 19.

Le uscite: Rosso1, Rosso2, Verde1, etc… sono

codificate su di un singolo bit.

Tale funzione descrive la funzionalità del blocco

logico incrocio.

All’interno di questa si è indicato in quali istanti ogni

luce semaforica deve essere accesa o spenta.

Il blocco DIV_FREQ4 invece, era invece il blocco contenente la serie di flip-flop precedentemente

illustrata.

3 Simulazione

3.1 Waveform

Prima di scaricare sulla scheda il programma, se ne è simulato il comportamento, attraverso il Waveform

di MAX Plus II visualizzando più cicli:

Page 7 of 10

4 Prova al banco

4.1 Download firmware

Una volta alimentata la scheda a +9V, si è passati alla fase di scaricamento del firmware attraverso il

cavo di interfaccia opportunamente collegata con il PC attraverso la porta parallela.

Anche in questa fase occorre però alimentare la scheda

ad una tensione continua di ≅ +9V.

Onde evitare sbalzi di tensione tali da poter danneggiare

la scheda, occorre ricordare sempre di collegare tutti i

cavi, prima di alimentare il tutto.

4.2 Piedinatura chip

Una volta compilato il file .gdf contenente il circuito dell’impianto semaforico, si è fatto riferimento alla

piedinatura della MAX Flex, in modo da poter collegare con i giusti riferimenti, la varie uscite.

Page 8 of 10

5 Analisi risultati

5.1 Delay Matrix

E’ stata fatta una verifica sui vari

tempi di ritardo che il circuito

realizzato presentava, attraverso il

Timing Analyzer.

Si è potuto riscontrare come

entrambi i segnali di uscita

commutassero stato logico dopo

151ns dalla commutazione di stato

del clock.

Inoltre è stata eseguita una ulteriore verifica sempre attraverso il

Timing Analyzer di MAX Plus II. E’ stata quindi verificata la

massima frequenza di funzionamento del circuito la quale è di

147.05 MHz.

Page 9 of 10

6 Semaforo attraverso le macchine a stati

6.1 Schema

6.2 Descrizione SEM_MACHINE

Page 10 of 10