DISPENSE DI

SISTEMI ELETTRONICI PROGRAMMABILI

Parte I

Richiami di Elettronica Digitale

Andrea Del Re

SOMMARIO

CAPITOLO 1 – Sistemi Combinatori e Sequenziali ...........................................................................3

1.1 Introduzione ...................................................................................................................................3

1.2 Sistemi combinatori e sequenziali..................................................................................................3

1.3 Macchine a stati finiti.....................................................................................................................5

CAPITOLO 2 – Registri, Contatori e Memorie...................................................................................6

2.1 Introduzione ...................................................................................................................................6

2.2 Registri ...........................................................................................................................................6

2.2.1 Registro parallelo ....................................................................................................................6

2.2.2 Registro a scorrimento (shift-register) ....................................................................................7

2.3 Contatori ........................................................................................................................................8

2.3.1 Contatori modulo 2n ................................................................................................................8

2.3.2 Contatori modulo M≠2n ..........................................................................................................8

2.3.3 Contatori con conteggio decrescente ......................................................................................9

2.3.4 Circuiti ri-configurabili registro-contatore..............................................................................9

2.4 Random Access Memory (RAM) ................................................................................................10

2.4.1 RAM composte da più dispositivi.........................................................................................11

2.4.2 Singola cella di memoria.......................................................................................................12

2.4.3 RAM con bus dati separati....................................................................................................13

2.4.4 RAM con data bus singolo....................................................................................................14

2.4.5 Indirizzamento di memorie di grandi dimensioni .................................................................15

2.5 Register Files................................................................................................................................16

INDICE DELLE FIGURE

Figura 1: Esempio di circuito combinatorio ....................................................................................................................... 3

Figura 2: Esempio di circuito sequenziale .......................................................................................................................... 4

Figura 3: Simbolo di un Flip-Flop JK................................................................................................................................. 5

Figura 4: Registro a caricamento parallelo ......................................................................................................................... 6

Figura 5: Registro a caricamento parallelo con segnale di Load ........................................................................................ 7

Figura 6: Shift register ........................................................................................................................................................ 7

Figura 7: Shift register con uscita parallela ........................................................................................................................ 8

Figura 8: Contatore modulo 24............................................................................................................................................ 8

Figura 9: Contatore modulo 13........................................................................................................................................... 9

Figura 10: Contatore con conteggio decrescente ................................................................................................................ 9

Figura 11: Circuito che realizza un registro-contatore ri-configurabile............................................................................ 10

Figura 12: Schema a blocchi di una RAM 1024x8........................................................................................................... 11

Figura 13: Blocco RAM 256x8 realizzato con 4 dispositivi da 64x8 ............................................................................... 12

Figura 14: Schema di una singola cella di memoria statica .............................................................................................. 13

Figura 15: Schema di una RAM con BUS dati separati.................................................................................................... 13

Figura 16: Schema di una RAM con BUS dati singolo .................................................................................................... 14

Figura 17: Indirizzamento bi-dimensionale ...................................................................................................................... 15

Figura 18: Collegamento del register file alla ALU all'interno della CPU ....................................................................... 16

Figura 19: Schema a blocchi di un semplice Register File ............................................................................................... 17

INDICE DELLE TABELLE

Tabella 1: Funzioni di transizione di stato e funzioni di eccitazione per i diversi tipi di elementi memoria ...................... 4

Tabella 2 Modalità di funzionamento del registro-contatore.............................................................................................. 9

Tabella 3: Funzionamento della singola cella di memoria................................................................................................ 12

Tabella 4: Confronto tra la complessità dell'indirizzamento mono e bi-dimensionale ..................................................... 15

CAPITOLO 1 – Sistemi Combinatori e Sequenziali

1.1 Introduzione

Nei paragrafi seguenti vengono riportati alcuni richiami sui fondamenti dei circuiti logici. Lo

scopo è quello di stimolare il ricordo di concetti che dovrebbero essere già noti e di spingere a

rivedere quelle parti che dovessero essere fonte di dubbi.

Per questo motivo la seguente esposizione ha carattere fortemente sintetico, senza la pretesa di

essere completa. Per una trattazione più organica si rimanda ai libri di testo consigliati.

1.2 Sistemi combinatori e sequenziali

I circuiti logici digitali possono essere classificati come combinatori o sequenziali. Nei circuiti

combinatori, l’uscita del circuito è funzione solamente dei suoi ingressi correnti e il loro

comportamento può essere descritto usando tabelle di verità o espressioni booleane. Nella Figura 1

è riportato un esempio di circuito combinatorio (a) e della sua tabella di verità (b) ed espressione

booleana (c).

A

B’

Y

A’

B

A

0

0

1

1

B

0

1

0

1

(b)

Y

0

1

1

0

Y=AB’+A’B

(c)

(a)

Figura 1: Esempio di circuito combinatorio

Nei circuiti sequenziali, l’uscita è funzione, oltre che dei suoi ingressi correnti, anche di un

certo numero dei suoi ingressi precedenti. Il comportamento di un circuito sequenziale può essere

descritto utilizzando tabelle o diagrammi di stato o le funzioni di transizione di stato e di uscita. Lo

stato di un circuito sequenziale può essere pensato come la condizione nella quale il circuito si è

portato, partendo da determinate condizioni iniziali, a seguito della sequenza di ingressi ricevuta.

Nella Figura 2 è riportato un esempio di circuito sequenziale (a), della sua tabella di transizione di

stato (b), della sua funzione di transizione di stato (c) e del suo diagramma di stato (d). In questo

caso particolarmente semplice, lo stato e l’uscita coincidono e lo stesso vale, quindi, per le funzioni

di transizione di stato e d’uscita.

A

A

0

0

1

1

Y

PS (Y)

0

1

0

1

(a)

Y+ = A xnor Y

(c)

NS (Y+)

1

0

0

1

0

1

0

1

(b)

1

0

(d)

Figura 2: Esempio di circuito sequenziale

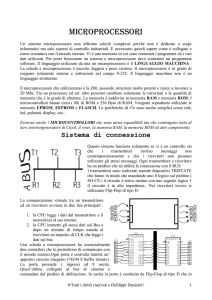

Il circuito di Figura 2 si comporta come un sistema sequenziale: a parità d’ingressi, infatti, la

sua uscita dipende dallo stato in cui il sistema si trova. L’elemento distintivo dei circuiti sequenziali

nei confronti di quelli combinatori è la presenza di elementi di memoria, che vengono realizzati

riportando le uscite di alcune porte logiche all’ingresso delle stesse o di altre porte. Così, un circuito

nella cui forma minima siano presenti questi loop è un circuito sequenziale.

I circuiti sequenziali possono esseri asincroni o sincroni. Nei circuiti asincroni gli ingressi

modificano il valore delle uscite del circuito in qualsiasi istante questi vengano applicati. Nei

circuiti sincroni, invece, il cambiamento di uno o più ingressi ha effetto sulle uscite solamente in

corrispondenza di alcuni istanti significativi, identificati attraverso un segnale solitamente indicato

come “clock”. Questo è un ingresso particolare del circuito, dall’andamento temporale tipicamente

periodico, che non altera la funzione logica realizzata, il cui compito è quello di segnare gli

intervalli di tempo durante il quale il circuito può evolvere, modificando la sua uscita ed il suo stato

in funzione dei suoi ingressi. I circuiti sincroni sono pensati in modo che l’uscita degli elementi di

memoria subisca al più una singola transizione per ogni periodo di clock.

Combinando opportunamente porte logiche e loop è possibile creare diversi elementi di

memoria (D, SR, JK, T), sensibili al livello (latches) o ad uno dei due fronti (di salita o di discesa)

del segnale di clock (Flip-Flop). Questi ultimi sono gli elementi di memoria solitamente utilizzati

nei circuiti sincroni.

Nella Tabella 1 sono riportate le funzioni di transizione di stato PS/NS e le funzioni di

eccitazione per i diversi tipi di elementi di memoria.

FF D

PS

0

1

D=0

0

0

FF T

D=1

1

1

PS

0

1

FF SR

T=0

0

1

NS

T=1

1

0

SR=00

0

1

NS

FF D

PS

0

1

PS

0

1

SR=01 SR=10

0

1

0

1

NS

FF T

NS=0

0

0

NS=1

1

1

D

PS

0

1

FF JK

SR=11

-

PS

0

1

JK=00

0

1

JK=01 JK=10

0

1

0

1

NS

FF SR

NS=0

0

1

NS=1

1

0

T

PS

0

1

NS=0

001

FF JK

NS=1

10

-0

SR

JK=11

1

0

PS

0

1

NS=0

0-1

NS=1

1-0

JK

Tabella 1: Funzioni di transizione di stato e funzioni di eccitazione per i diversi tipi di elementi memoria

Il simbolo di un Flip-Flop (FF) J/K è mostrato nella Figura 3. Oltre agli ingressi J e K ed al

segnale di clock, il FF prevede anche due segnali asincroni: il segnale di preset, che pone l’uscita ad

1 indipendentemente dal valore degli altri segnali, ed il segnale di clear, che pone l’uscita a 0

qualsiasi sia il valore degli altri segnali. Naturalmente, non ha senso porre ad 1

contemporaneamente i segnali preset e clear.

Clear

Preset

J

Q

FF

K

Q’

CLK

Figura 3: Simbolo di un Flip-Flop JK

1.3 Macchine a stati finiti

Un caso particolare di circuito sequenziale è rappresentato dalle macchine a stati finiti (Finite

State Machine). Come il nome stesso suggerisce, si tratta di circuiti sequenziali in cui il numero

degli stati è finito. A questa categoria appartengono tutti i circuiti che hanno una memoria limitata,

e alcuni di quelli con memoria infinita. Come esempio si consideri un circuito la cui funzione sia

quella di determinare se il numero di 1 ricevuti in ingresso dalla sua accensione al tempo t sia pari o

dispari; si tratta di un sistema con memoria infinita, ma con soli 2 stati (numero di 1 pari e numero

di 1 dispari). Il comportamento di una macchina a stati finiti è completamente identificato dalle

funzioni di transizione di stato e di uscita.

Le macchine a stati finiti possono essere descritte sia come macchine di Mealy che come

macchine di Moore. Per le macchine di Mealy, l'uscita è funzione dello stato presente e degli

ingressi:

S(t+1)=F[S(t),x(t)]

Y(t)=G[S(t),x(t)]

Per le macchine di Moore, l'uscita è funzione solamente dello stato presente:

S(t+1)=F[S(t),x(t)]

Y(t)=G[x(t)]

Sebbene la prima rappresentazione possa sembrare più generale, è possibile dimostrare che per ogni

macchina di Mealy ne esiste una di Moore equivalente.

CAPITOLO 2 – Registri, Contatori e Memorie

2.1 Introduzione

In questo capitolo verranno illustrati alcuni dei più comuni circuiti sequenziali utilizzati

nell’architettura dei calcolatori. In particolare, verranno trattati i registri, i contatori, i register-file e

la Random Access Memory (RAM).

2.2 Registri

Un registro è una sequenza di elementi di memoria ad 1 bit che sono utilizzati come una

singola unità di memoria. I registri sono utilizzati per immagazzinare dati temporanei per

l’elaborazione o la comunicazione tra due unità del calcolatore. Possono differire per dimensione,

modalità di scrittura e modalità di lettura.

2.2.1 Registro parallelo

In un registro a caricamento parallelo il contenuto degli elementi di memoria che lo compongono

viene immagazzinato in un unico colpo di clock. Un registro parallelo ad n-bit è un registro con n

ingressi, composto da n FF, ognuno dei quali ha il compito di registrare un bit della parola

d’ingresso. Di conseguenza, il contenuto del registro può essere letto in un unico colpo di clock. Un

esempio di un registro parallelo a 3 bit è riportato Figura 4.

I2

I1

I0

CLK

CLK

CLK

D

D

D

FF

FF

FF

Q

Q

Q

Out2

Out1

Out0

Figura 4: Registro a caricamento parallelo

Il circuito di Figura 5 ha un ulteriore ingresso “Load” che serve ad attivare o meno il

caricamento dei dati nel registro. Questo meccanismo è utile nel caso in cui nel nostro sistema siano

presenti più registri e non sia necessario aggiornarli tutti ad ogni colpo di clock. Di conseguenza, se

il segnale Load è alto, sul fronte di salita del clock l’ingresso di ogni flip-flop viene copiato sulla

sua uscita; al contrario, se Load è basso l’uscita rimane al valore precedente grazie al loop esterno ai

FF.

Load

I2

I1

I0

CLK

CLK

CLK

D

D

D

FF

FF

FF

Q

Q

Q

Out2

Out1

Out0

Figura 5: Registro a caricamento parallelo con segnale di Load

2.2.2 Registro a scorrimento (shift-register)

I registri a scorrimento sono utilizzati per scrivere nel registro un bit per volta. Possono essere

realizzati in modo da rendere disponibile in uscita un bit alla volta o tutti i bit in parallelo. Ad ogni

ciclo di clock i bit contenuti nel registro vengono spostati verso sinistra o verso destra (a seconda di

come sono posti in cascata i registri all’interno dello shift-register). Nella Figura 6 è riportato un

esempio di shift-register a 4 bit.

Input

D

Q

FF

D

Q

D

FF

Q

FF

D

Q

Out

FF

CLK

Figura 6: Shift register

Sul fronte di salita del clock l’ingresso è memorizzato nel FF più a sinistra e, allo stesso tempo,

i valori memorizzati in ogni FF vengono fatti scorrere verso il FF subito a destra. Per riempire il

registro saranno necessari, quindi, 4 cicli di clock. In maniera analoga, occorreranno 4 cicli di clock

per leggere il contenuto completo dello shift-register. Questo modificherà il contenuto del registro,

poiché ad ogni colpo di clock il segnale d’ingresso verrà fatto avanzare verso destra, prendendo il

posto dei dati registrati. Normalmente questo meccanismo è quello desiderato quando si utilizza uno

shift-register, ma in caso contrario si può provvedere a rendere disponibile le uscite in parallelo,

come mostrato nella Figura 7.

Y0

Input

D

Q

D

FF

CLK

Y1

Q

FF

Y2

D

Q

D

FF

Q

FF

Y3

Figura 7: Shift register con uscita parallela

2.3 Contatori

I contatori sono dei circuiti sequenziali la cui uscita segue una sequenza periodica

predeterminata. Se la sequenza di uscita corrisponde al conteggio binario si parla di contatori binari.

I contatori possono essere sincroni, nei quali tutti i flip-flop ricevono lo stesso segnale di clock,

oppure asincroni, dove questo non avviene. Noi tratteremo solamente contatori sincroni.

2.3.1 Contatori modulo 2n

Un contatore binario modulo m è un circuito sequenziale la cui uscita varia da 0 ad m-1, a passi

di 1, in modo periodico, ossia con lo 0 che segue il valore m-1. Se m=2n, il circuito può essere

realizzato utilizzando, come elementi di memoria, solo flip-flop di tipo T o JK. Infatti, osservando

la sequenza delle uscite, si può notare come il bit k-esimo venga modificato, da 0 a 1 e viceversa),

solo dopo che tutti i precedenti sono diventati 1. Quindi, l’ingresso del k-esimo FF sarà dato

dall’AND delle uscite di tutti i FF precedenti. Nella Figura 8 è riportato un esempio di un contatore

modulo 24.

COUNT

Q’

Y2

Q

Y1

J

K

Q

FF

J

Q’

Y0

FF

K

Q

Q’

J

Q’

FF

K

Q

FF

J

K

CLK

Y3

Figura 8: Contatore modulo 24

Un problema di questo circuito deriva dal fatto che il numero di porte AND collegate in cascata

cresce come il numero di bit, portando a dei ritardi nel calcolo dell’ingresso dell’ultimo FF che

potrebbero limitare pesantemente la massima frequenza di clock.

2.3.2 Contatori modulo M≠2n

Quando M non è una potenza di 2, il circuito che realizza il contatore può essere sintetizzato

utilizzando la classica procedura basata sulle mappe-K. In alternativa, è possibile sfruttare

l’ingresso clear asincrono, per azzerare l’uscita di tutti i FF quando si è raggiunto il massimo valore

per il conteggio. Nella Figura 9 è mostrato l’esempio di un contatore modulo 13.

COUNT

J

Q

Q’

Y1

FF C

K

Q

Q’

J

K

Q

Y0

FF C

J

Q’

FF C

K

Q

FF C

Q’

J

K

CLK

Y2

Y3

Figura 9: Contatore modulo 13

Si noti come il valore massimo dell’uscita sia mantenuto per un periodo di tempo molto limitato.

Questo perché tutti i FF vengono resettati non appena la condizione di fine conteggio rappresentata

dall’uscita della AND si propaghi fino all’ingresso Clear dei FF. La soluzione consiste nel rendere

sincrono l’azzeramento dei registri, con una struttura analoga a quella mostrata nella Figura 11.

2.3.3 Contatori con conteggio decrescente

In alcune situazioni può essere conveniente utilizzare un contatore che, ad ogni passo,

decrementi la sua uscita piuttosto che aumentarla. Questi contatori sono facilmente realizzabili

utilizzando l’uscita negata Q’ dei FF. Il risultato è mostrato nella Figura 10.

COUNT

Q’

J

K

Q

FF

J

Y1

Y2

Q

Q’

Y0

FF

K

Q

Q’

J

Q’

FF

K

Q

FF

J

K

CLK

Y3

Figura 10: Contatore con conteggio decrescente

2.3.4 Circuiti ri-configurabili registro-contatore

Utilizzando dei multiplexer è possibile realizzare dei circuiti che, a seconda del valore dei bit di

controllo, possa funzionare come un contatore o come un registro. Nel circuito di Figura 11 è

mostrato un circuito ri-configurabile che può funzionare in 4 diverse modalità, indicate nella

seguente tabella.

S1

0

0

1

1

S0

0

1

0

1

Funzionamento

Il contenuto dei registri non cambia

Gli ingressi I0…I3 vengono registrati

Conteggio crescente

Conteggio decrescente

Tabella 2 Modalità di funzionamento del registro-contatore

D

FF

Q

Out0

FF

Q

D

FF

D

D

Out1

Q

Out2

FF

Q

Out3

CLK

4 to 1

MUX

4 to 1

MUX

4 to 1

MUX

4 to 1

MUX

S1

S0

1

I3

I2

I1

I0

Figura 11: Circuito che realizza un registro-contatore ri-configurabile

Se i segnali di controllo sono pari a S1S0=00 l’uscita del registro viene riportata al suo ingresso

e, di conseguenza, l’uscita rimarrà invariata al fronte di clock successivo. Quando i segnali di

controllo sono pari a S1S0=01 gli ingressi I0…I3 vengono portati ai FF e la funzionalità del circuito è

pari a quella di un registro parallelo. Quando S1S0=10 il circuito assume la configurazione di un

contatore crescente, mentre con S1S0=11 quella di un contatore decrescente.

2.4 Random Access Memory (RAM)

La RAM è l’elemento di memoria utilizzato nel calcolatore per immagazzinare i dati e

programmi durante l’esecuzione di un programma. La memoria è divisa in parole (word), ovvero

l’insieme di locazioni di memoria che possono essere mosse da/verso la RAM come una singola

entità. Una parola è individuata attraverso il suo indirizzo (address) e caratterizzata dal suo

contenuto, ossia l’informazione effettivamente immagazzinata. Il nome deriva dal fatto che si può

accedere in maniera casuale ad una sequenza di parole mantenendo, approssimativamente, lo stesso

tempo di ritardo.

Nella Figura 12 è riportato lo schema a blocchi di una RAM di 1024 parole da 8 bit. In questo

caso la RAM è accessibile attraverso due data bus a 8 bit, uno d’ingresso e uno d’uscita, un address

bus a 10 bit, e segnali di chip select (CS) per l’abilitazione della RAM, e di read/write (R/W) per

l’abilitazione della scrittura sulla RAM.

8

Address BUS

10

CS

R/W

Data In BUS

1010111

Word 0

Word 1

RAM

Word 1023

8

Data Out BUS

Figura 12: Schema a blocchi di una RAM 1024x8

L’operazione di lettura è quella che permette di ottenere in uscita dalla RAM il contenuto di

una parola. Per far questo, occorre:

1. abilitare il blocco di RAM in questione ponendo ad 1 il segnale di chip select CS

2. fare una richiesta di lettura ponendo ad 1 (ma, a seconda dei casi può essere anche 0) il

segnale read/write R/W

3. mettere l’indirizzo corrispondente alla parola che si vuol leggere nell’address bus

L’operazione di scrittura permette di modificare il contenuto di una parola. Per far questo occorre:

1. abilitare il blocco di RAM in questione ponendo ad 1 il segnale di chip select CS

2. fare una richiesta di scrittura ponendo a 0 (ma, a seconda dei casi può essere anche 1) il

segnale read/write R/W

3. mettere la parola che si vuole scrivere sul data-in bus

4. mettere l’indirizzo della locazione in cui si vuol scrivere nell’address bus

2.4.1 RAM composte da più dispositivi

A causa di limitazioni fisiche legate ai processi tecnologici, il numero di parole contenute in un

singolo dispositivo RAM non può crescere a piacimento. Laddove sia necessario avere un numero

di parole maggiore di quello offerto dai singoli dispositivi, è possibile collegare più dispositivi in

modo da realizzare RAM più grandi. Nella Figura 13 è mostrato il circuito con il quale è possibile

costruire una RAM da 256 word x 8 bit utilizzando dei dispositivi con 64 word x 8 bit. I 2 bit più

significativi del bus indirizzi vengono utilizzati per stabilire quale dispositivo attivare, mentre i

restanti 6 indirizzano la parola. Inoltre, i bus d’uscita dei vari dispositivi sono collegati all’unico bus

dati verso la CPU, utilizzando dei buffer tristate, che vengono attivati dallo stesso decoder che

genera i CS.

Data_IN BUS

8

Address

BUS (5..0) 6

RAM 0

CS

RAM 1

CS

RAM 2

CS

RAM 3

CS

2x4

Decoder

Address

2 BUS (7..6)

CPU

Data_OUT

BUS

8

Figura 13: Blocco RAM 256x8 realizzato con 4 dispositivi da 64x8

2.4.2 Singola cella di memoria

Nella presente sezione verrà mostrata la realizzazione di una cella di RAM statica (SRAM), il

cui utilizzo è limitato a memorie di ridotte dimensioni e ad elevate prestazioni. L'alternativa è

rappresentata dalla RAM dinamica (DRAM), che è la più utilizzata per la RAM di sistema dei PC,

essenzialmente per ragioni economiche, legate alla possibilità di un maggiore livello d'integrazione.

Il circuito di Figura 14 mostra lo schema di una singola cella di memoria SRAM.

In una RAM occorre essere in grado di indirizzare ogni singola cella e di indicare se si tratta di

una richiesta di lettura o scrittura. Per questo vengono utilizzati il segnale select e il segnale R/W.

Inoltre occorre poter abilitare l'uscita nel caso di operazione di lettura; per queso motivo è

necessario utilizzare il buffer tristate di uscita. In particolare, se select=0 si ha S=0 e R=0 (nessun

cambiamento nell'informazione immagazzinata nel FF) e l'uscita è disabilitata; se select=1 e R/W=0

si ha S=In ed R=In', in modo da avere Q(t+1)=In(t), e l'uscita è disabilitata; infine, se S=1 e

R/W=1, si ha ancora S=0 ed R=0, ma l'uscita è collegata al FF. Il funzionamento è riassunto nella

Tabella 3, mettendo in evidenza il comportamento della cella di memoria.

S

0

1

1

R/W

X

0

1

Q(t+1)

Q

In

Q

Out

Floating

Floating (scrittura)

Q (lettura)

Tabella 3: Funzionamento della singola cella di memoria

R/W

Select

S

IN

Q

ENB

FF

R

Q’

Figura 14: Schema di una singola cella di memoria statica

2.4.3 RAM con bus dati separati

Per una memoria con 2n parole, ognuna di m bit, occorrono 2n⋅m celle da 1 bit. Per la selezione

di una parola si utilizza un decoder n⋅2n che abilita tutte le celle che formano la parola in esame.

Nella Figura 15 è mostrato un esempio di una RAM composta da 4 parole, ognuna di 3 bit; i blocchi

indicati con MC corrispondono ad 1 bit di memoria, del tipo indicato in Figura 14.

Data IN BUS (2..0)

MC

MC

MC

MC

MC

MC

MC

MC

MC

MC

MC

MC

CS

ADDR_1

ADDR_0

2x4

Decoder

R/W

Data OUT BUS (2..0)

Figura 15: Schema di una RAM con BUS dati separati

Il segnale di CS è collegato all'enable del decoder, in modo che quando CS=0, le uscite del

decoder sono tutte a 0, e nessuna cella di memoria risulta selezionata.

2.4.4 RAM con data bus singolo

Per ridurre il numero di linee necessarie per collegare la CPU alle periferiche, ottenendo un

beneficio in termini di complessità e costi, molto spesso le RAM utilizzate nella pratica hanno un

solo bus dati bi-direzionale. Questo può essere ottenuto utilizzando dei buffer tristate, come

illustrato nella Figura 16. I buffer sono comandati dal segnale R/W in modo da collegare il bus dati

alle celle di memoria durante una scrittura e l'uscita delle celle al bus dati durante una lettura.

MC

MC

MC

MC

MC

MC

MC

MC

MC

MC

MC

MC

CS

ENB

R/W

ENB

ADDR_0

2x4

Decoder

ENB

ADDR_1

Data BUS (2..0)

Figura 16: Schema di una RAM con BUS dati singolo

2.4.5 Indirizzamento di memorie di grandi dimensioni

Un singolo chip di RAM può eccedere i 256 Mbit di dimensione e non è praticamente

realizzabile un'indirizzamento basato su un unico decoder, soprattutto per questioni legate al ritardo

che un componente tanto complesso introdurrebbe nel circuito. Utilizzando un indirizzamento bidimensionale è possibile ridurre sensibilmente la complessità del decoder. Con questa tecnica, le

celle di memoria sono organizzate su una griglia, ed il singolo elemento viene individuato

attraverso la divisione del bus indirizzi in 2 parti, una delle quali identifica la riga e l'altra la colonna

delle celle di memoria MC. Nella Figura 17 è mostrato il funzionamento dell'indirizzamento.

Address

BUS

Indirizzo della

Colonna

Decoder

di Colonna

Indirizzo

della Riga

Parola

Indirizzata

Decoder

di Riga

Figura 17: Indirizzamento bi-dimensionale

La complessità dei decoder riga e colonna è molto minore di quella del decoder singolo: infatti,

se l'address bus è composto da 10 bit avremo bisogno di un decoder 10x1024, mentre utilizzando un

indirizzamento bi-direzionale si scende a 2 decoder da 5x32. Nella Tabella 4 è mostrato il numero

di mintermini necessario nei 2 casi al variare della grandezza del bus indirizzi.

Dimensioni di ADDR BUS

2

4

10

20

1 Decoder

4

16

1024

1M

Numero di mintermini

2 Decoder

4

8

64

2048

Tabella 4: Confronto tra la complessità dell'indirizzamento mono e bi-dimensionale

2.5 Register Files

I register files sono una particolare forma di memoria che può essere utilizzata all’interno delle

CPU. Si tratta essenzialmente di un insieme di registri con un bus d’ingresso e due di uscita,

tipicamente collegati alla ALU, come mostrato nella Figura 18.

Output BUS

REGISTER

FILE

Output BUS

ALU

Input BUS

Figura 18: Collegamento del register file alla ALU all'interno della CPU

Nella Figura 19 è riportato lo schema di un register file semplificato, composto da soli 2 registri

di 2 bit ognuno. I dati all’ingresso del register file vengono memorizzati in un certo registro quando

il relativo segnale di load è alto, altrimenti il contenuto rimane invariato. Per selezionare su quale

bus d’uscita collocare i dati provenienti dai registri vengono utilizzati due decoder, uno per ogni

bus, che abilitano i relativi buffer tristate. Naturalmente, il contenuto di uno stesso registro può

essere posto in uscita sui 2 bus contemporaneamente.

Bus Select A

Bus Enable A

Bus Select B

Bus Enable B

1x2

Decoder

1x2

Decoder

B0

B1

A0

A1

Q

D

FF

Q

R00

D

FF

D

D

FF

Q

R01

FF

R10

Q

R11

CLK

2 to 1

MUX

I1

2 to 1

MUX

Load 1

2 to 1

MUX

I0

Figura 19: Schema a blocchi di un semplice Register File

2 to 1

MUX

Load 0