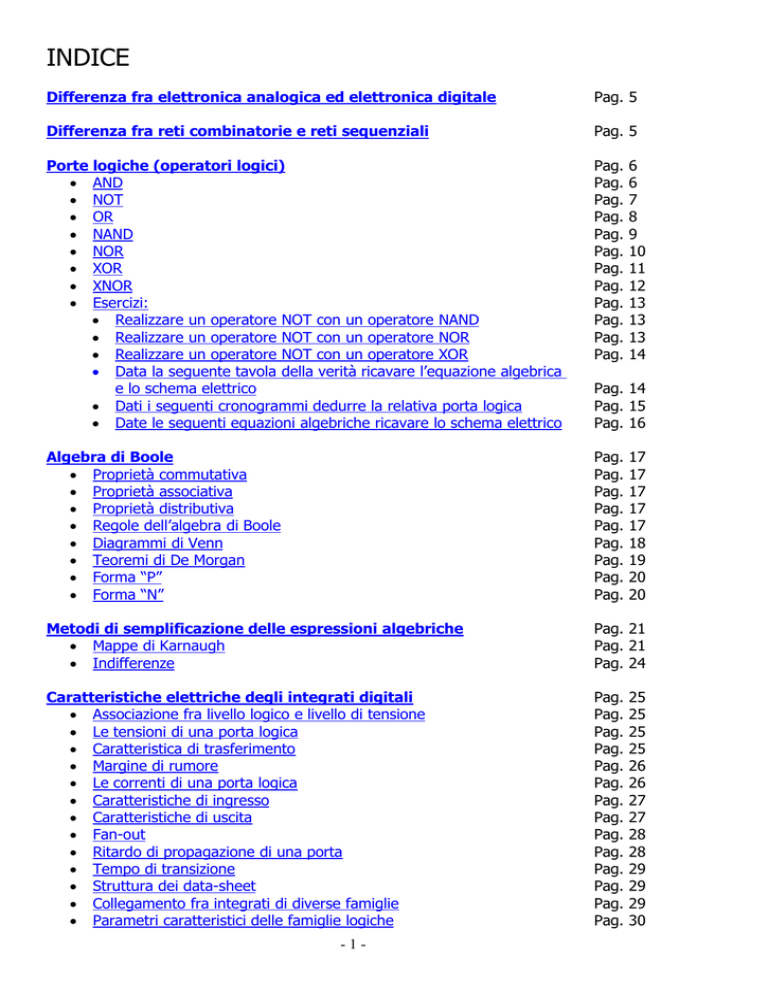

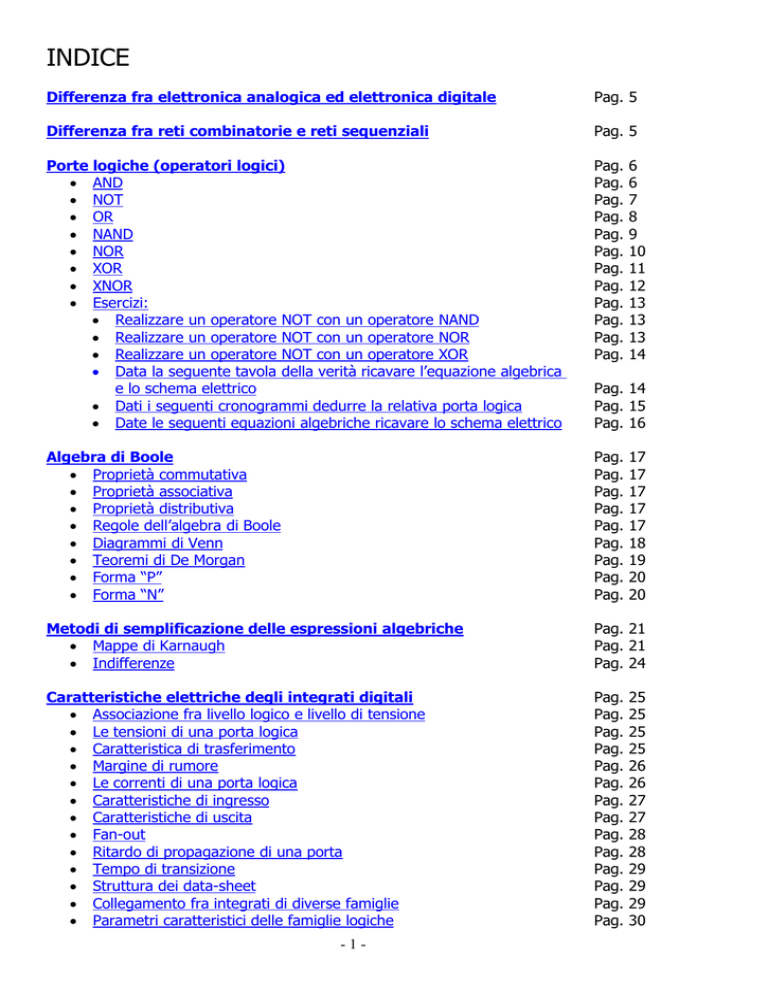

INDICE

Differenza fra elettronica analogica ed elettronica digitale

Pag. 5

Differenza fra reti combinatorie e reti sequenziali

Pag. 5

Porte logiche (operatori logici)

AND

NOT

OR

NAND

NOR

XOR

XNOR

Esercizi:

Realizzare un operatore NOT con un operatore NAND

Realizzare un operatore NOT con un operatore NOR

Realizzare un operatore NOT con un operatore XOR

Data la seguente tavola della verità ricavare l’equazione algebrica

e lo schema elettrico

Dati i seguenti cronogrammi dedurre la relativa porta logica

Date le seguenti equazioni algebriche ricavare lo schema elettrico

Pag.

Pag.

Pag.

Pag.

Pag.

Pag.

Pag.

Pag.

Pag.

Pag.

Pag.

Pag.

Algebra di Boole

Proprietà commutativa

Proprietà associativa

Proprietà distributiva

Regole dell’algebra di Boole

Diagrammi di Venn

Teoremi di De Morgan

Forma “P”

Forma “N”

Pag.

Pag.

Pag.

Pag.

Pag.

Pag.

Pag.

Pag.

Pag.

Metodi di semplificazione delle espressioni algebriche

Mappe di Karnaugh

Indifferenze

Pag. 21

Pag. 21

Pag. 24

Caratteristiche elettriche degli integrati digitali

Associazione fra livello logico e livello di tensione

Le tensioni di una porta logica

Caratteristica di trasferimento

Margine di rumore

Le correnti di una porta logica

Caratteristiche di ingresso

Caratteristiche di uscita

Fan-out

Ritardo di propagazione di una porta

Tempo di transizione

Struttura dei data-sheet

Collegamento fra integrati di diverse famiglie

Parametri caratteristici delle famiglie logiche

Pag.

Pag.

Pag.

Pag.

Pag.

Pag.

Pag.

Pag.

Pag.

Pag.

Pag.

Pag.

Pag.

Pag.

-1-

6

6

7

8

9

10

11

12

13

13

13

14

Pag. 14

Pag. 15

Pag. 16

17

17

17

17

17

18

19

20

20

25

25

25

25

26

26

27

27

28

28

29

29

29

30

Tipologie di uscite di una porta logica

Uscite a totem pole

Uscite a open collector drain

Pag. 32

Pag. 32

Pag. 32

Decodifica

Esercizi

Decoder 74138

Esercizi:

o Realizzare una decodifica a 4 ingressi usando il decoder 74128

o Realizzare una decodifica a 5 ingressi usando il decoder 74128

o Realizzare una decodifica a 6 ingressi usando il decoder 74128

Pag.

Pag.

Pag.

Pag.

Pag.

Pag.

Pag.

33

33

37

40

40

40

41

Multiplexer

Esercizi

o Progettare un multiplexer con 1 ingresso di selezione

o Progettare un multiplexer con 2 ingressi di selezione

o Progettare un multiplexer con 3 ingressi di selezione

Pag.

Pag.

Pag.

Pag.

Pag.

42

42

42

43

43

Demultiplexer

Esercizi

o Progettare un demultiplexer con 1 ingresso di selezione

o Progettare un demultiplexer con 2 ingressi di selezione

o Progettare un demultiplexer con 3 ingressi di selezione

Pag.

Pag.

Pag.

Pag.

Pag.

45

45

45

46

46

Encoder

Progettare un encoder per rappresentare sul display a 7 segmenti

i numeri compresi fra 0 e 9

Pag. 48

Diodo

Pag. 51

Led (light emitter diode)

Esercizi

Pag. 53

Pag. 53

Transistor

Guadagno statico di corrente hfe

Caratteristica d’ingresso del transistor bjt

Caratteristica d’uscita del transistor bjt

Condizioni per l’utilizzo del transistor in zona attiva

Condizioni per l’utilizzo del transistor in saturazione

Condizioni per l’utilizzo del transistor in interdizione

Esercizi

Pag.

Pag.

Pag.

Pag.

Pag.

Pag.

Pag.

Pag.

Trigger di schmitt

Pag. 60

Operatori 3-state

Esercizio

Pag. 61

Pag. 62

Transceiver

Pag. 63

Latch set-reset

Esercizio: realizzare l’antirimbalzo di un pulsante utilizzando un latch

-2-

Pag. 64

Pag. 66

Pag. 48

55

56

56

57

57

57

58

58

Flip-flop

Flip-flop D

Flip-flop JK

Pag. 67

Pag. 67

Pag. 67

Contatori asincroni

Contatore asincrono per 2

Contatore asincrono per 4

Pag. 68

Pag. 68

Pag. 69

Shift register

Pag. 70

Automi

Termini generali riguardanti la progettazione di un automa

Procedura per la progettazione di un automa

Esercizi:

o Progettare un contatore per 2 con ingresso di abilitazione tale

che se E = 0 il contatore si ferma nello stato in cui si trova.

o Progettare un contatore per 2 con ingresso di abilitazione tale

che se E = 0 il conteggio ritorna al primo stato.

o Progettare un contatore per 4 tale che se E = 0 il conteggio

ritorna a 0 0.

o Progettare un contatore per 4 up and down tale che se E = 0

il conteggio ritorna a 0 0.

o Progettare un contatore per 4 con ingresso di abilitazione tale

che se E = 0 il contatore si ferma nello stato in cui si trova.

o Progettare un contatore per 3 tale che se E = 0 il conteggio

ritorna a 0 0.

o Progettare un contatore per 3 up and down tale che se E = 0

il conteggio si ferma nello stato in cui si trova.

o Progettare un contatore per 3 tale che se C = 0 il conteggio

ha la sequenza 00, 01, 10; se C = 1 il conteggio ha la sequenza

00, 11, 10.

Pag.

Pag.

Pag.

Pag.

Carica di un condensatore

Pag. 86

Multivibratori

Pag. 88

Esercitazioni di laboratorio

Prova porte logiche

Prova decodifica a 2 ingressi

Linea mux-demux

Codificatori integrati (74LS147; 74LS148)

Decoder per display a 7 segmenti

Realizzazione di porte logiche not e nor con transistor

Rilevamento caratteristica di trasferimento di un trigger di schmitt

Realizzazione di un latch set-reset e di un circuito antirimbalzo

Verifica delle funzionalitá degli integrati 74LS73 e 73LS74 e

realizzazione di un contatore asincrono e divisore di frequenza per 2.

Realizzare un contatore asincrono per 4

Realizzazione di contatori sincroni per 3

Progetto giochi di luce

Pag.

Pag.

Pag.

Pag.

Pag.

Pag.

Pag.

Pag.

Pag.

90

90

94

95

96

98

100

104

107

Pag.

Pag.

Pag.

Pag.

109

117

119

126

-3-

71

71

71

72

Pag. 72

Pag. 73

Pag. 74

Pag. 76

Pag. 78

Pag. 80

Pag. 82

Pag. 84

Verifiche:

1° compito

2° compito

3° compito

4° compito

5° compito

6° compito

7° compito

8° compito

9° compito

10° compito

Pag.

Pag.

Pag.

Pag.

Pag.

Pag.

Pag.

Pag.

Pag.

Pag.

Pag.

-4-

130

130

134

136

137

139

142

144

146

149

152

DIFFERENZA FRA ELETTRONICA ANALOGICA ED

ELETTRONICA DIGITALE

ELETTRONICA ANALOGICA: l’elettronica analogica tratta segnali continui nel tempo (variano

con continuità).

ELETTRONICA DIGITALE: l’elettronica digitale tratta invece segnali discontinui nel tempo

(elabora numericamente le informazioni). Questi segnali possono assumere due stati: 0 (può

essere vero o falso) e 1 (può essere vero o falso, ma opposto a 0).

DIFFERENZA FRA RETI COMBINATORIE

E RETI SEQUENZIALI

RETI COMBINATORIE: le uscite del circuito all’istante di tempo “t” dipendono unicamente dal

valore degli ingressi allo stesso istante di tempo “t” (a meno di un ritardo della rete stessa).

RETI SEQUENZIALI: le uscite del circuito all’istante del tempo “t” dipendono dagli ingressi al

tempo “t”, ma anche da ciò che è successo nella rete prima dell’istante di tempo “t” (memoria del

passato).

-5-

PORTE LOGICHE (OPERATORI LOGICI)

Le porte logiche sono i circuiti combinatori più semplici tramite i quali si possono realizzare tutte le

funzioni logiche più complesse assemblando opportunamente questi componenti.

AND

La porta AND funziona secondo la seguente regola: l’uscita y deve essere VERA se l’ingresso A è

VERO e contemporaneamente l’ingresso B è VERO.

TAVOLA DELLA VERITÁ:

EQUAZIONE ALGEBRICA: y = A B

SCHEMA ELETTRICO:

A

0

0

1

1

SIMBOLO ELETTRICO:

CRONOGRAMMA:

NOT

-6-

B

0

1

0

1

Y

0

0

0

1

La porta NOT funziona secondo la seguente regola: l’uscita y è complementare all’ingresso A.

TAVOLA DELLA VERITÁ:

A Y

0 1

1 0

EQUAZIONE ALGEBRICA: y = /A

SCHEMA ELETTRICO:

SIMBOLO ELETTRICO:

CRONOGRAMMA:

OR

La porta OR funziona secondo la seguente regola: l’uscita y deve essere VERA se l’ingresso A è

VERO oppure l’ingresso B è VERO.

TAVOLA DELLA VERITÁ:

-7-

A

0

0

1

1

B

0

1

0

1

Y

0

1

1

1

EQUAZIONE ALGEBRICA: y = A + B

SCHEMA ELETTRICO:

SIMBOLO ELETTRICO:

CRONOGRAMMA:

NAND

La porta NAND funziona secondo la seguente regola: l’uscita y è FALSA solo se tutti gli ingressi

sono VERI.

TAVOLA DELLA VERITÁ:

A B Y

0 0 1

-8-

0

1

1

1

0

1

1

1

0

EQUAZIONE ALGEBRICA: y = /(A B)

SCHEMA ELETTRICO:

SIMBOLO ELETTRICO:

CRONOGRAMMA:

NOR

La porta NOR funziona secondo la seguente regola: l’uscita y è FALSA se almeno un ingesso è

VERO.

TAVOLA DELLA VERITÁ:

A B Y

0 0 1

0 1 0

-9-

1

1

0

1

0

0

EQUAZIONE ALGEBRICA: y = /(A +B)

SCHEMA ELETTRICO:

SIMBOLO ELETTRICO:

CRONOGRAMMA:

XOR

La porta XOR funziona secondo la seguente regola: l’uscita y è VERA se i due ingressi sono diversi.

TAVOLA DELLA VERITÁ:

A

0

0

1

1

B

0

1

0

1

EQUAZIONE ALGEBRICA: y = /A B + A /B = A

- 10 -

Y

0

1

1

0

B

SCHEMA ELETTRICO:

SIMBOLO ELETTRICO:

CRONOGRAMMA:

XNOR

La porta XNOR funziona secondo la seguente regola: l’uscita y è VERA se i due ingressi sono

uguali.

TAVOLA DELLA VERITÁ:

A

0

0

1

1

B

0

1

0

1

EQUAZIONE ALGEBRICA: y = /A /B + A B = /(A

SCHEMA ELETTRICO:

- 11 -

Y

1

0

0

1

B)

SIMBOLO ELETTRICO:

CRONOGRAMMA:

Esercizi:

1) Realizzare un operatore NOT con un operatore NAND.

Y = /(A B)

Y = /A

Quanto deve essere B?

Se B = A → Y = /(A A) = /A

Se B = 1 → Y = /(A 1) = /A

- 12 -

2) Realizzare un operatore NOT con un operatore NOR.

Y = /(A + B)

Y = /A

Quanto deve essere B?

Se B = A → Y = /(A + A) = /A

Se B = 0 → Y = /(A + 0) = /A

3) Realizzare un operatore NOT con un operatore XOR.

Y = /A B + A /B = A

Y = /A

Quanto deve essere B?

Se B = 1 → Y = /A 1 + A 0 = /A

- 13 -

B

4) Data la seguente tavola della verità ricavare l’equazione algebrica e lo schema

elettrico.

INPUTS OUTPUT

A B C

L

0 0 0

0

0 0 1

0

0 1 0

0

0 1 1

1

1 0 0

0

1 0 1

1

1 1 0

0

1 1 1

1

A, B, C = 0 → INTERRUTTORE APERTO

A, B, C = 1 → INTERRUTTORE CHIUSO

L = 0 → LAMPADA SPENTA

L = 1 → LAMPADA ACCESA

L = /A B C + A /B C + A B C = (A + B) C

- 14 -

5) Dati i seguenti cronogrammi dedurre la relativa porta logica.

La relativa porta logica è la seguente:

La relativa porta logica è la seguente:

6) Date le seguenti equazioni algebriche ricavare lo schema elettrico.

Y = B [ C (/A + D) + A]

- 15 -

Y = (AB + AC) D + /ACD

- 16 -

ALGEBRA DI BOOLE

PROPRIETÁ COMMUTATIVA

A+B=B+A

AB=BA

PROPRIETÁ ASSOCIATIVA

A + B + C = (A + B) + C = A + (B + C)

A B C = (A B) C = A (B C)

PROPRIETÁ DISTIBUTIVA

A (B + C) = A B + A C

A + B C = (A + B) (A + C)

REGOLE DELL’ALGEBRA DI BOOLE

A+0=A

A +1 = 1

A0=0

A1=A

A+A=A

A + /A = 1

AA=A

A /A = 0

//A = A

A + AB = A

A + /AB = A + B

DIAGRAMMI DI VENN

- 17 -

I diagrammi di Venn sono le rappresentazioni grafiche sottoforma dell’insiemistica dell’equazioni

algebriche di una data funzione logica.

Y=A

Y = /A

Y=B

Y = /B

Y=AB

Y = /(A B)

Y=A+B

Y = /(A+B)

Y=A

Y = /(A B)

B

- 18 -

TEOREMI DI DE MORGAN

/(AB) = /A + /B

La parte verde del primo diagramma è uguale a tutta la parte colorata del secondo diagramma (i

colori azzurro e giallo sono da considerarsi parte del risultato essendo una somma-unione).

Ciò è visibile in modo migliore tramite la tavola delle verità:

A

0

0

1

1

B /(A B) /A /B /A + /B

0

1

1

1

1

1

1

1

0

1

0

1

0

1

1

1

0

0

0

0

/(A + B) = /A /B

La parte verde del primo diagramma è uguale a alla parte verde del secondo diagramma (i colori

azzurro e giallo non sono da considerarsi parte del risultato essendo una moltiplicazioneintersezione).

Ciò è visibile in modo migliore tramite la tavola delle verità:

A

0

0

1

1

B /(A + B) /A /B /A /B

0

1

1

1

1

1

0

1

0

0

0

0

0

1

0

1

0

0

0

0

- 19 -

FORMA “P”

La forma P di una funzione è una scrittura algebrica della funzione in cui compaiono solo prodotti

logici di qualunque lunghezza posti ad OR fra loro. I prodotti logici avvengono fra mintermini che

contengono in forma vera o negata tutte le variabili della tavola della verità. Per ricavare le

equazioni dalle tavole delle verità basta considerare gli 1 come VERI.

Una volta ottenuta la forma P dell’equazione, è importante, per semplificare la questione, avere la

forma minima ovvero la soluzione semplificata dell’equazione.

Es.

A

0

0

1

1

B

0

1

0

1

Y

1

0

0

1

Questa tavola della verità espressa in forma P sarà: y = /A /B + A B

FORMA “N”

La forma N di una funzione è una scrittura algebrica della funzione in cui compaiono solo somme

logiche di qualunque lunghezza posti ad AND fra loro. Le somme logiche avvengono fra

maxtermini che contengono in forma vera o negata tutte le variabili della tavola della verità. Per

ricavare le equazioni dalle tavole delle verità basta considerare gli 0 come VERI.

Una volta ottenuta la forma N dell’equazione, è importante, per semplificare la questione, avere la

forma minima ovvero la soluzione semplificata dell’equazione.

Es.

A

0

0

1

1

B

0

1

0

1

Y

1

0

0

1

Questa tavola della verità espressa in forma N sarà: y = (A + /B) (/A + B)

- 20 -

METODI DI SEMPLIFICAZIONE DELLE

ESPRESSIONI ALGEBRICHE

MAPPE DI KARNAUGH

Si tratta di una rappresentazione grafica dei maxtermini di una funzione booleana realizzata in

modo da avere caselle adiacenti fra loro.

Una casella è adiacente ad un’altra quando cambia una sola variabile (hanno un lato in comune,

ma non solo)

1) Mappa di Karnaugh ad una sola variabile

A 0 1

/A A

2) Mappa di Karnaugh a due variabili

A

0

1

B 0

1

/A /B /A B

A /B A B

3) Mappa di Karnaugh a tre variabili

A

0

1

BC

0 0

0 1

1

1

1

0

/A /B /C /A /B C /A B C /A B /C

A /B /C A /B C A B C A B /C

4) Mappa di Karnaugh a quattro variabili

AB

00

01

11

10

CD

0 0

0 1

1

1

1

0

/A /B /C /D /A /B /C D /A /B C D /A /B C /D

/A B /C /D /A B /C D /A B C D /A B C /D

A B /C /D A B /C D A B C D A B C /D

A /B /C /D A /B /C D A /B C D A /B C /D

5) Mappa di Karnaugh a cinque variabili

E

CD

0 0

0

0 1

1

1

1

- 21 -

0

CD

0 0

1

0 1 1

1 1

0

AB

00

01

11

10

/A/B

/C/D/E

/AB

/C/D/E

AB

/C/D/E

A/B

/C/D/E

/A/B

/CD/E

/AB

/CD/E

AB

/CD/E

A/B

/CD/E

/A/B

CD/E

/AB

CD/E

AB

CD/E

A/B

CD/E

AB

00

/A/B

C/D/E

/AB

C/D/E

AB

C/D/E

A/B

C/D/E

01

11

10

/A/B

/C/DE

/AB

/C/DE

AB

/C/DE

A/B

/C/DE

/A/B

/CDE

/AB

/CDE

AB

/CDE

A/B

/CDE

/A/B

CDE

/AB

CDE

AB

CDE

A/B

CDE

/A/B

C/DE

/AB

C/DE

AB

C/DE

A/B

C/DE

Esempi:

1) Mappa di Karnaugh ad una sola variabile

A 0 1

1 0

Y = /A

2) Mappa di Karnaugh a due variabili

A

0

1

Y = /A /B + A B

B 0 1

1 0

0 1

3) Mappa di Karnaugh a tre variabili

A

0

1

BC 00 01 11 10

0

1

0

0

1

1

0

0

Y = /A B C + A /B /C + A B C

4) Mappa di Karnaugh a quattro variabili

AB

00

01

11

10

CD 00 01 11 10

0

0

0

0

0

0

0

1

1

1

0

1

0

0

0

0

Y = /A /B C D + /A B C D + A /B /C D + A /B C D

Y = /A C D + A /B D

In due caselle adiacenti cambia una sola variabile, ciò significa che se posso rappresentarle

(entrambe contengono 1) la variabile che cambia sparisce.

Es.

- 22 -

A

0

0

1

1

A

0

1

Y=A+B

B

0

1

0

1

Y

0

1

1

1

B 0 1

0 1

1 1

Es.

A

0

1

BC 00 01 11 10

1

1

1

1

0

0

1

1

Y = /B + /C

Es.

AB

00

01

11

10

CD 00 01 11 10

0

0

0

1

1

0

1

1

1

0

1

1

0

0

0

1

Y = A D + /B D + A /B

Es.

AB

00

01

11

10

CD 00 01 11 10

1

1

1

1

0

1

1

0

0

1

1

0

0

0

0

0

Y = /C /D + B D

Es.

AB

00

01

11

CD 00 01 11 10

1

0

1

0

1

0

- 23 -

0

0

0

1

0

0

10

1

0

0

1

Y = /C /D + /B D

INDIFFERENZE

Si ha un’indifferenza quando ad una combinazione d’ingressi non corrisponde uno stato definito 0

o 1 e che quindi per il rilevamento dell’equazioni algebriche si può considerare 0 o 1 a nostro

compiacimento. Vengono indicate spesso con una X o con un trattino.

Es.

AB

00

01

11

10

Y = A B + /A /B + /A D = /(A

CD 00 01 11 10

X

X

1

0

B) + /A D

- 24 -

X

X

1

0

1

1

1

0

1

0

1

0

CARATTERISTICHE ELETTRICHE DEGLI

INTEGRATI DIGITALI

ASSOCIAZIONE FRA LIVELLO LOGICO E LIVELLO DI TENSIONE

I livelli logici alto e basso (1 e 0) corrispondono ad un valore di tensione che cambia a seconda del

tipo di logica usata: RTL, TTL, CMOS, LVTTL, HCMOS, ECL, PECL.

Convenzionalmente si associa il livello BASSO allo 0 logico e il livello ALTO all’1 logico per la logica

positiva, mentre per la logica negativa il livello BASSO è associato all’1 logico e il livello ALTO allo

0 logico.

LE TENSIONI DI UNA PORTA LOGICA

CARATTERISTICA DI TRASFERIMENTO

La caratteristica di trasferimento di una porta logica è la curva che mette in relazione la tensione

di uscita con la tensione di un ingresso, tenendo gli altri ingressi ad un livello di tensione fisso.

-CARATTERISTICA DI TRASFERIMENTO DI UNA PORTA NOT

Quando la tensione d’ingresso è prossima allo 0, la tensione di uscita è riconosciuta come livello

logico alto in quanto si mantiene ad un valore pressoché fisso superiore alla VOHmin. Al crescere

della tensione d’ingresso la tensione di uscita diminuisce gradualmente fino ai valori per cui è

considerata livello logico basso (inferiore alla VOLmax). Per identificare i confini fra le tre zone che

si possono riconoscere (ALTA, banda proibita, BASSA), per convenzione si assumono i due punti

per cui la tangente alla caratteristica ha un’inclinazione di -45°. Bisogna comunque dire che la

caratteristica di trasferimento varia a seconda del carico, della temperatura, dalla qualità della

porta, per questo si fa riferimento ad una fascia entro la quale sono contenute tutte le

caratteristiche e dalla quale si ricavano i valori caratteristici VOHmin, VOHmax, VOLmin, VOLmax.

VOHmin: valore minimo della tensione di uscita riconosciuto come livello logico ALTO

VOLmax: valore massimo della tensione di uscita riconosciuto come livello logico BASSO

VIHmin: valore minimo della tensione d’ingresso riconosciuto come livello logico ALTO

VILmax: valore massimo della tensione d’ingresso riconosciuto come livello logico BASSO

- 25 -

MARGINE DI RUMORE

Il margine di rumore è la differenza fra VOHmin e VIHmin oppure la differenza fra VILmax e VOLmax

e sono il primo riferito al livello ALTO e il secondo al livello BASSO.

LE CORRENTI DI UNA PORTA LOGICA

Convenzionalmente i costruttori indicano col segno positivo le correnti entranti e col segno

negativo le correnti uscenti.

CARATTERISTICHE DI INGRESSO

La caratteristica d’ingresso di una porta logica è una curva che mette in relazione la corrente di

ingresso e la tensione d’ingresso. Come la caratteristica di trasferimento la caratteristica di

ingresso varia a seconda delle condizioni di utilizzo e per questo si fa riferimento ad una fascia

entro la quale sono contenute tutte le caratteristiche di ingresso e dalla quale si ricavano i valori

caratteristici IIHmax e IILmin.

IIHmax: valore massimo della corrente che può essere da un ingresso pilotato a livello ALTO

IILmin: valore minimo della corrente che può essere erogato da un ingresso pilotato a livello

BASSO

- 26 -

CARATTERISTICHE DI USCITA

La caratteristica di uscita di una porta logica è una curva che mette in relazione la corrente di

uscita e la tensione di uscita. La caratteristica di uscita a livello ALTO è una curva che mette in

relazione la corrente di uscita e la tensione di uscita, quando l’uscita si trova a livello ALTO. La

caratteristica di uscita a livello BASSO è una curva che mette in relazione la corrente di uscita e la

tensione di uscita, quando l’uscita si trova a livello BASSO.

IOHmax: valore massimo della corrente erogabile da un uscita pilotata a livello logico ALTO

IOLmax: valore massimo della corrente assorbibile da un uscita pilotata a livello logico BASSO

FAN-OUT

Il fan-out è il numero massimo di ingressi pilotabili da una sola uscita in condizioni di

sicurezza ed è il minore fra i due seguenti rapporti: IOHmax / IIHmin ; IOLmax / IILmin.

- 27 -

RITARDO DI PROPAGAZIONE DI UNA PORTA

Convenzionalmente il tempo di ritardo è definito come il tempo che intercorre fra l’istante

in cui il segnale d’ingresso raggiunge il 50% della sua variazione e l’istante in cui il segnale

di uscita raggiunge il 50% della sua variazione. Esistono quindi due tipi di ritardi: quello

per la transizione da livello logico ALTO a livello logico BASSO (tPHL) e quello per la

transizione da livello logico BASSO a livello logico ALTO (tPLH).

TEMPO DI TRANSIZIONE

Il tempo di transizione di un segnale è il tempo che intercorre fra il 10% e il 90% del

campo di variazione del segnale stesso. Esistono quindi due tipi di tempi di transizione:

quello di salita per il passaggio da livello BASSO a livello ALTO e quello di discesa per il

passaggio da livello ALTO a livello BASSO.

STRUTTURA DEI DATA-SHEET

Un data-sheet è costituito essenzialmente da quattro parti:

1. absolute maximum rating (LIMITI MASSIMI TOLLERATI): in questa parte sono

riportati i valori di alcune grandezze che stabiliscono i limiti massimi di utilizzo oltre i

- 28 -

quali l’integrato può subire danni irreversibili. Fra queste grandezze ci sono la

tensione di alimentazione Vcc (supplì voltage), la tensione massima d’ingresso

(input voltage), le temperature di lavoro (operating free-air temperature range) e le

temperature di conservazione (storage temperature range).

2. recommended operatine conditions (CONDIZIONI DI LAVORO

RACCOMANDATE): in questa parte sono riportati i valori minimi, tipici e massimi

raccomandati di alcune grandezze per il corretto utilizzo dell’integrato. Fra queste

grandezze ci sono la tensione di alimentazione, la temperatura di lavoro, la corrente

di uscita riconosciuta come livello basso e come livello alto.

3. elettrical characteristics (CARATTERISTICHE ELETTRICHE): in questa parte

sono descritti i parametri di funzionamento dell’integrato e i suoi limiti. I parametri

descritti per valori minimi, massimi e tipici in questa sezione sono: VIH, VIL, VIK, VOH,

VOL, II, IIH, IIL, IOS, ICC.

4. swiching characteristics (CARATTERISTICHE DI COMMUTAZIONE): in questa

parte sono riportati i valori tipici e massimi dei due tipi di ritardi di commutazione

(tPHL, tPLH).

COLLEGAMENTO FRA INTEGRATI DI DIVERSE FAMIGLIE

Solitamente i livelli di tensione di ingresso e di uscita sono dipendente dalla tensione di

alimentazione: è per questo necessario che i due integrati di diverse famigli per essere

collegati opportunamente debbono essere alimentati con la stessa tensione. Le altre

tensioni limite devono rispettare le seguenti condizioni:

VOHmin (1) > VIHmin (2)

VOLmax (1) < VILmax (2)

IOHmax (1) ≥ IIHmax (2)

IOLmax (1) ≥ IILmin (2)

(1) = porta pilota; (2) = porta di carico

Qualora non fosse possibile il collegamento diretto sarà necessario introdurre un circuito di

interfaccia.

PARAMETRI CARATTERISTICI DELLE FAMIGLIE LOGICHE

-CONNESSIONE DIRETTA CON FAMIGLIE LOGICHE DIVERSE

Se la connessione diretta con famiglie logiche è consentita non sarà necessario utilizzare

circuiti di interfaccia e questo rende più semplice e meno costoso l’impiego dell’integrato.

-DISTURBI GENERATI INTERNAMENTE

Una minore generazione di disturbi all’interno del componente rende più sicuro il

funzionamento di una rete in quanto questi si propagano più difficilmente lungo i

collegamenti con altri dispositivi.

-IMMUNITÁ AL RUMORE

- 29 -

Un componente è immune al rumore quando è in grado a operare in presenza di disturbi

elettrici esterni.

-POTENZA DISSIPATA

Minore è la potenza dissipata per porta, minore sarà il consumo elettrico e maggiore la

durata delle batterie per l’alimentazione (se alimentato a batterie), meno sarà dissipato

calore.

-COSTO

Il costo di un componente non è da valutare solo nella sua valuta, ma anche considerando

il costo del montaggio, di progettazione e altri fattori.

-FATTORE DI QUALITÁ

Il fattore di qualità è il prodotto fra il ritardo di propagazione espresso in nanosecondi e la

potenza dissipata per porta espressa in milliWatt ed esprime il compromesso esistente fra

queste due grandezze per una migliore velocità di commutazione.

-REPERIBILITÁ

Se un componente è reperibile sul mercato con facilità e a distanza di tempo, è possibile

effettuare progetti destinati alla produzione con più sicurezza.

-VELOCITÁ DI COMMUTAZIONE

Maggiore è la velocità di comunicazione e maggiori saranno le operazioni eseguibili

nell’unità di tempo; è solitamente espressa in ritardi di propagazione.

-DISPONIBILITÁ DI FUNZIONI COMPLESSE

Se un componente dispone di funzioni complesse saranno necessari meno componenti per

la realizzazione di un’intera rete e quindi sarà anche più facile il montaggio.

- 30 -

TIPOLOGIE DI USCITE DI UNA PORTA LOGICA

In generale le uscite di una porta logica possono essere di due tipi:

USCITE A TOTEM POLE

Non è possibile collegare due uscite totem pole altrimenti si creerebbero dei conflitti che

non sono altro che cortocircuiti.

USCITE A OPEN COLLECTOR DRAIN

- 31 -

DECODIFICA

Una decodifica è una rete combinatoria con n ingressi e 2n uscite mutuamente esclusive

fra loro, ciò significa che in corrispondenza di una combinazione di ingressi risulta attiva

una ed una sola uscita.

Esercizi:

1) Progettare un decoder con 2 ingressi e uscite attive a livello logico alto.

A

0

0

1

1

Y0

Y1

Y2

Y3

=

=

=

=

B Y0 Y1 Y2 Y3

0 1

0

0

0

1 0

1

0

0

0 0

0

1

0

1 0

0

0

1

/A /B

/A B

A /B

A B

- 32 -

2) Progettare un decoder con 3 ingressi e con un ulteriore ingresso di abilitazione (E)

tale che se E=0 le uscite sono tutte inattive ovvero tutte a 1. Altresì la decodifica è

libera di operare (uscite attive a 0).

A

X

0

0

0

0

1

1

1

1

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

=

=

=

=

=

=

=

=

B

X

0

0

1

1

0

0

1

1

C

X

0

1

0

1

0

1

0

1

E Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7

0 1

1

1

1

1

1

1

1

1 0

1

1

1

1

1

1

1

1 1

0

1

1

1

1

1

1

1 1

1

0

1

1

1

1

1

1 1

1

1

0

1

1

1

1

1 1

1

1

1

0

1

1

1

1 1

1

1

1

1

0

1

1

1 1

1

1

1

1

1

0

1

1 1

1

1

1

1

1

1

0

A + B + C +/E

A + B + /C +/E

A + /B + C +/E

A + /B + /C +/E

/A + B + C +/E

/A + B + /C +/E

/A + /B + C +/E

/A + /B + /C +/E

- 33 -

3) Progettare una decodifica con 3 ingressi e uscite attive basse. Esiste anche un

ingresso “E” e un “/G” tali che se E=0 e /G indifferente le uscite sono disattive e

viceversa se /G=1 ed E indifferente le uscite sono ancora disattive.

A

X

X

X

0

0

0

0

1

1

1

1

B

X

X

X

0

0

1

1

0

0

1

1

C

X

X

X

0

1

0

1

0

1

0

1

E /G Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7

0 0

1

1

1

1

1

1

1

1

0 1

1

1

1

1

1

1

1

1

1 0

1

1

1

1

1

1

1

1

1 1

0

1

1

1

1

1

1

1

1 1

1

0

1

1

1

1

1

1

1 1

1

1

0

1

1

1

1

1

1 1

1

1

1

0

1

1

1

1

1 1

1

1

1

1

0

1

1

1

1 1

1

1

1

1

1

0

1

1

1 1

1

1

1

1

1

1

0

1

1 1

1

1

1

1

1

1

1

0

- 34 -

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

=

=

=

=

=

=

=

=

A + B + C +/E + /G

A + B + /C +/E + /G

A + /B + C +/E + /G

A + /B + /C +/E + /G

/A + B + C +/E + /G

/A + B + /C +/E + /G

/A + /B + C +/E + /G

/A + /B + /C +/E + /G

- 35 -

DECODER 74138

Il decoder 74138 è una rete di decodifica costituita da 3 ingressi e quindi 8 uscite attive a

livello logico basso, ma anche da altri 3 ingressi di abilitazione che funzionano secondo la

seguente tavola della verità:

A

X

X

X

0

0

0

0

1

1

1

1

B

X

X

X

0

0

1

1

0

0

1

1

C

X

X

X

0

1

0

1

0

1

0

1

E /G1 /G2 /Y0 /Y1 /Y2 /Y3 /Y4 /Y5 /Y6 /Y7

0

X

X

1

1

1

1

1

1

1

1

X

1

X

1

1

1

1

1

1

1

1

X

X

1

1

1

1

1

1

1

1

1

1

0

0

0

1

1

1

1

1

1

1

1

0

0

1

0

1

1

1

1

1

1

1

0

0

1

1

0

1

1

1

1

1

1

0

0

1

1

1

0

1

1

1

1

1

0

0

1

1

1

1

0

1

1

1

1

0

0

1

1

1

1

1

0

1

1

1

0

0

1

1

1

1

1

1

0

1

1

0

0

1

1

1

1

1

1

1

0

/Y0

/Y1

/Y2

/Y3

/Y4

/Y5

/Y6

/Y7

=

=

=

=

=

=

=

=

A + B + C + /E + /G1 + /G2

A + B + /C + /E + /G1 + /G2

A + /B + C + /E + /G1 + /G2

A + /B + /C + /E + /G1 + /G2

/A + B + C + /E + /G1 + /G2

/A + B + /C + /E + /G1 + /G2

/A + /B + C + /E + /G1 + /G2

/A + /B + /C + /E + /G1 + /G2

- 36 -

=

=

=

=

=

=

=

=

/( /A /B /C

/( /A /B C

/( /A B /C

/( /A B C

/( A /B /C

/( A /B C

/( A B /C

/( A B C

E

E

E

E

E

E

E

E

G1

G1

G1

G1

G1

G1

G1

G1

G2)

G2)

G2)

G2)

G2)

G2)

G2)

G2)

- 37 -

- 38 -

Esercizi:

1) Realizzare una decodifica a 4 ingressi usando il decoder 74138.

2) Realizzare una decodifica a 5 ingressi usando il decoder 74138.

3) Realizzare una decodifica a 6 ingressi usando il decoder 74138.

- 39 -

- 40 -

MULTIPLEXER

Un multiplexer è una rete combinatoria con n ingressi di selezione, 2n ingressi di

dato e una sola uscita. L’uscita assume il valore dell’ingresso di dato selezionato dagli

ingressi di selezione.

Esercizi:

1) Progettare un multiplexer con 1 ingresso di selezione.

S0 z

0 I0

1 I1

z = /S0 I0 + S0 I1

se S0 = 0

se S0 = 1

z = /0 I0 + 0 I1 = I0

z = /1 I0 + 1 I1 = I1

- 41 -

2) Progettare un multiplexer con 2 ingressi di selezione.

S0 S1

0 0

0 1

1 0

1 1

z

I0

I1

I2

I3

z = /S0 /S1 I0 + /S0 S1 I1 + S0 /S1 I2 + S0 S1 I3

3) Progettare un multiplexer con 3 ingressi di selezione.

S0

0

0

0

0

1

1

1

1

S1

0

0

1

1

0

0

1

1

S2

0

1

0

1

0

1

0

1

z

I0

I1

I2

I3

I4

I5

I6

I7

z = /S0 /S1 /S2 I0 +/S0 /S1 S2 I1 + /S0 S1 /S2 I2 + /S0 S1 S2 I3 + S0 /S1 /S2 I4 + S0 /S1 S2 I5 +

+S0 S1 /S2 I6 + S0 S1 S2 I7

- 42 -

- 43 -

DEMULTIPLEXER

Un demultiplexer è una rete combinatoria con n ingressi di selezione, 2n uscite e un

solo ingresso di dato. L’ingresso di dato assume il valore dell’uscita del multiplexer

selezionata dagli ingressi di selezione. Se devo trasmettere 2n informazioni ci vorrebbero

2n fili, che costano, allora se si utilizza una linea mux-demux ci si accontenta di avere le

informazioni una alla volta.

Esercizi:

1) Progettare un demultiplexer con 1 ingresso di selezione.

S0 O0 O1

0

I

0

1 0

I

O0 = /S0 I

O1 = S0 I

- 44 -

2) Progettare un demultiplexer con 2 ingressi di selezione.

S0 S1 O0 O1 O2 O3

0 0

I

0

0

0

0 1 0

I

0

0

1 0 0

0

I

0

1 1 0

0

0

I

O0

O1

O2

O3

=

=

=

=

/S0 /S1 I

/S0 S1 I

S0 /S1 I

S0 S1 I

3) Progettare un demultiplexer con 3 ingressi di selezione.

S0 S1 S2 O0 O1 O2 O3 O4 O5 O6 O7

0 0 0

I

0

0

0

0

0

0

0

0 0 1 0

I

0

0

0

0

0

0

0 1 0 0

0

I

0

0

0

0

0

0 1 1 0

0

0

I

0

0

0

0

1 0 0 0

0

0

0

I

0

0

0

1 0 1 0

0

0

0

0

I

0

0

1 1 0 0

0

0

0

0

0

I

0

1 1 1 0

0

0

0

0

0

0

I

- 45 -

O0

O1

O2

O3

O4

O5

O6

O7

=

=

=

=

=

=

=

=

/S0 /S1 /S2 I

/S0 /S1 S2 I

/S0 S1 /S2 I

/S0 S1 S2 I

S0 /S1 /S2 I

S0 /S1 S2 I

S0 S1 /S2 I

S0 S1 S2 I

- 46 -

ENCODER

Un encoder è una rete combinatoria con n ingressi e m uscite. Ad una combinazione degli

n ingressi corrisponde una ed una sola combinazione delle uscite.

Esercizio: Progettare un encoder per rappresentare sul display a 7 segmenti i numero

compresi fra 0 e 9.

D

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

C

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

B

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

A DGT a b c d e f g

0

0

1 1 1 1 1 1 0

1

1

0 1 1 0 0 0 0

0

2

1 1 0 1 1 0 1

1

3

1 1 1 1 0 1 0

0

4

0 1 1 0 0 1 1

1

5

1 0 1 1 0 1 1

0

6

1 0 1 1 1 1 1

1

7

1 1 1 0 0 0 0

0

8

1 1 1 1 1 1 1

1

9

1 1 1 1 0 1 1

0

//

X X X X X X X

1

//

X X X X X X X

0

//

X X X X X X X

1

//

X X X X X X X

0

//

X X X X X X X

1

//

X X X X X X X

- 47 -

a = B + D + /(A

b = D + C + /(A

c = /B + A + C

C)

B)

DC

00

01

11

10

DC

00

01

11

10

DC

00

01

11

10

BA 00 01 1 1 1 0

1

0

X

1

0

1

X

1

1

1

X

X

1

1

X

X

BA 00 01 1 1 1 0

1

1

X

1

1

0

X

1

1

1

X

X

1

0

X

X

BA 00 01 1 1 1 0

1

1

X

1

1

1

X

1

1

1

X

X

0

1

X

X

BA 00 01 1 1 1 0

DC

1

0

00

0

1

01

X

X

11

1

1

10

d = D + /C /A + B /A + /D /C B + C /B A

e = /A (/C + B)

DC

00

01

11

10

1

0

X

X

1

1

X

X

BA 00 01 1 1 1 0

1

0

X

1

0

0

X

0

0

0

X

X

1

1

X

X

BA 00 01 1 1 1 0

DC

1

0

1

0

00

1

1

0

1

01

X

X

X

X

11

1

1

X

X

10

f = /A /B + D + /B C + C /A + A B /C

- 48 -

g = D + C /B + B /A

DC

00

01

11

10

BA 00 01 1 1 1 0

0

1

X

1

0

1

X

1

- 49 -

0

0

X

X

1

1

X

X

DIODO

Un diodo è un dispositivo semiconduttore che consente il passaggio di corrente solo in un

verso, cioè nella direzione da anodo a catodo (A → K).

1a ipotesi: DIDO IDEALE

2a ipotesi:

- 50 -

3a ipotesi:

Nella realtà:

La Vγ è la tensione di soglia oltre la quale il diodo si considera in conduzione: per i diodi al

silicio vale circa 0,6 V; per i diodi al germanio vale circa 0,2 V.

La VBRK è la tensione di breakdown sotto la quale il diodo si rompe irreparabilmente

causando il cortocircuito del diodo stesso. Il valore di questa tensione varia a seconda del

tipo di componente

- 51 -

LED (LIGHT EMITTER DIODE)

Il diodo è un dispositivo semiconduttore che consente il passaggio di corrente solo in un

verso, cioè nella direzione da anodo a catodo. Il diodo LED funziona come un diodo

normale, ma se attraversato da corrente diretta, emette luce. La tensione Vγ vale,

orientativamente, 1,6V.

Esercizio: Calcolare le tensioni e le correnti del seguente circuito.

I1 0 A

V 1 V

10 0,6

9,216mA

R1 R 2 R3 100 100 820

I3 I 2

I2

V 1 R 2 I 2 100 9,216 10 3 0,9216V

V 2 R3 I 3 820 9,216 10 3 7,557V

- 52 -

Esercizio: calcolare R1 e R2 in modo che VAB = 9V sapendo che ILED = 10mA.

R2

V AB V LED 9 1,6

740

I LED

0,01

V AB V 9 0,6

8,4mA

R3

1000

V 1 V AB

10 9

R1

54,348

I LED I R 3 0,01 0,0084

I R3

Esercizio: calcolare R in modo che nel LED scorra una corrente pari a 20mA.

R

V 1 V LED 10 1,6

420

I LED

0,02

- 53 -

TRANSISTOR

Il transistor BJT (Bipolar Junction Transistor) è un dispositivo semiconduttore composto da

tre cristalli di semiconduttore drogati alternativamente di tipo “n” e di tipo “p”. Ciò significa

che ci sono due giunzioni: BASE- EMETTITORE (Je) e BASE-COLLETTORE (Jc). L’intensità

del drogaggio nelle varie zone è differente l’una dall’altra, per questo E e C non sono

intercambiabili.

Ci sono due particolarità costruttive essenziali affinché il BJT funzioni:

1. la regione di base deve essere molto sottile (pochi μm);

2. la zona di base deve essere poco drogata rispetto a quella dell’emettitore.

Nel transistor BJT, la corrente di base controlla la corrente di collettore: annullando la

corrente di base si impedisce il passaggio di corrente nel collettore, per cui il percorso

collettore-emettitore equivale ad un circuito aperto (interdizione); forzando nella base una

corrente sufficientemente grande, si ottiene il passaggio di corrente dal collettore

all’emettitore e l’abbassamento della tensione tra questi due terminali a valori prossimi allo

0 (saturazione), per cui il percorso collettore-emettitore equivale ad un corto circuito. Il

funzionamento di un transistor BJT è caratterizzato da un parametro detto guadagno

statico di corrente (hFE).

Il BJT funziona come amplificazione di corrente se viene utilizzato in zona attiva, oppure

può svolgere la funzione di interruttore elettronico se utilizzato in saturazione (ON) e in

interdizione (OFF).

- 54 -

Le equazioni caratteristiche di un transistor sono:

Ie Ib Ic

Ic Ie I 0

Ic

da0,99a0,999 amplificazione statica di corrente

Ie

Ic

h FE

guadagno statico di corrente

Ib 1

Ic h FE Ib (h FE 1) I 0

-GUADAGNO STATICO DI CORRENTE hFE

L’hFE è un parametro detto guadagno statico di corrente che dipende poco dalla tensione

Vce e maggiormente dalla corrente Ic, in base alla quale diminuisce sia per correnti molto

basse che per correnti alte, mentre per valori intermedi rimane pressoché costante. Con

l’aumento di Vce, e quindi della polarizzazione inversa Jc, la zona di transizione all’interno

della base poco drogata si estende, di conseguenza si riduce la larghezza della base utile

per le ricombinazioni e quindi un aumento di hFE. Questa modulazione della larghezza

della base al variare di Vce è detto effetto Early.

-CARATTERISTICA D’INGRESSO DEL TRANSISTOR BJT

La caratteristica d’ingresso rappresenta l’andamento della corrente d’ingresso Ib al variare

della tensione VBE, per valori costanti di VCE. In funzionamento lineare, le caratteristiche

tendono a non dipendere da VCE e per questo coincidono, diventando un’unica curva. La

tensione di soglia Vγ vale circa 0,5V, mentre è da evitare una polarizzazione in inversa

troppa elevata di Je che provoca la rottura della giunzione che è solitamente irreversibile.

Il valore di questa tensione va da 5 a 7V.

- 55 -

-CARATTERISTICA D’USCITA DEL TRANSISTOR BJT

La caratteristica d’uscita mette in relazione la corrente Ic con la tensione VCE per valori

costanti di Ib. Quando al tensione VCE assume valori superiori a pochi decimi di volt, le

caratteristiche appaiono ben distinte e possono essere quasi considerate orizzontali,

parallele ed equidistanti per uguali variazioni di Ib. Nella realtà, invece, Ic cresce

gradualmente all’aumentare di VCE e le curve tendono ad addensarsi sia verso l’alto sia

verso il basso. Per valori di VCE molto bassi il transistor è in saturazione, per valori di Ic

praticamente nulli il transistor è in interdizione, mentre per valori intermedi il transistor

lavora in zona attiva.

-CONDIZIONI PER L’UTILIZZO DEL TRANSISTOR IN ZONA ATTIVA

Ic h FE Ib

V BC 0

V BE V

VCE V BE

Vcc

2

Pdissipata VCE Ic

VCE

Ic(max)

P max

VCE

-CONDIZIONI PER L’UTILIZZO DEL TRANSISTOR IN SATURAZIONE

VCE V BE

IB

Ic

h FE

VCE ( sat ) da 0,1 a 0,3V

VBE (sat) da 0,75 a 0,8V

- 56 -

-CONDIZIONI PER L’UTILIZZO DEL TRANSISTOR IN INTERDIZIONE

VBE V

Ic I 0 0 A

Esercizio: determinare i valori di R1 e di R2 tenendo conto che ILED = 10mA e hFE = 100.

Se SW è aperto non si genera corrente di base e quindi il transistor è interdetto, ciò

significa che non scorrerà ne corrente di collettore e di conseguenza anche sull’emettitore.

Se SW è chiuso si genera una corrente di base che satura il transistor e permette il

passaggio della corrente di collettore.

I LED 1,2 0,01

120 A

hFE

100

V 1 VBE

5 0,6

R1

36, 6K

Ib

120 10 6

V 2 VLED VCE 10 1,6 0,2

R2

820

I LED

0,01

Ib 1,2

- 57 -

Esercizio: determinare i valore di R1 e di R2 tenendo conto che ILED = 20mA, hFE = 100;

Vγ = 0,6V; VCESAT = 0,2V; V1 = 10V; VBE = 0,6V; VLED = 1,6V.

I LED 1,2 0,02

240 A

hFE

100

Vcc 2V LED VCE V 10 3,2 0,2 0,6

R1

300

Ib

0,02

V 1 V V BE 10 0,6 0,6

R2

36, 6K

Ib

240 10 6

Ib 1,2

- 58 -

TRIGGER DI SCHMITT

Per eliminare gli elementi di incertezza nel riconoscimento dei segnali (i livelli dei segnali si

degradano assumendo valori lontani da quelli nominali, la forma di questi peggiora in

quanto i fronti di salita e discesa diventano lenti e non ben definiti) si sono realizzati

integrati con ingressi a trigger di Schmitt. Nella caratteristica di trasferimento di questi

integrati si nota che non esiste una zona di transizione, nella quale l’uscita passa

gradualmente da un livello ad un altro, bensì si osserva che i passaggi tra i livelli di uscita

avvengono in modo brusco in corrispondenza di due distinti valori della tensione d’ingresso.

Con tensione d’ingresso crescente si ha un cambio di livello quando viene raggiunto il

valore di tensione di soglia VTH+ , mentre con tensione d’ingresso decrescente la

variazione avviene in corrispondenza di un valore di soglia differente denominato VTH- . Il

raggiungimento di una tensione di soglia innesca un ciclo di funzionamento interno che,

una volta iniziato, non è più controllato dal segnale d’ingresso e si evolve in modo

autonomo spingendo l’uscita sul livello logico opposto a quello di partenza; la soglia VTH+

è sempre più alta della soglia VTH-.

CONSEGUENZE SULL’ANDAMENTO DEI SEGNALI IN USCITA:

Le variazioni in ingresso causate dai disturbi non provocano un andamento

oscillante dell’uscita in quanto sarebbero necessarie oscillazioni delle tensioni di

ingresso più ampie (glich) della differenza tra le due soglie (ISTERESI).

Il tempo impiegato per le transizioni tra i livelli non dipende dall’andamento del

segnale d’ingresso: infatti la transizione è governata da cicli interni che vengono

solo avviati al raggiungimento delle soglie.

- 59 -

OPERATORI 3-STATE

X

0

1

E Y

0 z

1 0

1 1

- 60 -

Esercizio: usando degli operatori 3 state e un’opportuna rete combinatoria per le

abilitazioni, realizzare un multiplexer a due ingressi di selezione.

E

0

0

1

1

F

0

1

0

1

A

1

0

0

0

B

0

1

0

0

- 61 -

C D

0 0

0 0

1 0

0 1

TRANSCEIVER

E D meaning G1 G2

0 z

z

z

1 0

A→B

1

0

1 1

B→A

0

1

- 62 -

LATCH SET-RESET

Il latch set reset è un dispositivo che permette, oltre che a scrivere un’informazione (0 o

1), di memorizzare l’informazione immessa.

Un lach set reset può essere costruito utilizzando porte NAND o porte NOR.

Un circuito si dice asincrono quando l'uscita si adegua allo stato degli ingressi senza

attendere il consenso di un segnale di sincronismo.

Un circuito si dice sincrono quando l'uscita si adegua allo stato degli ingressi solo

all'arrivo di un impulso di sincronismo.

Si dice clock un impulso di sincronismo in grado di stabilire l'istante preciso in cui i circuiti

devono commutare. Vi sono circuiti che commutano sul fronte di salita dell'impulso di clock,

oppure sul fronte di discesa dell'impulso di clock, oppure quelli che hanno bisogno

dell'intero impulso di clock per poter commutare. Gli ingressi di questi circuiti agiscono in

modo asincrono sui segnali di uscita: ogniqualvolta diventano attivi le uscite, trascorso il

tempo di ritardo di propagazione, commutano.

In un latch set-reset realizzato con porte NOR, se l’ingresso set (S) è attivo (1) e l’ingresso

di reset (R) è disattivo (0) l’uscita sarà condizionata a 1; se l’ingresso S è disattivo (0) e

l’ingresso di reset è attivo (1) l’uscita sarà condizionata a 0; se entrambi gli ingressi sono a

livello logico basso, l’uscita rimarrà quella che c’era nell’istante prima della commutazione;

se invece entrambi gli ingressi sono attivi, la condizione non è valida, cioè la due uscite Q

e /Q non sono più complementari.

S

0

0

1

1

R

0

1

0

1

Qn+1

Qn

0

1

Non ha senso

In un latch set-reset realizzato con porte NAND se l’ingresso di set (/S) è attivo (0) e

l’ingresso di reset (/R) è disattivo (1) l’uscita (Q) sarà condizionata a 1; se l’ingresso /S è

disattivo (1) e l’ingresso 7R è attivo (0) l’uscita (Q) sarà condizionata a 0; se entrambi gli

ingressi sono a livello logico alto, l’uscita rimarrà quella che c’era nell’istante prima della

commutazione; se invece entrambi gli ingressi sono attivi, la condizione non è valida, cioè

la due uscite Q e /Q non sono più complementari.

- 63 -

/S

0

0

1

1

/R

0

1

0

1

Qn+1

Non ha senso

1

0

Qn

Se /S e /R sono attivi contemporaneamente c’è un problema, per questo viene inserito un

altro ingresso (E) che se è uguale a 1 S*=/S e R*=/R, invece se è uguale a 0 S*=1 e

R*=1, ciò significa che viene memorizzata l’informazione precedente.

Prima dell’ingresso e si può inserire un sistema di porte che riescono a rilevare solo i fronti

di salita o di discesa, in modo che l’ingresso E cambi da 0 a 1 e viceversa. Il sistema così

ottenuto è un flip flop SR, più comunemente chiamato JK, con un clock, due ingressi (set e

reset) e due uscite che sono sempre complementari fra loro.

- 64 -

Esercizio: Realizzare l’antirimbalzo di un pulsante utilizzando un latch.

- 65 -

FLIP FLOP

I flip flop sono dei circuiti sequenziali analoghi ai latch S- R, tuttavia si differenziano

perché nei flip flop l'istante in cui avviene la commutazione delle uscite è stabilito con

certezza, e si evita il difetto della trasparenza; dove trasparenza vuol dire che l'uscita si

adegua immediatamente allo stato degli ingressi, non appena variano gli ingressi, ciò è un

difetto quando si vogliono circuiti perfettamente sincronizzati, nei quali gli istanti di

commutazione devono essere decisi con precisione.

FLIP-FLOP D

Un flip-flop di tipo D ha un ingresso, due uscite complementari e un ingresso di

sincronizzazione (clock). In corrispondenza del comando di clock, trasferisce l'ingresso in

uscita e lo mantiene fino al successivo fonte attivo di clock.

Equazione caratteristica: Q

n+1

= Dn

Tabella di verità:

D Q n+1

0

0

(reset)

1

1

(set)

FLIP-FLOP JK

Un flip-flop di tipo JK ha due ingressi, due uscite complementari e un ingresso di

sincronizzazione. Ha funzioni di memoria, reset, set . A differenza dei Flip Flpo SR non ha

stati proibiti, ovvero le due entrate posso assumere qualsiasi valore (0-0,0-1,1-0,1-1).

Equazione caratteristica: Q

n+1

= /Qn Jn + Qn /Kn

Tabella di verità:

J

0

0

1

1

K

0

1

0

1

CK

Q n+1

Fronte attivo Q n (nessun cambiamento)

Fronte attivo

0

(reset)

Fronte attivo

1

(set)

Fronte attivo /Q n

(complemento)

- 66 -

CONTATORI ASINCRONI

I contatori asincroni sono divisori di frequenza la cui uscita si adegua allo stato degli

ingressi senza attendere il consenso di un segnale di sincronismo.

-CONTATORE ASINCRONO PER 2

- 67 -

-CONTATORE ASINCRONO PER 4

- 68 -

SHIFT REGISTER

I registri a scorrimento (SHIFT REGISTER) sono dei registri adatti a lavorare in forma

seriale e lo scorrimento dei dati (bit) presuppone l’utilizzo di memorie a cascata (è

possibile utilizzare anche dei flip-flop.

- 69 -

AUTOMI

TERMINI GENERALI RIGUARDANTI LA PROGETTAZIONE DI UN AUTOMA

b) Grafo: rappresentazione grafica di come avvengono le transizioni entro un automa;

c) Automa: macchina in grado di fare tutto ciò per cui è stata progettata in modo

ripetitivo e per un tempo indefinito;

d) Stati: condizioni nelle quali si trova un automa;

e) Transizioni: passaggio da uno stato ad un altro avvenuto in seguito ad una certa

condizione sugli ingressi;

S0

S1

f) Autoanelli: transizioni verso lo stesso stato;

S0

g) Variabile di stato: è una variabile (può assumere due valori) usata per

rappresentare gli stati di un automa, costruita utilizzando un flip flop. Con una sola

variabile di stato si possono rappresentare 2 stati, con due 4 stati, con tre 8 stati, e

così via.

PROCEDURA PER LA PROGETTAZIONE DI UN AUTOMA

1) Si disegna il GRAFO ricavato dalle specifiche del problema;

2) INDIVIDUATI GLI STATI si procede alla CODIFICA degli stessi (associare un

numero univoco a ciascun stato presente sul grafo);

3) Si costruisce la TABELLA DI TRANSIZIONE DEGLI STATI (rappresenta gli stati futuri

in relazione alla situazione presente);

4) Si ottiene, usando la codifica, la mappa relativa a ciascuna variabile di stato;

5) Si sceglie il flip flop da usare e in base a quello si ottiene l’equazione risolutiva per

ciascun flip flop

- 70 -

Esercizi:

1. Progettare un contatore per 2 con ingresso di abilitazione tale che se E =

0 il contatore si ferma nello stato in cui si trova.

1) GRAFO

2) CODIFICA DEGLI STATI

S0 0

S1 1

3) RILEVAMENTO EQUAZIONE DEGLI INGRESSI DEL F-F D

Q0

0

1

n

Q0

En 0 1

0 1

1 0

n+1

= Q0n

En

4) RILEVAMENTO EQUAZIONE DEGLI INGRESSI DEL F-F JK

Q0

0

1

n

E

n

Q0n

0

1

0 1

0 1

1 0

J0 = En

K0 = En

Q0n

0

1

- 71 -

En

0 1

0 1

X X

J0 n+1

En 0 1

X X

0 1

K0 n+1

2. Progettare un contatore per 2 con ingresso di abilitazione tale che se

E = 0 il conteggio ritorna al primo stato.

1) GRAFO

2) CODIFICA DEGLI STATI

S0 0

S1 1

3) RILEVAMENTO EQUAZIONE DEGLI INGRESSI DEL F-F D

Q0n

0

1

Q0

En 0 1

0 1

0 0

n+1

= /Q0n En

4) RILEVAMENTO EQUAZIONE DEGLI INGRESSI DEL F-F JK

Q0

0

1

n

E

n

Q0

0

1

n

0 1

0 1

0 0

J0 = En

K0 = 1

Q0

0

1

n

- 72 -

En

0 1

0 1

X X

J0 n+1

En 0 1

X X

1 1

K0 n+1

3. Progettare un contatore per 4 tale che se E = 0 il conteggio ritorna a 0 0.

1) GRAFO

2) CODIFICA DEGLI STATI

S0

S1

S2

S3

0

0

1

1

0

1

0

1

3) RILEVAMENTO EQUAZIONE DEGLI INGRESSI DEL F-F D

Q1 Q0

0

0

0

1

1

1

1

0

n

E

n

Q1n Q0n

0

0

0

1

1

1

1

0

Q1

Q0

n+1

n+1

0

1

0

0

0

0

0

0

0

0

= E (Q1

= /Q0n En

n

n

0

1

0

1

1

0

0

1

Q0 )

n

n

Q1n Q0n

0

0

0

1

1

1

1

0

En 0 1

0 0

0 1

0 0

0 1

Q1 n+1

En 0 1

0 1

0 0

0 0

0 1

Q0 n+1

4) RILEVAMENTO EQUAZIONE DEGLI INGRESSI DEL F-F JK

- 73 -

E

n

Q1n Q0n

0

0

0

1

1

1

1

0

Q1n Q0n

0

0

0

1

1

1

1

0

0 1

0 0

0 1

0 0

0 1

Q1 n+1

Q1 Q0

0

0

0

1

1

1

1

0

n

J1 = E Q0

K1 = /En + Q0n

n

n

E

n

Q1n Q0n

0

0

0

1

1

1

1

0

n

Q1n Q0n

0

0

0

1

1

1

1

0

0 1

0 1

0 0

0 0

0 1

Q0 n+1

Q1 Q0

0

0

0

1

1

1

1

0

n

J0 = En

K0 = 1

En 0 1

- 74 -

n

En 0 1

0 0

0 1

X X

X X

J1 n+1

En 0 1

X X

X X

1 1

1 0

K1 n+1

0 1

X X

X X

0 1

J0 n+1

En 0 1

X X

1 1

1 1

X X

K0 n+1

4. Progettare un contatore per 4 up and down tale che se E = 0 il conteggio

ritorna a 0 0.

1) GRAFO

2) CODIFICA DEGLI STATI

S0

S1

S2

S3

0

0

1

1

0

1

0

1

3) RILEVAMENTO EQUAZIONE DEGLI INGRESSI DEL F-F D

Q1n Q0n

0

0

0

1

1

1

1

0

Q1n Q0n

0

0

0

1

1

1

1

0

En UDn 0 0 0 1 1 1 1 0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

1

1

0

0

1

1

0

1

0

1

0

0

1

Q1 Q0

0

0

0

1

1

1

1

0

n

Q1

Q0

n+1

n+1

= E /((UD

= /Q0n En

n

n

(Q1

n

Q0 )

n

- 75 -

n

En UDn 0 0 0 1 1 1 1 0

0

0

0

0

0

0

0

0

0

1

0

1

Q1

1

0

1

0

n+1

En UDn 0 0 0 1 1 1 1 0

0

0

0

0

0

0

0

0

1

0

0

1

Q0

1

0

0

1

n+1

4) RILEVAMENTO EQUAZIONE DEGLI INGRESSI DEL F-F JK

Q1 Q0

0

0

0

1

1

1

1

0

n

E UD

n

Q1n Q0n

0

0

0

1

1

1

1

0

J1

K1

n+1

n+1

00 01 11 10

0

0

0

0

= E /(Q0

= En /(Q0n

Q1 Q0

0

0

0

1

1

1

1

0

n

n

n

n

0

0

0

0

0

1

0

1

1

0

1

0

Q1n Q0n

0

0

0

1

1

1

1

0

UD )

UDn) + /En

n

n

Q1n Q0n

0

0

0

1

1

1

1

0

En UDn 0 0 0 1 1 1 1 0

0

0

0

0

0

0

0

0

1

0

0

1

n

1

0

0

1

Q1 Q0

0

0

0

1

1

1

1

0

n

J0 n+1 = En

K0 n+1 = 1

- 76 -

n

En UDn 0 0 0 1 1 1 1 0

0

0

X

X

0

0

X

X

0

1

X

X

J1

1

0

X

X

n+1

En UDn 0 0 0 1 1 1 1 0

X

X

1

1

X

X

1

1

X

X

1

0

K1

X

X

0

1

n+1

En UDn 0 0 0 1 1 1 1 0

0

X

X

0

0

X

X

0

1

X

X

1

J0

1

X

X

1

n+1

En UDn 0 0 0 1 1 1 1 0

X

1

1

X

X

1

1

X

X

1

1

X

K0

X

1

1

X

n+1

5. Progettare un contatore per 4 con ingresso di abilitazione tale che se

E = 0 il contatore si ferma nello stato in cui si trova.

1) GRAFO

2) CODIFICA DEGLI STATI

S0

S1

S2

S3

0

0

1

1

0

1

0

1

3) RILEVAMENTO EQUAZIONE DEGLI INGRESSI DEL F-F D

E

n

Q1 Q0

0

0

0

1

1

1

1

0

n

Q1

Q0

n+1

n+1

n

0

0

0

1

1

Q1n Q0n

0

0

0

1

1

1

1

0

1

0

1

1

0

0

1

0

1

1

0

0

1

= Q1 /E + E (Q1

= Q0n

En

n

n

n

n

Q1n Q0n

0

0

0

1

1

1

1

0

Q0 )

n

- 77 -

En 0 1

0 0

0 1

1 0

1 1

Q1 n+1

En 0 1

0 1

1 0

1 0

0 1

Q0 n+1

4) RILEVAMENTO EQUAZIONE DEGLI INGRESSI DEL F-F JK

Q1 Q0

0

0

0

1

1

1

1

0

n

Q1n Q0n

0

0

0

1

1

1

1

0

En 0 1

0 0

0 1

1 0

1 1

Q1 n+1

Q1n Q0n

0

0

0

1

1

1

1

0

J1 = En Q0n

K1 = En Q0n

E

n

Q1 Q0

0

0

0

1

1

1

1

0

n

n

n

Q1n Q0n

0

0

0

1

1

1

1

0

0 1

0 1

1 0

1 0

0 1

Q0 n+1

Q1n Q0n

0

0

0

1

1

1

1

0

J0 = E

K0 = En

n

- 78 -

En 0 1

0 0

0 1

X X

X X

J1 n+1

En 0 1

X X

X X

0 1

0 0

K1 n+1

En 0 1

0 1

X X

X X

0 1

J0 n+1

En 0 1

X X

0 1

0 1

X X

K0 n+1

6. Progettare un contatore per 3 tale che se E = 0 il conteggio ritorna a 0 0.

1) GRAFO

2) CODIFICA DEGLI STATI

S0

S1

S2

S3

0

0

1

1

0

1

0

1

3) RILEVAMENTO EQUAZIONE DEGLI INGRESSI DEL F-F D

Q1 Q0

0

0

0

1

1

1

1

0

n

E

0

n

Q1n Q0n

0

0

0

1

1

1

1

0

Q1

Q0

n+1

n+1

0

0

0

0

1

0

0

0

0

0

1

0

0

1

0

0

0

Q1n Q0n

0

0

0

1

1

1

1

0

= /Q1 Q0 E

= /Q0n /Q1n En

n

n

n

n

- 79 -

En 0 1

0 0

0 1

0 0

0 0

Q1 n+1

En 0 1

0 1

0 0

0 0

0 0

Q0 n+1

4) RILEVAMENTO EQUAZIONE DEGLI INGRESSI DEL F-F JK

Q1 Q0

0

0

0

1

1

1

1

0

n

En 0 1

Q1n Q0n

0

0

0

1

1

1

1

0

0 0

0 1

0 0

0 0

Q1 n+1

Q1n Q0n

0

0

0

1

1

1

1

0

J1 = En Q0n

K1 = 1

E

0 1

n

Q1 Q0

0

0

0

1

1

1

1

0

n

n

Q1 Q0

0

0

0

1

1

1

1

0

n

0 1

0 0

0 0

0 0

Q0 n+1

J0 = /Q1 E

K0 = 1

n

n

n

n

Q1 Q0

0

0

0

1

1

1

1

0

n

- 80 -

n

En 0 1

0 0

0 1

X X

X X

J1 n+1

En 0 1

X X

X X

1 1

1 1

K1 n+1

En 0 1

0 1

X X

X X

0 0

J0 n+1

En 0 1

X X

1 1

1 1

X X

K0 n+1

7. Progettare un contatore per 3 up and down tale che se E = 0 il conteggio

si ferma nello stato in cui si trova.

1) GRAFO

2) CODIFICA DEGLI STATI

S0

S1

S2

S3

0

0

1

1

0

1

0

1

3) RILEVAMENTO EQUAZIONE DEGLI INGRESSI DEL F-F D

Q1n Q0n

0

0

0

1

1

1

1

0

Q1n Q0n

0

0

0

1

1

1

1

0

En UDn 0 0 0 1 1 1 1 0

0

0

0

1

0

1

0

0

0

0

0

1

0

1

0

0

0

1

0

0

1

0

0

0

1

0

0

0

0

0

0

1

Q1 Q0

0

0

0

1

1

1

1

0

n

Q1

n+1

Q0

n+1

= Q1 /Q0 /E +

/ Q1n En /(UDn

= /Q1n Q0n /En +

/ Q0n En (UDn

n

n

n

Q0n)

Q1n)

- 81 -

n

En UDn 0 0 0 1 1 1 1 0

0

0

0

1

0

0

0

1

0

1

0

0

Q1

1

0

0

0

n+1

En UDn 0 0 0 1 1 1 1 0

0

1

0

0

0

1

0

0

1

0

0

0

Q0

0

0

0

1

n+1

4) RILEVAMENTO EQUAZIONE DEGLI INGRESSI DEL F-F JK

Q1n Q0n

0

0

0

1

1

1

1

0

Q1n Q0n

0

0

0

1

1

1

1

0

En UDn 0 0 0 1 1 1 1 0

0

0

0

1

0

0

0

1

0

1

0

0

1

0

0

0

Q1 Q0

0

0

0

1

1

1

1

0

n

J1

K1

n+1

n+1

= E /(Q0

= Q0n + En

Q1n Q0n

0

0

0

1

1

1

1

0

n

UD )

n

n

Q1n Q0n

0

0

0

1

1

1

1

0

En UDn 0 0 0 1 1 1 1 0

J0 n+1 = En /(Q1n

K0 n+1 = En + Q1n

0

1

0

0

0

1

0

0

1

0

0

0

n

0

0

0

1

Q1 Q0

0

0

0

1

1

1

1

0

n

UDn)

- 82 -

n

En UDn 0 0 0 1 1 1 1 0

0

0

X

X

0

0

X

X

0

1

X

X

J1

1

0

X

X

n+1

En UDn 0 0 0 1 1 1 1 0

X

X

1

0

X

X

1

0

X

X

1

1

K1

X

X

1

1

n+1

En UDn 0 0 0 1 1 1 1 0

0

X

X

0

0

X

X

0

1

X

X

0

J0

0

X

X

1

n+1

En UDn 0 0 0 1 1 1 1 0

X

0

1

X

X

0

1

X

X

1

1

X

K0

X

1

1

X

n+1

8. Progettare un contatore per 3 tale che se C = 0 il conteggio ha la

sequenza 00, 01, 10; se C = 1 il conteggio ha la sequenza 00, 11, 10.

1) GRAFO

2) CODIFICA DEGLI STATI

S0

S1

S2

S3

0

0

1

1

0

1

0

1

3) RILEVAMENTO EQUAZIONE DEGLI INGRESSI DEL F-F D

C

0

n

Q1 Q0

0

0

0

1

1

1

1

0

n

Q1

Q0

n+1

n+1

n

0

1

0

0

Q1n Q0n

0

0

0

1

1

1

1

0

1

1

0

0

0

1

0

1

0

1

0

0

0

= /Q1 /Q0 C + Q0 /(Q1

= /Q0n /Q1n

n

n

n

n

n

Q1n Q0n

0

0

0

1

1

1

1

0

C)

n

- 83 -

Cn 0 1

0 1

1 0

0 1

0 0

Q1 n+1

Cn 0 1

1 1

0 0

0 0

0 0

Q0 n+1

4) RILEVAMENTO EQUAZIONE DEGLI INGRESSI DEL F-F JK

Q1 Q0

0

0

0

1

1

1

1

0

n

En 0 1

Q1n Q0n

0

0

0

1

1

1

1

0

0 1

1 0

0 1

0 0

Q1 n+1

Q1n Q0n

0

0

0

1

1

1

1

0

J1 = En

Q0n

K1 = /En + /Q0n

E

n

Q1 Q0

0

0

0

1

1

1

1

0

n

n

J0 = /Q1

K0 = 1

n

Q1n Q0n

0

0

0

1

1

1

1

0

0 1

1 1

0 0

0 0

0 0

Q0 n+1

Q1n Q0n

0

0

0

1

1

1

1

0

n

- 84 -

En 0 1

0 1

1 0

X X

X X

J1 n+1

En 0 1

X X

X X

1 0

1 1

K1 n+1

En 0 1

1 1

X X

X X

0 0

J0 n+1

En 0 1

X X

1 1

1 1

X X

K0 n+1

CARICA DI UN CONDENSATORE

Per definizione stessa di capacità

Q

C

V

la corrente I(t) per definizione è

Q

I (t )

t

ma, dalla legge do Ohm, si ha:

Vi (t ) Vo (t )

I (t )

R

per cui essendo ΔQ = I(t) Δt = C ΔVo

si ha

Vi (t ) Vo (t )

C Vo

t

R

ne segue che

Vo

1

(Vi (t ) Vo (t ))

t

RC

Vo

1

1

Vo (t )

Vi (t )

t

RC

RC

supposto che Vi(t) sia un gradino di ampiezza costante VM si ha

Vo

1

1

Vo (t )

t

RC

RC

Considerando Δt intervalli di tempo molto piccoli si può scrivere: Δt = (t n-t n-1) = costante

Vo (t n 1 ) Vo (t n )

1

1

Vo (t n )

t

RC

RC

quindi il valore della tensione ai capi del condensatore all’istante futuro (n+1) vale:

1

1

Vo (t n 1 ) (

Vo (t n )

) t Vo (t n )

RC

RC

- 85 -

Il grafico che ne consegue sarà quello della carica del condensatore ed è il seguente:

- 86 -

MULTIVIBRATORI