Technology Mapping

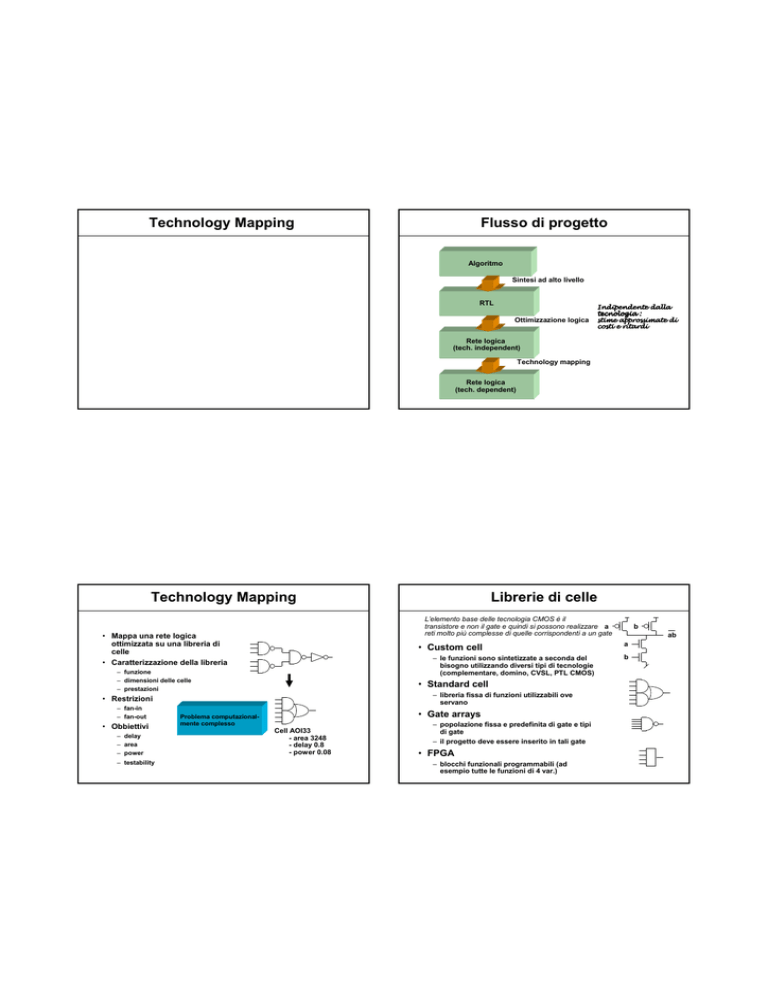

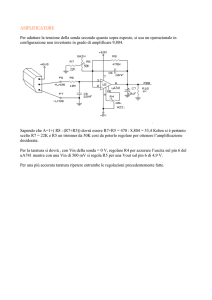

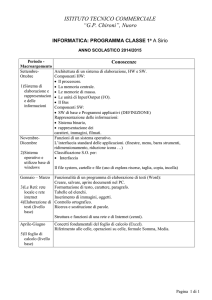

Flusso di progetto

Algoritmo

Sintesi ad alto livello

RTL

Ottimizzazione logica

Indipendente dalla

tecnologia :

stime approssimate di

costi e ritardi

Rete logica

(tech. independent)

Technology mapping

Rete logica

(tech. dependent)

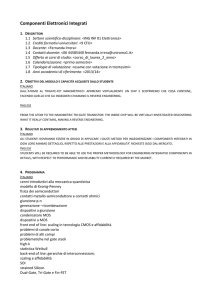

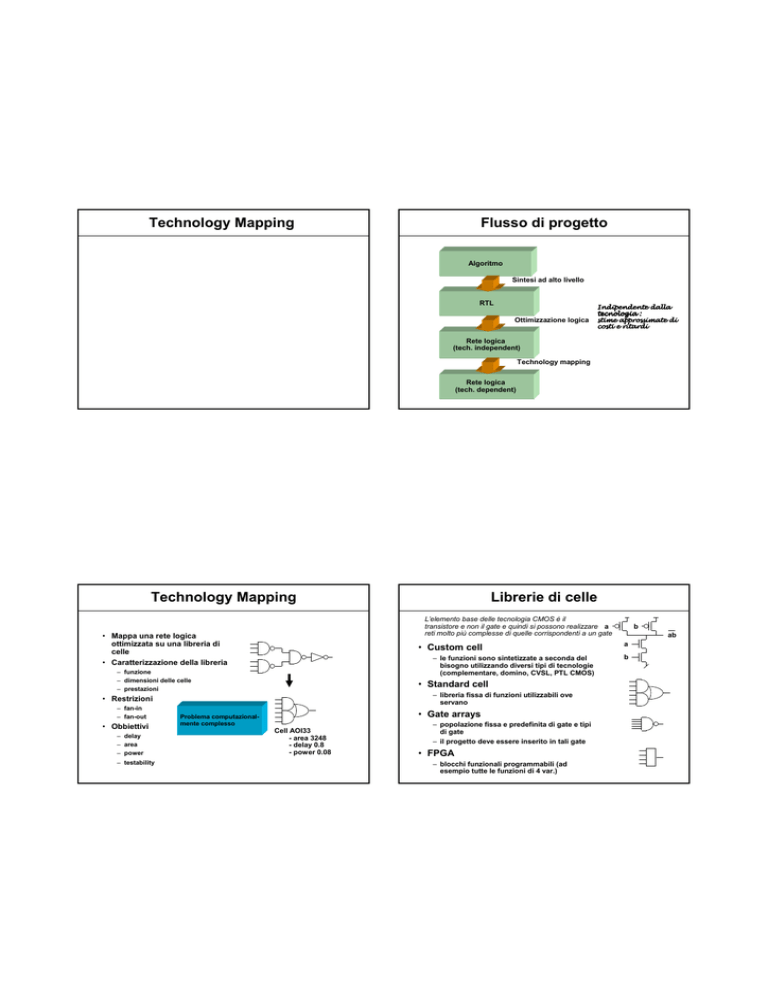

Technology Mapping

L’elemento base delle tecnologia CMOS è il

transistore e non il gate e quindi si possono realizzare a

reti molto più complesse di quelle corrispondenti a un gate

• Mappa una rete logica

ottimizzata su una libreria di

celle

• Caratterizzazione della libreria

• Custom cell

– le funzioni sono sintetizzate a seconda del

bisogno utilizzando diversi tipi di tecnologie

(complementare, domino, CVSL, PTL CMOS)

– funzione

– dimensioni delle celle

– prestazioni

• Standard cell

– libreria fissa di funzioni utilizzabili ove

servano

• Restrizioni

– fan-in

– fan-out

• Obbiettivi

– delay

– area

– power

– testability

Librerie di celle

• Gate arrays

Problema computazionalmente complesso

Cell AOI33

- area 3248

- delay 0.8

- power 0.08

– popolazione fissa e predefinita di gate e tipi

di gate

– il progetto deve essere inserito in tali gate

• FPGA

– blocchi funzionali programmabili (ad

esempio tutte le funzioni di 4 var.)

b

ab

a

b

Sintesi di celle custom

Libreria di celle standard

• In teoria si potrebbe realizzare un blocco CMOS

per qualsiasi funzione interessante

– la cella risultante potrebbe essere piuttosto lenta - ad es.

20-input NAND gate

– il problema è evitabile limitando le dimensioni delle funzioni

durante il processo di sintesi

ABCDEF => (ABC)(DEF)

– limiti sul fan-in e fan-out delle funzioni

A+B+C+D => (A+B)+(C+D)

• Possibilità di sfruttare appieno

dimensionamenti elettrici

– dimensionamento dei transistori per soddisfare le

specifiche sulle temporizzazioni (logical effort)

– velocizzazione dei cammini più lunghi del circuito

– regole specifiche per il tipo di tecnologia utilizzata

Matching basato sulle regole (IBM)

• Applica alla rete una serie di

trasformazioni basate su regole

– che codificano le capacità e le restrizioni della

libreria

– trasformazioni che migliorano area, delay, power,

etc.

• Problemi

– le regole non garantiscono di trovare un ottimo

•

•

•

•

•

•

•

NOT, NAND 2 - 4, NOR 2 - 4

AOI gates:(a+bc)’, (ab+cd)’ ….

OAI gates: (a(b+c))’, ((a+b)(c+d))’ ….

EXOR, EXNOR

MPX, HA, FA

elementi di memoria

per ogni funzione ci sono vari dimensionamenti

per soddisfare le specifiche timing

Graph Covering

F = abcd

• Rappresentazione delle

equazioni logiche

– directed acyclic graph (DAG)

» 2-input NAND e invertitori

» la rappresentazione non è unica

• Rappresentazione delle celle di

libreria

a

– utilizzo di DAG

» 2-input NAND e invertitori

» tutte le possibili rappresentazioni di

una cella

» ~N! possibilità (N = numero di

ingressi)

– costo di una cella (area, delay, power)

a

F

NOT

NAND

b

F

b

F

d

d

F

b

c

c

a

d

b

•••

a

c

c

d

Graph Covering

Esempio

• Algoritmo

F = abcd

– copertura di costo minimo delle equazioni del

circuito (DAG) con i DAG che descrivono le

equazioni delle porte logiche della libreria

– NP-completo

– problema simile alla generazione di codice di un

compilatore

• Approcci

– ricerca a partire dai primary inputs

– ricerca a partire dai primary outputs

– tentare prima con i DAGs delle celle più grandi

» area ridotta

» problemi di prestazioni

– bisogna evitare i minimi locali

• Esempio delle possibilità per la copertura di una

rete mediante componenti di libreria

F

a

b

c

d

F

a

b

c

d

Libreria

INVERTER A=2

NAND2

A=3

NAND3

A=4

NAND4

A=5

AOI21

A=4

AOI22

A=5

Rete obbiettivo

Rappresentazione ad albero

(canonica)

Copertura triviale

Primo tentativo

Costo

7*NAND2+5*INV=21+10=31

Costo

NAND2+2*INV+NAND3+NAND4=4+6+4+5=19

Secondo tentativo

Tree pattern matching

• Il graph covering può avere dei costi esponenziali

• Si utilizzano allora degli euristici che

garantiscono una maggior efficienza

computazionale

• Chiaramente, danno luogo a soluzioni

parzialmente ottimali

• Se tutti i grafi (sia della rete di partenza) che delle

celle sono alberi, si può trovare una soluzione

ottima (per l’albero)

Costo

NAND2+INV+2*NAND3+AOI121=3+2+8+4=17

Formulazione del problema

• Rappresentazione della rete in forma normale

– subject DAG

• Rappresentazione di ciascun gate della libreria in

forma normale

– primitive DAG

• Ciascun DAG ha un costo

• Obbiettivo: trovare una copertura di costo minimo

• Forma normale:

Copertura ottimale di alberi

• La copertura di una rete ad albero è ottima se

consiste nella migliore copertura per la radice

dell’albero e nelle coperture ottime dei sottoalberi

che partono dagli ingressi della copertura della

radice

• Questo consente di utilizzare tecniche di dynamic

programming

– rete di NAND a 2 ingressi e invertitori

– Per forma normale, si intende una decomposizione a NAND e

invertitori con gli alberi orientati verso sinistra (il primo

ingresso vede il minimo numero di livelli logici) (o viceversa)

Tree Pattern Matching

• Partiziona il grafo diretto aciclico del circuito in un

albero

– split dei nodi di fan-out

– solamente le uscite possono essere radici degli alberi

– la divisione viene fatta incrementalmente durante la ricerca

nell’albero e si ferma quando si trovano nodi già mappati

Fan-out splitting

DAG

• Algoritmo

– cerca il mapping ottimale per l’uscita dell’albero

– utilizza un algoritmo di confronto recursivo per verificare la

corrispondenza fra gli alberi

» cerca un matching per l’uscita

» cerca un mapping ottimale per le ciascun sottoalbero

che parte dagli ingressi delle cella già mappata

» costo = cell (output) più il costo delle celle di ingresso

– attraversamento top-down per registrare le celle già mappate

– tempo esponenziale

Forest of trees

Tree Pattern Matching

OptimalTree(tree)

{

mincost = INF;

for all cells

if (cell matches at tree.root) {

cost = cell.cost;

for all cell inputs

cost += OptimalTree(cell.input[i]);

if (cost < mincost) {

cost = 5+2+2+5+2+2 = 18

mincost = cost;

keep tree mapping;

}

}

return(mincost);

}

for each output {

outputcost = OptimalTree(output);

scan top-down to get cell mapping;

}

Tree Pattern Matching

• Inietta coppie di invertitori alle uscite dei

gate

– aumenta il numero di possibili match

Esempio

senza invertitori

con gli invertitori

cost = 4+4 = 8

Caratteristiche dell’algoritmo

• Si tratta di un algoritmo veloce

• Una cella può avere diversi tipi di albero che

la rappresentano

• Può perdere delle sottoespressioni comuni

Graph Pattern Matching

• Il match avviene con sottografi e non con alberi

– evita di decomporre il circuito in foreste di alberi

– match con più tipi di gate

» XOR, MUX

» multiple-output gates

• Algoritmo

a

a

b

c

d

a

b

c

b

c

b

b

c

d

c

d

4, 2-input AND

costo: 24 transistor

2, 3-input AND

cost: 16 transistor

– per ogni nodo del circuito, trova tutti i sottografi che corrispondono al

grafo di una cella

» O(C*N) (C è il numero di nodi del circuito, N numero di celle nella

libreria)

– copertura del grafo del circuito con grafi di minimo costo delle celle

» matrice con una riga per ogni nodo del circuito e una colonna per

ogni cella: valore 1 se la cella corrisponde al nodo e 0 altrimenti

» si cerca il massimo insieme di righe indipendenti (le celle non si

devono sovrapporre) che sia di costo minimo mediante una strategia

di branch and bound

Graph Matching Algorithm

Copertura di minimo costo di un grafo

celle di libreria

boolean CellMatch(x, y)

if (y.gatetype != x.gatetype) return(0);

i = y.firstchild; j = x.firstchild;

while (i != NULL && j != NULL)

if (!CellMatch(i,j)) return(0);

i = y.nextchild; j = x.nextchild;

if (j == NULL) return(1);

else return(0);

2

3

4

1

5

6

match

XOR cell

d

c

e

f

b

XOR2 INV NOR2 NAND2

Cost 14

2

4

4

a

0

0

1

0

b

1

0

0

1

c

0

0

0

1

d

0

1

0

0

e

0

0

0

1

f

0

0

0

1

a

Circuito

for each node i in circuit graph

for each cell j in library graphs

if (CellMatch(i,j)) match[i][j] = 1

soluzione iniziale: a, b, c, d, e,f

bound = 4 + 4 + 4 + 2 + 4 + 4= 26

soluzione di minor costo: a, b, d

costo = 4 + 14 + 2 = 20

NOR2 => a

XOR2 => b

INV => d

find least-cost maximum set of independent

rows in match array

Layout-Driven Mapping

FPGA Technology Mapping

• Blocchi logici programmibili

• Obbiettivo

–

–

–

–

minimizzare l’area del chip

gli approcci prcedenti

ignoravano le interconnessioni fra le celle

esempio - fan-in e fan-out grandi

» minimizza l’area delle celle

» implica molte interconnessioni

• Soluzione

– stima gli effetti del place e route durante il

mapping

» stime semplici e veloci

– multiplexor-based (Actel)

– lookup table (Xilinx)

• Problema

K

– una lookup table di K ingressi implementa 2 2 possibili

funzioni

– K = 5 (valore tipico)

– il numero di celle di libreria da considerare risulterebbe non

pratico

• Soluzioni

– bin packing

– OBDD matching

– ….

FPGAs

Bin packing

• Xilinx

–

–

–

–

RAM configurable logic blocks (CLB)

RAM programmable wiring

2 funzioni di 4 variabili

1 funzione di 5 variabili

• E’ un problema di ottimizzazione ben noto

• Dati n oggetti, ciascuno con la sua dimensione ai e

dei contenitori ciascuno dei quali può contenere

una dimensione k, si tratta di determinare il

numero di contenitori necessari a contenere tutti

gli oggetti

CLB

• Actel

–

–

–

–

elementi logici configurabili da fusibili

interconnessioni programmabili da fusibili

tutte le funzioni di 2 e 3 variabili

alcune funzioni di 4 variabili

Bin Packing

• Si vde ogni blocco logico configurabile

come un bin

– le equazioni dei nodi vengono considerate come

somme di prodotti

– cerca di inserire i prodotti nel minor numero

possibile di scaffali

– inserisce il termine somma in uno o più CLB che

lo possano contenere

• Algoritmo

– NP-completo

– euristico

» oridna i termini prodotti in ordine di

dimensione (numero di letterali) decrescente

» li inserisce nel primo CLB in cui c’è spazio

sufficiente

» O(N log N) ma da risultati peggiori del 22%

rispetto all’ottimo

Esempi

•

•

•

•

•

Utilizzo del technology mapping in SIS

Librerie tecnologiche

Il comando map

Il compromesso fra area e ritardo

Possibili esperienze da realizzare

Technology mapping in SIS

• All’interno di SIS si trovano diversi comandi da

utilizzare per il technology mapping

• Questi comandi vengono eseguiti una volta che:

– sia stata letta una libreria

– sia stata eseguita un ottimizzazione technology independent della

rete multilivello

• Gli algoritmi di technology mapping consentono di

ottimizzare o l’area o il ritardo

Libreria

• Le librerie utilizzate nella sintesi di circuiti basati su

standard cell sono costituite da celle caratterizzate

da:

–

–

–

–

funzione logica ie conengono

area

capacità di ingresso

parametri per il calcolo del ritardo di propagazione

• Le librerie contengono sia celle combinatorie che

sequenziali (latch, flip-flop)

• Le librerie commerciali possono contenere parecchie

decine di componenti

Librerie nel linguaggio blif

• Formato per la descrizione di celle combinatorie

GATE <cell_name

<cell_name>

cell_name> <cell_area

<cell_area>

cell_area> <cell_logic_function>

<pin_info>

pin_info>

<pin_info>:==<

pin_info>:==<pin_name

>:==<pin_name>

pin_name> <phase

<phase>

phase> <input_load

<input_load>

input_load>

<max_load>

max_load> <rise_delay

<rise_delay>

rise_delay> <rise_fan_out_delay>

<fall_delay>

fall_delay> <fall_fan_out_delay>

• delay=r/fdelay+r/fdelay.fan_out

Esempio (mcnc.genlib)

GATE inv1

#GATE inv2

#GATE inv3

#GATE inv4

GATE nand2

GATE nand3

GATE nand4

GATE nor2

GATE nor3

GATE nor4

#GATE and2

#GATE or2

GATE xor

GATE xor

GATE xnor

GATE xnor

GATE aoi21

GATE aoi22

GATE oai21

GATE oai22

GATE zero

GATE one

1

2

3

4

2

3

4

2

3

4

3

3

5

5

5

5

3

4

3

4

0

0

O=!a;

PIN * INV 1 999 0.9 0.3 0.9 0.3

O=!a;

PIN * INV 2 999 1.0 0.1 1.0 0.1

O=!a;

PIN * INV 3 999 1.1 0.09 1.1 0.09

O=!a;

PIN * INV 4 999 1.2 0.07 1.2 0.07

O=!(a*b);

PIN * INV 1 999 1.0 0.2 1.0 0.2

O=!(a*b*c); PIN * INV 1 999 1.1 0.3 1.1 0.3

O=!(a*b*c*d);

PIN * INV 1 999 1.4 0.4 1.4 0.4

O=!(a+b);

PIN * INV 1 999 1.4 0.5 1.4 0.5

O=!(a+b+c); PIN * INV 1 999 2.4 0.7 2.4 0.7

O=!(a+b+c+d);

PIN * INV 1 999 3.8 1.0 3.8 1.0

O=a*b;

PIN * NONINV 1 999 1.9 0.3 1.9 0.3

O=a+b;

PIN * NONINV 1 999 2.4 0.3 2.4 0.3

O=a*!b+!a*b;

PIN * UNKNOWN 2 999 1.9 0.5 1.9 0.5

O=!(a*b+!a*!b);

PIN * UNKNOWN 2 999 1.9 0.5 1.9 0.5

O=a*b+!a*!b;

PIN * UNKNOWN 2 999 2.1 0.5 2.1 0.5

O=!(!a*b+a*!b);

PIN * UNKNOWN 2 999 2.1 0.5 2.1 0.5

O=!(a*b+c); PIN * INV 1 999 1.6 0.4 1.6 0.4

O=!(a*b+c*d);

PIN * INV 1 999 2.0 0.4 2.0 0.4

O=!((a+b)*c);

PIN * INV 1 999 1.6 0.4 1.6 0.4

O=!((a+b)*(c+d));PIN * INV 1 999 2.0 0.4 2.0 0.4

O=CONST0;

O=CONST1;

Comandi per il mapping

Suggerimenti per possibili prove

• SIS mette a disposizione il comando map per il

technology mapping

• Per ottimizzare l’area: map –m

m 0

• Per ottimizzare il ritardo: map –n

n 1 –AFG

AFG

• Per avere delle statistiche sui risultati del technology

mapping: print_map_stats

• Per stampare il file blif con la netlist mappata:

write_blif –s

s –n

n <nome file>

• Utilizzo di scrit.rugged e script.boolean seguito da map

–m 0 per un insieme di benchmark dall’insieme

LGSynth89

– si rappresenti su un grafico la relazione fra il costo della rete

technology independent (numero di letterali) e l’area della rete

mappata

– si ripeta la stessa operazione per script.boolean

– si determini se la relazione è monotona

• Per ogni benchmark si usi lo script script.delay e map

–n 1 AFG per ottenere una versione ottimizzata dal

punto di vista dei ritardi

– Si appresenti in un grafico la relazione fra area e ritardo per le varie

implementazioni dei benchmark