Waveform Digitizer

Review

Franco Spinella

Luca Morescalchi

Elena Pedreschi

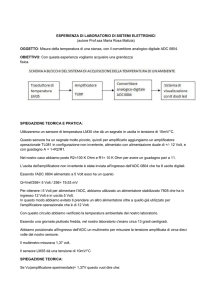

Calorimeter Electronics Scheme

Disks x2

FEE x10 / board

Crate x10

Waveform Digitizers

x8

CsI Crystal

CsI Crystal

(MPPC x2 / FEE)

ADC

ADC

ADC

ADC

ADC

ADC

DC/DC

ADC

ADC

DC/DC

ADC

ADC

FPGA

DC/DC

2

F. Spinella | INFN referee review

9/9/16

MU2E DAQ

• WD are readout in

chains (2-4 boards/chain)

• Chains are redundated

• Each chain is connected

to the DAQ servers

through optical fibers

WD

3

F. Spinella | INFN referee review

9/9/16

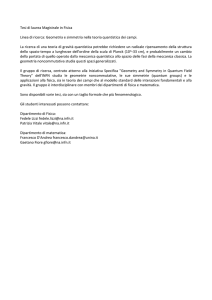

WD block diagram

FE

FE

2

3

9

FE

FE

10

4

ADS 4229

1

ARM CONTROLLER

1

FE

F. Spinella | INFN referee review

ADS 4229

FIBER

2

ADS 4229

3

FIBER

FPGA

SM2 150T

FIBER

FIBER

ADS 4229

9

ADS 4229

10

DC/DC

3.3V/1.8V

LTM8033

9/9/16

Specifiche WD

• Canali: 680 x 2 x 2 = 2720

•Goal 20 ch/board -> 2720 / 20 = 136 board (150 con spares)

• 12 bit, 200 MHz, flash ADC

•Ambiente ostile :

• campo magnetico elevato (1T)

• 5x1010 n/cm2 @ 1 MeVeq (Si)/y and 0.5 krad/y of TID (Total Ionizing

Dose).

• Vuoto

• Challenging …

5

F. Spinella | INFN referee review

9/9/16

Stato del progetto: componenti

- I componenti principali sono stati selezionati e qualificati singolarmente:

- ADC: TI ADS4229 (12 bit - 250 Msample max)

- DCDC converter: LTM8033 (max 3A)

- FPGA: Microsemi smartfusion 2 SM150T

- Alcuni componenti (e.g. DDR) sono comuni al tracker e qualificati da loro

- Altri saranno qualificati a livello di scheda (prototipo V1)

6

F. Spinella | INFN referee review

9/9/16

Stato del progetto:HW(1)

- Le schematiche sono quasi complete:

-

Definita la parte analogica di interfaccia tra ARM controller e ADC

Definito connettore di interfaccia tra le due schede

ADC, FPGA e DDR : OK

La V1 include un interfaccia Gbit elettrica per eventuale uso a TB

(richiede trasformatori), oltre a transceiver ottici rad-hard

- Definito l’albero di clock

- Rimane da progettare la parte power (DCDC ok)

7

F. Spinella | INFN referee review

9/9/16

Stato del progetto:HW(2)

- Sbroglio effettuato da ditta esterna (gia’ ordinato), previste circa 3 settimane

- FPGA gia’ ordinate e in stock (6 pezzi)

- In fase di ordinazione:

- Produzione circuito stampato (2 pezzi) 1-2 settimane

- Montaggio pick & place 1 settimana

- Componenti per 6 schede (digikey,mouser,Farnell)

10

F. Spinella | INFN referee review

9/9/16

Stato del progetto:FW

- Una versione preliminare e semplificata del firmware (1 canale) e’ stata testata

su una demo-board

- Versione 20 canali del firmware semplificato pronta e simulata

- Versione a 20 canali per eventuale TB … work in progress …

- La parte di readout su fibra e di slow control e’ comune a tutti i subD e sara’

sviluppata in collaborazione con FNAL

9

F. Spinella | INFN referee review

9/9/16

Attivita’ prevista per il 2016

- Un prototipo v1 dovrebbe essere pronto entro l’anno

- In contemporanea dovrebbe essere pronta una versione preliminare del Fw con

readout su rame tramite Gbit Ethernet

- Test preliminari

11

F. Spinella | INFN referee review

9/9/16

Attivita’ prevista per il 2017

- Assemblaggio di 5 schede v1per test di qualifica e test beam in termovuoto

(componenti acquistati nel 2016)

- Test funzionali completi su 20 canali:

- Linearita’ ADC, crosstalk fra canali

- Readout tramite fibra

- Test di qualifica board level:

- Test sotto vuoto (funzionalita’ e Potenza dissipata)

- Test in campo magnetico

- Test in presenza di radiazione

Per questi test sara’ necessario lo sviluppo di un banco di prova per impulsare

contemporaneamente tutti i canali.

- Progetto e costruzione v2 (e forse anche v3 …)

11

F. Spinella | INFN referee review

9/9/16

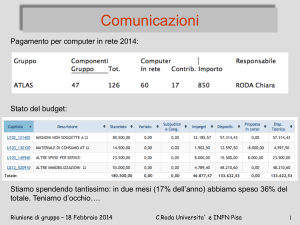

Cost

12

F. Spinella | INFN referee review

9/9/16