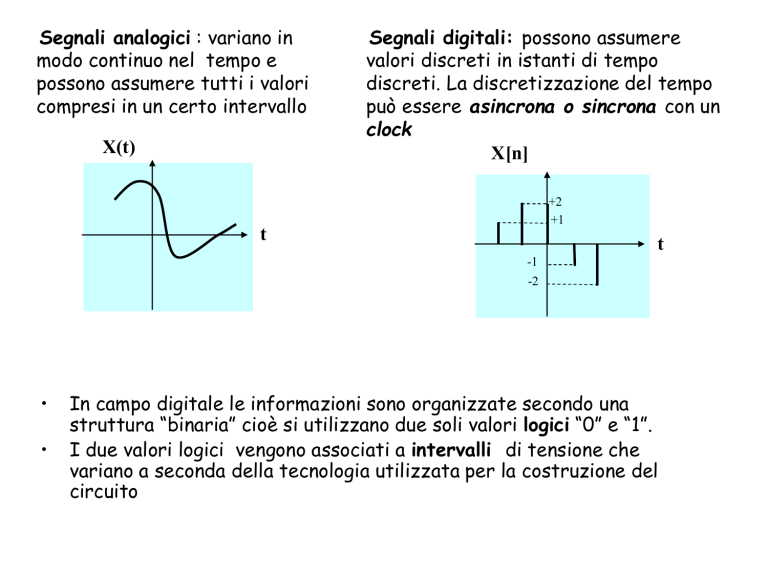

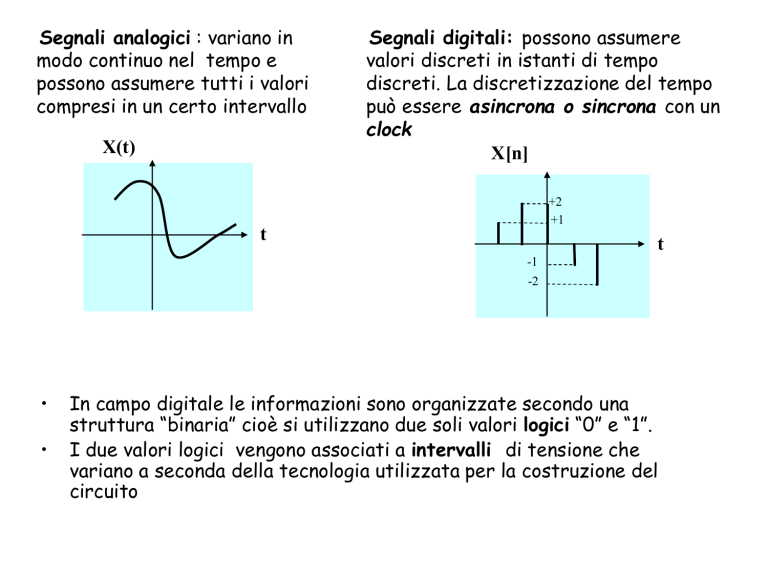

Segnali analogici : variano in

modo continuo nel tempo e

possono assumere tutti i valori

compresi in un certo intervallo

X(t)

Segnali digitali: possono assumere

valori discreti in istanti di tempo

discreti. La discretizzazione del tempo

può essere asincrona o sincrona con un

clock

X[n]

+2

+1

t

t

-1

-2

•

•

In campo digitale le informazioni sono organizzate secondo una

struttura “binaria” cioè si utilizzano due soli valori logici “0” e “1”.

I due valori logici vengono associati a intervalli di tensione che

variano a seconda della tecnologia utilizzata per la costruzione del

circuito

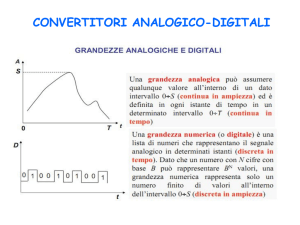

segnali analogici – segnali digitali

grandezza

fisica

segnale

trasduttore

segnale

elettrico

trattamento del

segnale

grandezza fisica variabile

segnale elettrico analogico

andamento della grandezza fisica

T

andamento della temperatura

in funzione del tempo

andamento della tensione

in funzione del tempo

•

•

trasmissione a distanza di piccoli segnali diversi stadi di amplificazione

introduzione del rumore degradazione del segnale.

conversione analogico – digitale riduce la distorsione del segnale.

segnale digitale: sequenza di 1 e 0

Esempio di applicazione : Waveform digitizers (digitizzatori di forme d’onda)

Caratteristiche dei convertitori 1

Risoluzione

• espressa in bit.

Esempio : un ADC che codifica un ingresso

analogico in 256 livelli discreti ha una

risoluzione di 8 bit (28 = 256)

• espressa in Volt.

Esempio 1:

o range compreso tra 0 e 10 volt

o risoluzione dell'ADC di 12 bit:

212 = 4096 livelli di quantizzazione

o risoluzione in Volt è

10 V / 4096=0.00244 V = 2.44 mV

Esempio 2:

o range compreso tra -10 e 10 volt

o risoluzione dell'ADC di 14 bit:

214 = 16384 livelli di quantizzazione

o risoluzione in Volt è

20 V / 16384=0.00122 V = 1.22 mV

Caratteristiche dei convertitori 2

linearità: La maggior parte degli ADC sono lineari,

sono progettati per produrre in uscita un valore

uscita

funzione lineare del segnale di ingresso.

digitale

111

110

101

100

011

010

001

000

straight

line

0 1/8 2/8 3/8 4/8 5/8 6/8 7/8

ingresso analogico

monotonicità : aumentando la tensione di ingresso deve

aumentare l’uscita digitale (e viceversa) – se questo non

avviene si ha un errore di monotonicità

ADC non monotono

111

110

101

100

011

010

001

000

0 1/8 2/8 3/8 4/8 5/8 6/8 7/8

Caratteristiche dei convertitori 3

caratteristica

ideale

Errori di OFF SET : la tensione di

OFFSET è quella misurata quando

tutti gli ingressi digitali sono 0

Si misura generalmente in mV, mV o

frazione del bit meno significativo.

111

110

101

100

011

010

001

000

0 1/8 2/8 3/8 4/8 5/8 6/8 7/8

offset error +1½ LSB

Errori di non linearità: è la differenza tra

la variazione di tensione letta in uscita e

quella ideale (cioè quella corrispondente

alla variazione di 1 LSB (bit meno significativo)

Ad es.: un DAC per il quale, al variare di 1 LSB si

ottiene una variazione di tensione corrispondente

ad 1.5 LSB ha un errore di non linearità pari a

mezzo LSB.

caratteristica

ideale

111

110

101

100

011

010

001

000

a b

b-a

differential error

0 1/8 2/8 3/8 4/8 5/8 6/8 7/8

Un esempio di ADC

ADC a contatore

• convertitore semplice ed economico, ma lento

• si usano : un contatore, un DAC ed un comparatore

• il contatore genera una sequenza di numeri binari partendo da zero fino al max

valore che il numero di bit consente.

• ciascun numero viene convertito dal DAC in segnale analogico che viene inviato

al comparatore e confrontato con il segnale.

• l’uscita dal comparatore è positiva fin quando il segnale da convertire è maggiore

del segnale in uscita dal DAC.

• quando il comparatore dà un segnale negativo, il contatore viene bloccato e

il numero letto all’uscita del contatore è una stima approx per eccesso del segnale

in esame.

• sono necessari fino a 2N confronti

• errore di quantizzazione:

metà del bit meno significativo

es.: ADC a 4 bit, con una risoluzione

di 1 bit/100 mV, errore = ± 50 mV

ORGANIZZAZIONE LOGICA DI UN

ESPERIMENTO

1

2

3

4

FENOMENO FISICO

IPOTESI DI LEGGE FISICA

PROGETTAZIONE DI UNA

MISURA SPERIMENTALE

INDIVIDUAZIONE DEGLI

STRUMENTI PIU’ ADATTI

5

6

7

COSTRUZIONE

DELL’APPARATO

RACCOLTA DEI DATI

ELABORAZIONE DEI DATI

SPERIMENTALI E VERIFICA

CRITICA DELL’IPOTESI FISICA

SISTEMA DI ACQUISIZIONE DATI

TRASDUTTORI

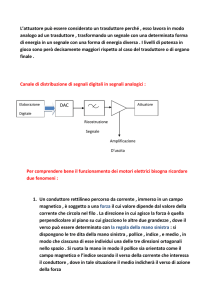

Trasformano una grandezza fisica in un’altra generalmente

un segnale elettrico (facilmente trattabile da parte di un

sistema automatico)

Trasduttori On-Off

Identificazione di eventi

aleatori che possono avere 2

soli stati vero / falso

Trasduttori “CONTINUI”

Monitoraggio di una grandezza

analogica (pressione, ..) variabile

in modo continuo in ampiezza e nel

tempo

Sistema di acquisizione dati

trasduttori on-off

Il trasduttore on-off è un elemento che trasforma una

determinata grandezza fisica in una informazione di

tipo binario (1-0, si-no, aperto-chiuso)

“1” se è accaduto

l’evento

EVENTO

TRASDUTTORE

ON-OFF

“0” se non è accaduto

l’evento

Sistema di acquisizione dati

trasduttori on-off

L’interruttore è un esempio di dispositivo che può svolgere

il ruolo di trasduttore on-off

(0 VOLT)

+5V

“0”

R

(5 VOLT) “1”

+5V

R

SISTEMA DI ACQUISIZIONE DATI

METODO “TRADIZIONALE” E METODO ON-LINE

per esempio: un dinamometro a molla

INPUT FISICO:

TRASDUTTORE

“CONTINUO”

FORZA, PRESSIONE,

TEMPERATURA, ETC

SCALA GRADUATA

a) TRASDUTTORE PER MISURA “TRADIZIONALE”

per esempio: una termocoppia

INPUT FISICO:

FORZA, PRESSIONE,

TEMPERATURA, ETC

ALIMENTAZIONE

ELETTRICA

TRASDUTTORE

“CONTINUO”

OUTPUT

ELETTRICO

b) TRASDUTTORE PER MISURA ON LINE

SISTEMA DI

ACQUISIZIONE

DATI (DAS )

In generale, l’uscita di un trasduttore “continuo” è un segnale di tipo

analogico, per esempio una differenza di potenziale variabile nel tempo.

Come trasformare questo

segnale analogico in un

segnale numerico, cioè in

una sequenza di bit?

X(t) ----- X(n Tc)

dove Tc è l’intervallo di tempo tra

un campionamento e l’altro

E’ necessario un passo intermedio prima di arrivare al vero e proprio

circuito di conversione analogico – digitale

CAMPIONAMENTO

Il clock scandisce l’operazione di campionamento: ad ogni impulso di clock

viene prelevata l’ampiezza “istantanea” del segnale in esame.

Ad intervalli di tempo regolari il segnale analogico viene immagazzinato

in una memoria analogica.

(a) funzione d’onda

(b) impulsi di clock

(c) risultato del campionamento

Il risultato è ancora analogico, cioè in uscita abbiamo una serie di numeri

reali che rappresentano il valore del segnale nei diversi istanti di tempo.

Circuito di Sample and Hold (S&H) = è un circuito che campiona (SAMPLE)

il segnale analogico all’istante voluto e ne trattiene (HOLD) il valore

mentre il circuito successivo (ADC) lo legge e lo converte in una sequenza

di bit (numero).

Può essere definito una interfaccia tra un segnale analogico rapidamente

variabile e un dispositivo successivo, in genere un ADC.

[01100101100…]

Esempio di circuito S&H (il più elementare) :

• chiusura dell’interruttore S ad un certo istante

• condensatore C in carica fino a Vi

• apertura di S

• lettura del segnale Vo

schema logico

Amplificatori operazionali in

configurazione di “inseguitori di

tensione” guadagno=1

vin: il segnale da campionare

vout: il segnale campionato

vs: il segnale impulsivo di controllo

che comanda l'apertura e la chiusura

dell'interruttore S.

Rout1+ Rint

Rin2 valore alto

TH quasi infinito

valore basso

TS piccolo

S chiuso C si carica alla tensione di ingresso vin sample (condensatore cattura vin. )

in un tempo breve

S aperto il condensatore “mantiene” vin. hold (mantenimento)

il tempo di scarica del condensatore è praticamente infinito

Circuito S&H in cui l’interruttore

è realizzato con un FET.

Sistema di acquisizione dati

il circuito di Sample and Hold

INGRESSO DI

CONTROLLO

A/D

INPUT

Tempo di conversione

non nullo Tc

S/H

SCHEMA ELETTRICO DEL SAMPLE AND HOLD

Vi

V

Vo

Vo

Vo= Vi

Vi

Vi

Vo= Vi

Vo= Vi

TS

Vo

TH

TC

TS

OUTPUT

TH

TC

TS

TH

TC

Vo= Vi

TS

TC

t

E’ necessario l’uso di un circuito S&H per dare tempo all’ADC di

effettuare la conversione.

Dal tempo di conversione si ricava il limite superiore alla frequenza di

campionamento.

E’ possibile inviare la successione di bit ottenuta dall’ADC ad un ricevitore

che provvede poi, tramite un convertitore D/A, a riprodurre

l’informazione analogica originale.

codifica binaria

ADC

[01100101100…]

DAC

forma d’onda ricostruita

S&H

forma d’onda originale

campionamento

MA

Siamo sicuri di ricostruire fedelmente la forma d’onda

di partenza?

• In particolare, ci sono ambiguità dovute al

campionamento del segnale?

• Quale deve essere l’intervallo tra due campionamenti

successivi per avere la certezza di ricostruire

fedelmente e univocamente la forma d’onda?

TEOREMA DEL CAMPIONAMENTO (Nyquist, 1928;

Shannon, 1949) per evitare ambiguità nel campionamento (aliasing),

la frequenza di campionamento deve essere almeno il doppio della

frequenza massima presente nel segnale.

uso di filtri (anti-alias) prima del circuito di campionamento, per

eliminare frequenze troppo alte

Esempio per costruire un "cd" il segnale audio analogico viene prima digitalizzato ad una

frequenza di 44.1KHz, dato che la larghezza di banda delle frequenze udibili è di 22KHz

due segnali sinusoidali : n1 = 2 sin (103 p t) n2 = -2 sin (7 * 103 p t) le cui frequenze

sono: n1 = 0.5 kHz e n2 = 3.5 kHz.

Se campioniamo alla frequenza di 4 kHz (ogni 0.25ms) – punti neri – le due curve

hanno in quegli istanti gli stessi valori ambiguità

Campionando a 8kHz (ogni 0.125ms) l’ambiguità sparisce – punti blu