Università degli Studi di Trieste

Facoltà di Ingegneria

Laureando:

Emanuele Viviani

Relatore:

Prof. Stefano Marsi

Anno Accademico 2009-2010

Sistema versatile di elaborazione audio

◦ Filtri passa basso

◦ Filtri passa alto

◦ Filtri passa banda

◦…

Implementazione di un filtro adattativo

◦ Algoritmo LMS

Progetto di un’architettura versatile per l’elaborazione di segnali audio su FPGA

Classe di filtri i cui coefficienti variano nel

tempo

Riduzione del rumore:

◦ s+n1: segnale utile con sovrapposta una

componente rumorosa;

◦ n2: rumore correlato a quello che si sovrappone al

segnale utile.

Progetto di un’architettura versatile per l’elaborazione di segnali audio su FPGA

Realizzazione di un filtro FIR di ordine elevato

◦ Lunghezza del filtro regolabile

◦ Coefficienti modificabili

◦ Numero di bit significativi dei coefficienti regolabile

Implementazione di un processore

Progetto di un’architettura versatile per l’elaborazione di segnali audio su FPGA

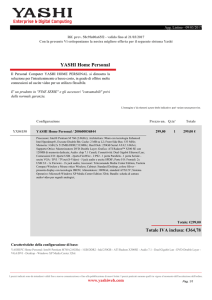

FPGA

◦ Cyclone II EP2C20F484C7 Altera

I/O Devices

◦ Built-in USB Blaster for FPGA configuration

◦ Line-in, Line-out, Mic-in (24-bit audio CODEC)

Memory

◦ 8-MB SDRAM

Switches, LEDs, Displays, and Clocks

◦ 10 toggle switches

◦ 4 debounced pushbutton switches

◦ 10 red LEDs, 8 green LEDs

◦ 27-MHz and 50-MHz oscillators

Progetto di un’architettura versatile per l’elaborazione di segnali audio su FPGA

Descrizione

Valori

Frequenza di campionamento del codec audio

Lunghezza del filtro

8KHz, 32KHz

1 - 1023

Rappresentazione dei campioni audio

Rappresentazione dei coefficienti

15 bit interi con segno

31 bit fixed point con segno

Numero di bit significativi nella rappresentazione usata

per i coefficienti

0 - 31

Frequenza di lavoro del processore e della SDRAM

100 MHz

Frequenza di lavoro del filtro

100 MHz

Tempo impiegato dal filtro per il calcolo del campione

96 ns con L_FIR = 1

10,3 us con L_FIR = 1023

Progetto di un’architettura versatile per l’elaborazione di segnali audio su FPGA

s+n1

n2

R

R

Interfaccia

L

audio

L

Filtro FIR

Selettore

Nios II

Interfaccia

System

audio

Progetto di un’architettura versatile per l’elaborazione di segnali audio su FPGA

R

L

R

Interfaccia

audio

Genera i segnali di sincronismo

Riceve i segnali dell’ADC

Invia i campioni al filtro

Riceve i dati elaborati

Invia i dati al DAC

L

Uscita

Sommatore

Progetto di un’architettura versatile per l’elaborazione di segnali audio su FPGA

x[n]

FIR

y[n]

Progetto di un’architettura versatile per l’elaborazione di segnali audio su FPGA

Un blocco MAC (Multiply-Accumulate)

Una memoria coefficienti

Una memoria dati

Blocco di sincronismo

Ingresso

audio

Lunghezza

filtro

Memoria

Dati

Blocco di

sincronismo

Nuovi

Coefficienti

MAC

Uscita

Filtro

Memoria

Coefficienti

Progetto di un’architettura versatile per l’elaborazione di segnali audio su FPGA

1024 parole a 16 bit

Memoria dual port

Indirizzamento circolare

◦ Un puntatore scrittura

◦ Un puntatore lettura

Progetto di un’architettura versatile per l’elaborazione di segnali audio su FPGA

1024 parole a 32 bit

Memoria dual port

Progetto di un’architettura versatile per l’elaborazione di segnali audio su FPGA

Intellectual Property fornito da Altera

Sfrutta i componenti hardware integrati nella

FPGA

Progetto di un’architettura versatile per l’elaborazione di segnali audio su FPGA

Controlla la lettura dalle memorie

Imposta il sincronismo tra i dati e

l’esecuzione delle MAC

Ferma l’esecuzione delle MAC quando viene

raggiunta la lunghezza del filtro richiesta

Progetto di un’architettura versatile per l’elaborazione di segnali audio su FPGA

Ingresso

Audio secondario

Uscita

Filtro

Selettore

Uscita

audio

Precisione Selezione

Coefficienti Uscita

Seleziona il segnale d’uscita:

◦ Il risultato del filtro

◦ La differenza tra un segnale secondario e l’uscita

del filtro

◦ Il segnale secondario

Progetto di un’architettura versatile per l’elaborazione di segnali audio su FPGA

Sistema SOPC (system-on-a-programmable-chip)

Formato da:

◦

◦

◦

◦

◦

◦

Processore «Fast» della famiglia «Nios II»

On chip RAM

External SDRAM Controller

Audio and Video Config

Parallel I/O Port per il controllo del filtro

Parallel I/O Port per le periferiche esterne

Progetto di un’architettura versatile per l’elaborazione di segnali audio su FPGA

Progetto di un’architettura versatile per l’elaborazione di segnali audio su FPGA

Canale destro:

◦ Ottenuto come somma di:

Sinusoide a 1KHz

Rumore bianco

Canale sinistro:

◦ Rumore correlato

Progetto di un’architettura versatile per l’elaborazione di segnali audio su FPGA

Progetto di un’architettura versatile per l’elaborazione di segnali audio su FPGA

GRAZIE

Progetto di un’architettura versatile per l’elaborazione di segnali audio su FPGA