Università degli Studi di Catania

Facoltà di Ingegneria

Architettura del

Calcolatore

Prof.Ing.S.Cavalieri

1

Indice

Evoluzione del Computer

Il modello di Von Neumann

Descrizione dell'Architettura da Studiare

Circuiti di Temporizzazioni (Clock)

Memorie RAM, ROM, Cache

Unità centrale di processo (CPU)

Direct Memory Access (DMA)

Circuiti di Interrupt

Chipset

BIOS

Bus di comunicazione

Controllore di periferiche (Controller)

Prof.Ing.S.Cavalieri

Periferiche e Memorie di Massa

2

Evoluzione: tecnologia

Sistemi Meccanici

Sistemi Meccanici/Elettrici

Sistemi Elettronici basati su Valvole

Sistemi Elettronici basati su Transistor

Sistemi Elettronici basati su Circuiti Integrati

Sistemi Elettronici basati su Microprocessori

Prof.Ing.S.Cavalieri

3

Evoluzione: tipi di calcolatori

1950 – Mainframe locale: batch (prima), time sharing (dopo)

1960 – Mainframe remoto: linee di telecomunicazioni.

1970 – Mini Computers: ambienti meno restrittivi, costi accessibili,

time sharing, Unix, Linguaggio C

1980 – Personal Computers: uso "domestico", applicativi per

compiti comuni (es.videoscrittura).

1990 – PC connessi in Reti di Calcolatori: PC con capacità

elaborative ed interfacce ad alte prestazioni, LAN, Internet.

2000 – Internet: reti a larga banda

Futuro Prossimo - Griglie Computazionali

Prof.Ing.S.Cavalieri

4

Il modello di Von Neumann

CPU

MEMORIA

CENTRALE

INTERFACCIA

I/O

PERIFERICHE

Prof.Ing.S.Cavalieri

5

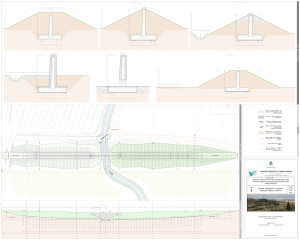

Architettura Studiata

Bus di controllo

DMA

Bus di indirizzi

ROM

RAM

Clock

CPU

Interrupt

BIOS

Prof.Ing.S.Cavalieri

Bus di dati

Controller

dischi,

CD-ROM,etc.

Connettori

Periferiche

I/O

Bus di I/O

6

Circuiti di Temporizzazione

(Clock)

T

tempo

Il megahertz (MHz) è l'unità di misura della frequenza alla quale

il processore funziona;

indica quanti milioni di oscillazioni al secondo (1 oscillazione al

secondo = 1 hertz [Hz]) sono generate dal clock.

f=1/T Hz.

Prof.Ing.S.Cavalieri

7

Circuiti di Temporizzazione

(Clock)

In generale il clock é prodotto da un apposito circuito

integrato, la cui oscillazione é controllata da un

cristallo di quarzo.

Il cristallo di quarzo garantisce una elevata stabilita nel

tempo e con il variare della temperatura ed una grande

precisione nel valore della frequenza prodotta, quanto

meno possibile influenzato dalla temperatura e dall'

invecchiamento.

In generale il quarzo di partenza é il 14.318 MHz

Scelta legata alla diffusione e economicità

Prof.Ing.S.Cavalieri

8

Circuiti di Temporizzazione

(Clock)

Prof.Ing.S.Cavalieri

9

Circuiti di Temporizzazione

(Clock)

Partendo dal quarzo a 14.318MHz, vengono generate

frequenze più elevate (50, 60, 66, 100MHz).

Ogni area del PC che contiene un processore o un

microcontrollore, necessita di un clock, che puó essere

generato in loco o dipendere dal clock principale.

Giá a partire dalle architetture basate sulla CPU 80486,

é diventato comune avere per il processore un clock piú

elevato di quello generale del sistema.

Prof.Ing.S.Cavalieri

10

Memorie Interne

RAM, ROM e Cache

Misura della Memoria

Classificazione della Memoria:

Interna ed Esterna

Memoria Interna: Caratteristiche Generali

RAM Statica

RAM Dinamica

ROM, PROM, EPROM, EEPROM, Flash

Memory

Memoria Cache

Prof.Ing.S.Cavalieri

11

Misura della Memoria

Informazione di base = bit

Raggruppamenti utilizzati:

1 byte = 8 bit

1 word = N byte

Multipli (bit/byte)

K (Kilo) = 210 (=1024) circa 103

M (Mega) = 220 (=1024*1024=1.048.576) circa 106

G (Giga) = 230 circa 109

T (Tera) = 240 circa 1012

P (Peta) = 250 circa 1015

Prof.Ing.S.Cavalieri

12

Alcuni Valori da Ricordare

24 = 16

28 = 256

216 = 65536 = 64

Prof.Ing.S.Cavalieri

K (65536/1024)

13

Memoria Interna o Centrale

memorizza programmi e dati su cui lavora la CPU a

cui è collegata tramite il bus principale:

si accede al singolo bit/byte/word

tempi di accesso bassi (<70 ns);

dimensioni tipiche sono 256Mbytes/512Mbytes

realizzata con circuiti elettronici

Prof.Ing.S.Cavalieri

14

Memoria Esterna o di Massa

memorizza dati e programmi sotto forma di file. Per

l’elaborazione, si devono trasferire programmi e dati

in memoria centrale:

Si accede a blocchi (cluster/settori)

Non è possible leggere/scrivere singoli bit/byte

tempi di accesso elevati (msec)

capacità elevate (decine/centinaia di Gbytes)

Può essere:

Memoria di Massa on-line, normalmente

realizzata con dischi magnetici fissi

Memoria di Massa off-line, normalmente

realizzata con supporti

Prof.Ing.S.Cavalieri (magnetici/ottici/elettronici) rimovibili

15

Memoria Interna:

Caratteristiche Generali

1 bit

bus degli indirizzi

n fili

0

1

2

bus dei dati

bus di controllo

read/write (strobe)

Prof.Ing.S.Cavalieri

m-1

16

Memoria Interna:

Caratteristiche Generali

Indirizzi e valori: Con n bit di indirizzo si

possono selezionare 2n caselle (m=2n).

Strobe: sono segnali generalmente impulsivi che

vengono inviati dopo il posizionamento dell’indirizzo per

discriminare tra operazione di letture e scrittura

Prof.Ing.S.Cavalieri

17

Memoria Interna:

Caratteristiche Generali

Tempi di servizio: accesso, ciclo (misurati in clock).

Accesso. E' il tempo necessario affinché la memoria ponga in

uscita il valore richiesto (o possa registrare il valore in ingresso),

dopo aver posizionato l'indirizzo e lo strobe.

Ciclo. E' il tempo minimo che deve intercorrere tra due

posizionamenti validi dell’indirizzo e dello strobe.

Modificabilità: Memoria a Sola Lettura/Riscrivibile.

Qualsiasi memoria deve essere scritta almeno una volta.

Le memorie che non possono essere riscritte si dicono a sola

lettura;

altrimenti sono riscrivibili.

Prof.Ing.S.Cavalieri

18

Memoria Interna:

Caratteristiche Generali

Persistenza: permanenti/volatili. Sono permanenti le

memorie che mantengono i dati senza bisogno di

alimentazione elettrica; altrimenti si dicono volatili.

Accessibilità: casuale /sequenziale. Se non esiste alcun

vincolo sulla sequenza degli indirizzamenti effettuati, si

parla di memoria ad accesso casuale; quando invece il

successivo indirizzo è l’attuale incrementato di uno si

parla di memorie ad accesso sequenziale.

Prof.Ing.S.Cavalieri

19

Memoria Interna:

Caratteristiche Generali

1 bit

bus degli indirizzi

n fili

bus di controllo

read/write

bus dei dati

Prof.Ing.S.Cavalieri

20

Memoria Interna:

Caratteristiche Generali

Possiamo identificare diversi livelli funzionali di

memoria:

Random Access Memory (RAM)

Read Only Memory (ROM)

Memoria Cache

Prof.Ing.S.Cavalieri

21

RAM - Random Access Memory

Il termine RAM deriva da Random Access Memory

Memoria Volatile

o La mancanza di tensione provoca la perdita di tutte le

informazioni contenute.

o In presenza di tensione, ciascuna informazione memorizzata

rimane fino alla successiva scrittura.

Memoria ad accesso casuale

Attualmente assumono valori tipici di centinaia/migliaia

di MBytes.

Prof.Ing.S.Cavalieri

22

RAM - Random Access Memory

La RAM vengono utilizzate per i seguenti scopi:

memorizzare il Sistema Operativo (ad esempio

Windows).

memorizzare i programmi utenti prima della loro

esecuzione.

memorizzare i dati utenti provenienti dalle periferiche

o quelli intermedi.

La RAM può essere realizzata in differenti modi, ma

quella più comune è:

RAM dinamica (DRAM)

Prof.Ing.S.Cavalieri

23

RAM DINAMICHE (DRAM)

La DRAM usa delle capacità (condensatore) interne per

memorizzare i dati.

Le capacità perdono la loro carica dopo un certo intervallo di

tempo. Queste capacità necessitano di un costante rinfresco per

mantenere inalterata l'informazione memorizzata.

Il risultato finale è che tra due accessi consecutivi alla memoria, una

carica elettrica viene mandata a rinfrescare la capacità del chip di

memoria affinché il dato venga mantenuto nello stato logico

corretto.

Durante il rinfresco della memoria non è possibile accedere ad essa,

rallentando, dunque, le sue prestazioni in termini di accessi in

lettura/scrittura.

Prof.Ing.S.Cavalieri

24

RAM DINAMICHE (DRAM)

Utilizzano un condensatore per memorizzare

1 Bit

Necessitano di un circuito di Refresh

Consumano poco

Sono abbastanza veloci (da 10 a 70 ns)

Tipi di DRAM obsolete:

FP DRAM (fast page)

EDRAM (DRAM Evoluta)

EDO RAM (extended data output RAM).

Prof.Ing.S.Cavalieri

25

RAM DINAMICHE (DRAM)

SDRAM. Quando sono apparsi i Bus

con clock a 100 MHZ, si sono affermate

le memorie dinamiche di tipo sincrono

SDRAM. La Intel ha definito le

specifiche PC100 (PC 133).

RAM BUS (o RDRAM) hanno un

canale da 16 bit a 800 Mhz

Le DDR (double data rate) sono un tipo

di SDRAM che lavorano sui due fronti

del clock. Sono chiamate:

DDR 300 (riferendosi al doppio del clock

effettivo, 150 MHz)

PC 2400 (riferendosi alla banda 8 byte * 2 *

150 MHz) o PC 2100 (8*2*133 Mhz)

Prof.Ing.S.Cavalieri

26

RAM DINAMICHE (DRAM)

Attualmente esistono le DDR-II

Sono caratterizzate da più elevate velocità di clock rispetto a DDR (circa il

doppio), che a sua volta raddoppiò la velocità della SDRAM.

La maggiore velocità è legata alla presenza di buffer di I/O con clock

doppio del bus interno rispetto quello di funzionamento di ogni cella di

memoria

Si raddoppia il numero di bit letti ad ogni ciclo ed inviati al bus

interno

Esempi di Chip

DDR2-400: chip di memoria con frequenza di 100 MHz, buffer di I/O

con frequenza di 200 MHz.

DDR2-533: frequenza di 133 MHz, buffer di I/O a 266 MHz.

DDR2-667: frequenza di 166 MHz, buffer di I/O a 333 MHz.

DDR2-800: frequenza di 200 MHz, buffer di I/O a 400 MHz.

DDR2-1066: frequenza di 266 MHz, buffer di I/O a 533 MHz.

Prof.Ing.S.Cavalieri

27

RAM DINAMICHE (DRAM)

Sono montate su moduli (schedine):

SIMM (30 pin) single in line module; hanno una

doppia fila di contatti ma connessi a coppie, quindi è

come se avessero la metà dei contatti attivi; ogni

modulo ha parallelismo 1 byte (un 486 usa 4

banchi)

SIMM (72 PIN); i pin sono sempre organizzati a

coppie; ogni modulo supporta 4 byte (il 486 usa un

solo banco); montano le EDO RAM

DIMM (168 PIN) Dual Inline Memory Module;

tutti i pin sono indipendenti; gestisce 8 byte (un P6

usa un banco); Montano le SDRAM

DIMM (184 PIN); montano le DDR; sono uguali

come geometria alle DIMM 168 PIN, ma si

differenziano per il fatto di avere una sola tacca

DIMM con dissipatore per RDRAM

Prof.Ing.S.Cavalieri

28

RAM DINAMICHE (DRAM)

DIMM per DDR2. I moduli di memoria DDR2 hanno 240 Pin, e sono quindi

incompatibili con quelli DDR che hanno 184 pin.

PC2-3200: modulo di memoria con frequenza di clock di 200 MHz, transfer

rate di 400 MT/s, chip DDR2-400, e 3,200 GB/s per canale.

PC2-4200: modulo di memoria con frequenza di clock di 266 MHz, transfer

rate di 533 MT/s, chip DDR2-533, e 4,267 GB/s per canale.

PC2-5300: modulo di memoria con frequenza di clock di 333 MHz, transfer

rate di 667 MT/s, chip DDR2-667, e 5,333 GB/s per canale.

PC2-6400: modulo di memoria con frequenza di clock di 400 MHz, transfer

rate di 800 MT/s, chip DDR2-800, e 6,400 GB/s per canale.

PC2-8500: modulo di memoria con frequenza di clock di 533 MHz, transfer

rate di 1066 MT/s, chip DDR2-1066, e 8,533 GB/s per canale.

Prof.Ing.S.Cavalieri

29

Parametri Prestazionali

Esistono alcuni parametri di funzionamento, tipicamente raccolti

sotto il nome di timings

Alcune volte è possibile intervenire manualmente a variare i

timings, così da ottenere prestazioni superiori

Tra i vari timings:

CAS (Column Address Strobe) Latency (CL): indica il

numero di periodi di clock richiesti dalla memoria per

processare una richiesta.

A valori inferiori della latenza corrispondono prestazioni

superiori.

Prof.Ing.S.Cavalieri

30

Soluzioni Innovative per

Incrementare le Prestazioni

Velocità dei processori sempre più elevata, crea dei colli di

bottiglia sull’accesso in memoria

Da un pò di anni è stata sviluppata la tecnologia dual-channel

La quantità di dati traferibile dalla CPU alla RAM viene

duplicata, utilizzando due bus di dati a 64 bits

Sia Intel sia AMD la usano, con differenti implementazioni

Gli slot di memoria sulla scheda madre si riconoscono perchè

colorati

Prof.Ing.S.Cavalieri

31

ROM - Read Only Memory

Il termine ROM significa Read Only Memory.

Indicava originariamente il fatto che l'unico tipo di accesso in

queste memorie è la lettura (ovviamente la prima scrittura deve

essere possibile).

L’attuale ROM è:

Memoria Permanente

o Nella ROM l'informazione in essa contenuta rimane anche

quando manca la corrente.

o Nella ROM l'informazione rimane fino alla successiva

scrittura.

Memoria ad accesso casuale

Prof.Ing.S.Cavalieri

32

ROM - Read Only Memory

Le ROM vengono in genere utilizzate per memorizzare

programmi e dati di configurazione essenziali per il

funzionamento del computer che devono essere

memorizzati anche quando il computer è spento.

Bios

Esistono differenti tipi di ROM:

ROM non programmabili

PROM. ROM Programmabili

EPROM. Erasable Programmable ROM

EEPROM. Electrical Erasable Programmable ROM

Flash Memory

Prof.Ing.S.Cavalieri

33

ROM - Read Only Memory

ROM: sono delle reti combinatorie già predisposte in

fabbrica (tramite il processo di mascheratura). Hanno

alte capacità bassi costi.

PROM: sono delle reti combinatorie programmabili

con un dispositivo da laboratorio. Molto utili per

prototipi, possono essere programmate una sola volta.

EPROM: sono programmabili con un dispositivo da

laboratorio. Hanno una finestra di quarzo tramite cui

è possibile esporre il chip ai raggi U.V. e “cancellare

“ il contenuto.

Prof.Ing.S.Cavalieri

34

ROM - Read Only Memory

EEPROM: come le EPROM, ma cancellabili con

particolari cicli di segnalazione senza togliere dalla

piastra il chip. I tempi di cancellazione sono di norma

molto più lunghi di quelli di lettura.

Flash Memory: come le EPROM, ma la scrittura

avviene per blocchi e non per byte, molto

velocemente.

Non può essere usata come la RAM per via

della scrittura a blocchi

Si chiama flash perché il microchip è

organizzato in sezioni di celle cancellabili in un

colpo solo (flash).

Prof.Ing.S.Cavalieri

35

Memoria Cache

La memoria cache è generalmente gestita direttamente dalla CPU

tramite bus privati.

Lo scopo della memoria cache è quello di reperire informazioni

utilizzate recentemente senza doverle nuovamente prelevare dalla

RAM.

L'utilizzo della memoria cache rispetto la RAM è più vantaggioso

perché:

il bus di indirizzi e dati è locale e non deve essere utilizzato

quello comune, che potrebbe essere occupato da altri dispositivi

(ad esempio DMA), ritardando l'accesso alla RAM

il tempo di accesso alla cache per lettura/scrittura è molto più

basso di quello della RAM (generalmente il tempo di accesso

medio alla RAM è 50-70ns, mentre si può arrivare a valori

inferiori a 10ns per accedere alla memoria cache).

Prof.Ing.S.Cavalieri

36

Memoria Cache

L'uso della memoria cache prevede, però, opportuni accorgimenti

dovuti al fatto che la dimensione di una cache è notevolmente

inferiore a quella di una RAM

la dimensione tipica della RAM è di centinaia di MBytes,

mentre la cache ha dimensioni dell'ordine di alcune centinaia di

KBytes.

è impensabile poter memorizzare nella cache tutti i dati letti dalla

RAM, ma sarà necessario sovrascrivere alcuni dati contenuti nella

cache, per far spazio a nuovi dati da memorizzare.

Prof.Ing.S.Cavalieri

37

Memoria Cache

In particolare, si adotta la politica di sovrascrivere i dati più vecchi,

ossia quelli non utilizzati da più tempo.

La gestione della cache, può essere formalizzata nella seguente

maniera:

la CPU necessita di un particolare dato

la CPU ricerca il dato nella cache

se lo trova, lo legge e lo utilizza

se non lo trova, lo reperisce nella RAM e lo trasferisce nella

cache nella locazione più "vecchia", ossia da più tempo non

utilizzata.

Prof.Ing.S.Cavalieri

38

Memoria Cache

Attualmente le memorie cache hanno dimensioni medie di

256Kbyte, con picchi di 512Kbyte fino ad arrivare a valori

di alcuni Mbytes.

Potrebbe sembrare che quanto più grande è la cache, tanto

più conveniente sia per le prestazioni della CPU.

Questa affermazione è vera relativamente, in quanto,

aumentando la cache oltre certi limiti, il rapporto

prezzo/prestazioni diventa non conveniente.

Prof.Ing.S.Cavalieri

39

Memoria Cache

Per aumentare ulteriormente le prestazioni, si può:

Frammentare la cache

Trasferire una parte della cache all'interno della CPU

Esistono, dunque, Cache Multi-livello:

L1, di dimensioni minori (8KB...64KB): è in genere contenuta

all'interno del Core del processore e opera alla frequenza di clock CPU;

L2 (nelle CPU correnti compresa tra 128KB e 1MB): a seconda del tipo

di architettura è posta o all'interno del Core del processore oppure sulla

motherboard; opera a frequenze differenti a seconda del tipo di

architettura, variabili tra la frequenza di bus e quella di clock.

L3: generalmente è un'estensione della L2 (2 MB nel Pentium IV Extreme

Edition 3.2 GHz)

Il processore cerca prima nella cache interna L1 e poi in

quelle esterne L2, L3.

Prof.Ing.S.Cavalieri

40

Memorie STATICHE

Generalmente le memorie cache sono realizzate da

memorie statiche

La memoria statica è la memoria più veloce disponibile

attualmente

Sono caratterizzate da tempi di accesso dell'ordine delle

decine di nanosecondi (da 6 ns a 25 ns).

Sono costose e possono memorizzare solo 1/4 dei dati

rispetto le memorie dinamiche (DRAM).

A differenza delle DRAM, non occorre il rinfresco

periodico.

Prof.Ing.S.Cavalieri

41

Memorie STATICHE

Utilizzano per ogni bit un flip

flop.

Il singolo bit occupa molto

spazio (8 transistors).

Consuma molta energia.

E’ molto veloce (< 10 ns).

Ha un elevato costo per bit.

Prof.Ing.S.Cavalieri

42

CPU

Principi di Base

Blocchi Fondamentali: Memoria Cache, Registri,

ALU, Istruction Decoder and Control

Esempio di Funzionamento

Tecnologie di fabbricazione dei microprocessori: la

microelettronica

Tecnologie di fabbricazione dei microprocessori: la

meccanica

Road map dei microprocessori

Indicatori di prestazione

Prof.Ing.S.Cavalieri

43

CPU-Principi di Base

STRUTTURA DELLA ISTRUZIONE MACCHINA:

Si tratta di una stringa binaria che identifica il codice della operazione da

eseguire e le modalità per indirizzare gli operandi

Opcode o codici operativi

Un programma scritto in Opcode è assai difficile, si utilizza l’Assembly

ESECUZIONE DI UNA ISTRUZIONE MACCHINA:

l’esecuzione di un’istruzione avviene con una sequenza di

microistruzioni a livello circuitale associate all'istruzione

FASI CPU:

Ricerca (Fetch) e Esecuzione (Execute)

Prof.Ing.S.Cavalieri

44

CPU-Memoria Cache

La memoria, a rigore, non dovrebbe far parte dell'unità

centrale ma attualmente una tendenza che si va

consolidando e quella di fornire CPU che presentino al

loro interno banchi di memoria allo scopo di reperire

velocemente informazioni, senza dover accedere alla

memoria centrale.

Cache di Primo Livello L1 (alcune volte anche la L2)

Prof.Ing.S.Cavalieri

45

CPU-Registri Interni

Di numero e di caratteristica molto differenziate, i registri

interni di lavoro permettono all'unità centrale lo

spostamento, la manipolazione ed il deposito temporaneo

dei dati senza dover ricorrere alla memoria esterna.

I tipi di registri, le modalità di interconnessione e di

comunicazione fra i vari registi sono una caratteristica del

processore

Possiamo tuttavia individuare un set di registri essenziali

per il funzionamento di un qualunque processore, e che,

dunque, possono essere ritrovati in una qualunque

architettura.

Prof.Ing.S.Cavalieri

46

CPU-Registri Interni

Memory Address Register (MAR). E' il registro specializzato per

indirizzare la memoria. Durante l'esecuzione di un programma il

MAR contiene l'indirizzo della locazione di memoria centrale (esterna

alla CPU) alla quale si vuole accedere in quell'istante.

Program Counter (PC). E' il registro specializzato per contenere

l'indirizzo dell'istruzione che deve essere eseguita.

Memory Data Register (MDR). E' il registro da cui transitano tutti i

dati scambiati con la memoria esterna prima di venire smistati, in

base al loro significato, presso gli altri registri interni.

Instruction Register (IR). E' il registro che contiene la parte codice

operativo di un'istruzione, vale a dire quella sequenza di bit che

opportunamente decodificati determineranno le azioni che la CPU

deve eseguire.

Prof.Ing.S.Cavalieri

47

CPU-Registri Interni

Accumulatore. E' il principale registro di calcolo

dell'unità centrale: contiene sempre uno degli operandi e

il risultato dell'operazione

Pointer Registers (PRs). Sono registi specializzati per contenere

indirizzi, solitamente di quei sotto programmi ricorrenti con

particolare frequenza. Alcuni di essi possono venire specializzati a

funzioni particolari.

Uno di essi è lo stack pointer, che indirizza la zona di RAM in

cui è stato costruito lo stack. Lo stack e' definita come una

porzione di memoria gestita secondo una politica LIFO (Last In

First Out).

Risulta estremamente comodo per il salvataggio del

program counter in caso di interruzione (interrupt) o

Prof.Ing.S.Cavalieri

48

subroutine;

CPU-Registri Interni

Status Register. Con registro di stato si intende un registro il cui

contenuto è costituito da un insieme di flag aventi un significato

individuale, anche se può essere manovrato ed elaborato in parallelo.

Il significato dei vari flags costituenti il registro può differire a

seconda del microprocessore, ma avremo sempre alcuni flags

fondamentali:

CARRY. Viene manipolato dalle operazioni aritmetiche; viene

settato o resettato nel corso di un'istruzione di somma se si è

avuto o no un riporto.

OVERFLOW. Risente anch'esso dell'esito delle operazioni

aritmetiche; viene settato a uno se nel corso di una somma o

sottrazione si è avuto un trabocco della capacità dei registi.

Prof.Ing.S.Cavalieri

49

CPU-Unità Aritmetico Logica

ALU

Operazioni Aritmetiche: Somma in Complemento a 2

Operazioni Logiche: AND, OR e NOT

Operazioni sui Bit: Shift e Rotazione

Dati in Ingresso: il Contenuto dell'Accumulatore (sempre) e dei

registri interni della CPU (operandi residenti in memoria centrale

vengono trasferiti su registri temporanei)

Risultato dell'Operazione: Accumulatore

Uscite Collaterali: è fondamentale registrare alcune condizioni di

fine esecuzione delle operazioni di ALU al fine di determinare se

procedere con la successiva istruzione in memoria o con un’altra

opportunamente specificata.

risultato zero, negativo, riporto, overflow ……

registro di stato

Prof.Ing.S.Cavalieri

50

CPU-Instruction Decoder and

Control

E' il cuore del processore

Riceve come dato in ingresso il codice operativo dell'istruzione

presente nell'instruction register (IR).

Questo codice può essere pensato come l'indirizzo di partenza di un

microprogramma interno che agisce a livello circuitale minimo

componendo insieme, in modo opportuno, gruppi di

microistruzioni.

Queste ultime consistono in definitiva nell'emissione di una serie di

segnali e stati logici di controllo che servono:

a predisporre la ALU a compiere una particolare funzione aritmetico

logica

a smistare attraverso i bus interni i contenuti dei registri interessati

a svolgere i necessari test e gli eventuali scambi di dati con l'esterno.

Prof.Ing.S.Cavalieri

51

CPU-Instruction Decoder and

Control

Esempio di Microprogramma associato all'istruzione di Somma del

contenuto dell'accumulatore con il contenuto del MDR.

Questa operazione può essere scomposta in sette passi elementari:

1. Trasferimento del contenuto dell'accumulatore sul bus dati

interno alla CPU.

2. Trasferimento del contenuto del bus dati nella ALU.

3. Trasferimento del contenuto del MDR sul bus dati interno alla

CPU.

4. Trasferimento del contenuto del bus dati nella ALU.

5. Attivazione della logica di somma.

6. Trasferimento del contenuto della ALU (risultato della somma)

sul bus dati.

7. Trasferimento del contenuto della data bus nell'accumulatore

(che conterrà il risultato della somma).

Prof.Ing.S.Cavalieri

52

CPU - Fasi di Fetch e Execute

In qualunque processore l'esecuzione di una generica istruzione

avviene in due fasi differenti:

la fase di ricerca (FETCH): consiste nel prelievo dalla memoria

centrale dell'istruzione

la fase di esecuzione (EXECUTE), caratterizzata dalla decodifica

dell'istruzione e dall'attivazione del microprogramma ad essa

associato.

Prof.Ing.S.Cavalieri

53

CPU - Fasi di Fetch e Execute

Esempio: Supponiamo che l'istruzione sia di somma fra il contenuto

dell'accumulatore e il contenuto di una cella di memoria il cui

indirizzo sia dato direttamente dalla parte operando dall'istruzione

stessa.

Supponiamo cioè che la cella di memoria contenente l'istruzione da

eseguire sia strutturata come segue:

codice istruzione

Prof.Ing.S.Cavalieri

indirizzo RAM del secondo operando

54

CPU - Fasi di Fetch e Execute

Fase di ricerca (FETCH):

1.

Il contenuto del Program Counter (PC) è relativo all’indirizzo di

memoria che contiene l’istruzione.

2.

Il contenuto del Program Counter è inviato al MAR (Memory

Address Register) per operare il prelevamento dell'istruzione

all'indirizzo di memoria contenuto nel MAR.

3.

Il dato prelevato dalla memoria è riposto nel MDR (Memory

Data Register).

4.

Il contenuto del MDR, ossia l’istruzione, è messa nel Instruction

Register per essere decodificata.

5.

Il Program Counter viene incrementato per puntare all'istruzione

successiva.

Prof.Ing.S.Cavalieri

55

CPU - Fasi di Fetch e Execute

Ha inizio a questo punto la fase di esecuzione (EXECUTE):

1.

viene compreso che il secondo operando risiede in memoria

2.

la parte dell’istruzione relativa all’indirizzo del secondo

operando viene trasferita nel MAR

3.

L'effettivo operando, prelevato dalla memoria è posto nel MDR.

4.

L’operando viene presentato ad un ingresso della ALU.

5.

All'altro ingresso dell’ALU viene presentato il contenuto

dell'accumulatore.

6.

L'ALU, predisposta dall'Instruction Register ad eseguire la

somma, pone il suo risultato nell'accumulatore.

La fase di esecuzione è terminata ed il processore prosegue con la

fase di ricerca dell'istruzione successiva.

Prof.Ing.S.Cavalieri

56

Tecnologie di fabbricazione dei

microprocessori: la microelettronica

Il Canale (0,065μ/0,09μ/0,13μ/0,18μ): indica il più

piccolo spessore di silicio nel transistor che si riesce a

trattare con procedimenti fotochimici e quindi concorre a

determinare la densità di transistor che si può ottenere

0,065μ(micron)=65 nm (nanometri)

L’Area Chip (140mmq-300mmq): aumentando l’area del

chip si aumentano le funzioni logiche implementabili

Numero Transistor/Chip > Centinaia di Milioni - 1

Miliardo

Prof.Ing.S.Cavalieri

57

Tecnologie di fabbricazione dei

microprocessori: la meccanica

Il Packaging: il contenitore in cui è incapsulato il

chip della CPU deve avere ottime caratteristiche

meccaniche e termiche; si usano ceramiche

particolari.

La Piedinatura: l’aumento della memoria

indirizzabile, del parallelismo di trasferimento con la

memoria centrale, delle funzionalità avanzate hanno

determinato un crescente numero di punti esterni di

connessione (pin).

Il Socket: il socket è l’elemento meccanico di

interconnessione tra il chip e la scheda madre.

Il Raffreddamento: le sempre maggiori potenze

impegnate richiedono ventole montate su CPU e su

chassis più potenti e controlli automatici di

temperatura

Prof.Ing.S.Cavalieri

58

Tabella dei socket

Socket 5

Socket 7

SuperSocket 7

Socket 8

Slot 1

Slot A

Socket A

Socket 423/478

Socket 940

Socket T (LGA 775)

Socket M (µPGA478)

Socket P (µPGA478)

Prof.Ing.S.Cavalieri

59

Road map dei microprocessori

Socket

Canale

K6

Socket 7

K6 - II

Milioni

Transistor

Cache

L1

Cache

L2

Clock

CPU

FSB

0,35

64KB

0KB

2,33GHz

66MHz

Socket 7

0,25

64KB

0KB

3,00GHz

66MHz

K6-III

Super

Socket 7

0,25

64KB

256KB

4,50GHz

100MHz

DURON

SOCKET

A

0,18μ

25Mtr

128KB

64KB

1,2GHz

200Mhz

ATHLON

SOCKET

A

0,18μ

37Mtr

128KB

256KB

1,4GHz

266Mhz

ATHLON

XP

SOCKET

A

0,18μ

37,5Mtr

128KB

256KB

1,6GHz

266Mhz

ATHLON

MP

SOCKET

A

0,18μ

37,5Mtr

128KB

256KB

1,6GHz

266Mhz

AMD

Prof.Ing.S.Cavalieri

60

Road map dei microprocessori

Socket

Canale

Milioni

Transistor

Cache

L1

Cache

L2

Clock

CPU

FSB

CELERON

Coppermine

SOCKET

370

0,18μ

19Mtr

32KB

128KB

1,1GHz

100Mhz

CELERON

TUALATIN

SOCKET

370

0,13μ

28,5Mtr

32KB

256KB

1,2GHz

100Mhz

PENTIUM

III

Coppermine

SOCKET

370

0,18μ

28Mtr

32KB

256KB

1,1GHz

133MHz

PENTIUM

III

TUALATIN

Slot1/

SOCKET

370

0,13μ

28Mtr

32KB

256KB/

512KB

1,4GHz

133MHz

PENTIUM

IV

SOCKET

423

0,18 μ

42Mtr

8KB

256KB

2GHz

PENTIUM

IV

SOCKET

478

0,13 μ

42Mtr

8KB

512KB

2,8GHz

Pentium IV

EE

Socket 478

0,13 μ

169Mtr

8KB

512KB+

2MB (L3)

3,2GHz

INTEL

Prof.Ing.S.Cavalieri

200MHz

61

Ultime Soluzioni per

Incremento di Prestazioni

Soluzione DUAL CORE: unione di due processori indipendenti

Aumento di potenza di calcolo senza aumentare la frequenza di

clock

Motivo: aumento della frequenza di clock comporta consumi più

alti e problemi di riscaldamento

Si punta al parallelismo delle istruzioni eseguite in ogni ciclo di

clock

Esempi in casa Intel:

Core 2 Duo E6850 (Luglio 2007): Socket 775, 3GHz, 65nm,

L1=2x64KB, L2=4MB (la L2 è condivisa)

Prof.Ing.S.Cavalieri

62

Ultime Soluzioni per

Incremento di Prestazioni

Soluzione QUAD CORE: unione di 4 processori indipendenti

Esempi in casa Intel:

Core 2 Quad Q6700 (Luglio 2007): Socket 775, 2,66GHz, 65nm,

L1=4x64KB, L2=2x4MB (la L2 è condivisa tra ogni coppia di

processori)

Prof.Ing.S.Cavalieri

63

Indicatori di prestazione

Un Benchmark è un programma che consente di valutare

comparativamente le prestazione di due sistemi relativamente a:

Tempo di risposta (secondi)

Throughput (Numero di bit /secondo)

Fotogrammi / secondo

Alcuni programmi di Benchmark:

Stream (misura la banda delle RAM in Mbytes/s)

Video Giochi: 3D Mark, Mercedes Benz Truck Racing (fps)

Applicativi: Sysmark 2000 (sec)

Prof.Ing.S.Cavalieri

64

Sottosistema di I/O

I Bus: Bus di I/O

Interfacce: Seriali, Parallele, USB, FireWire

Controller

Schede Grafiche, Audio e di Acquisizione Video

Prof.Ing.S.Cavalieri

65

Bus di I/O

Il bus di I/O ha il compito di connettere la CPU alle periferiche di I/O

Esistono diverse tipologie che si differenziano per: numero di bit e

larghezza di banda (bit/sec)

Considerando l'architettura Intel, esistono i seguenti tipi di bus I/O:

ISA. Il termine ISA significa Industry Standard Architecture. La

prima versione del bus ISA era a 8 bit, presente ad esempio negli IBM

compatibili AT. Molto più recente ed utilizzato è il bus ISA a 16 bit.

16 bit @ 8 MHz picco 16MByte/s

EISA. Il termine significa Extended Industry Standard Architecture.

EISA è un'evoluzione del bus ISA ed è teoricamente compatibile con

questo. E' caratterizzato da prestazioni superiori rispetto il bus ISA,

principalmente dovute alla doppia capacità del bus e all'uso di un proprio

dispositivo DMA (Direct Memory Access).

Prof.Ing.S.Cavalieri

66

Bus di I/O

MCA. E' un bus proprietario IBM ed è derivato dal bus ISA. Il fatto di

essere proprietario implica l'incompatibilità con altri bus di I/O. E'

commercializzato in due versioni: a 16 e 32 bit. In termini pratici è

capace di trasferire circa 20 Mbit/secondo.

PCI (Peripheral Component Interconnect). I dati vengono trasferiti in

blocchi di 32 bit (a differenza dell'ISA caratterizzato da trasferimenti a

16 bit).

32 bit @ 33 MHz => 132 MByte/sec

32 bit @ 66 MHz => 264 MByte/sec (bus PCI 2.1, che lavora ad

una frequenza di 66 MHz)

AGP (Accelerated Graphic Port). Viene utilizzata esclusivamente per la

connessione a particolari schede video accelerate (ossia dotate di

processore interno che elabora informazioni visive).

Prof.Ing.S.Cavalieri

67

Interfacce

Esistono differenti connettori che permettono il collegamento con le

periferiche esterne (mouse, tastiera, stampante, etc.).

Generalmente tali connettori si collegano al bus di I/O. I più noti e

vecchi connettori sono:

COM1, COM2: RS 232, 9 e 25 poli maschio.

Porta Parallela. Sono connettori a 25 poli femmina.

Prof.Ing.S.Cavalieri

68

Interfaccia USB

E' l'acronimo di Universal Serial Bus;

Fino a 127 periferiche in catena.

L'USB è stato introdotto per fornire uno standard che superasse in

prestazioni le ormai vetuste porte seriale e parallela;

USB è quindi la soluzione ideale per le periferiche di media velocità

quali modem esterni, webcam, lettori CD-Rom esterni ecc.

E' possibile collegare le periferiche con PC

acceso

E'

possibile

fornire

direttamente

l'alimentazione ad alcuni tipi di periferiche.

Due Versioni:

USB 1.0: 12 Mbit/sec

USB 2.0: 480 Mbit/sec

Prof.Ing.S.Cavalieri

69

Interfaccia FireWire IEEE1394

Molti computer più recenti sono dotati di una porta per il

collegamento delle periferiche FireWire.

Si tratta di uno standard di comunicazione ideato da Apple e

sviluppato insieme a IEEE (e quindi conosciuto anche come standard

IEEE 1394).

Bus digitale di comunicazione che permette un

transfer rate massimo di 400 Mbit/secondo e di

collegare 64 periferiche in cascata;

Esiste la versione IEEE 1394b a 800 Mbps

La porta FireWire consente di collegare al

computer periferiche ad alta velocità, ad

esempio videocamere digitali, riproduttori

audio, unità Zip e altri dispositivi di

memorizzazione esterni.

Prof.Ing.S.Cavalieri

70

Controller

Esistono particolari periferiche, quali dischi fissi, CD-ROM, nastri

magnetici (o unità di back-up), e scanner, che necessitano di

particolari circuiti di interfaccia chiamati controller (controllori).

Il compito principale di un controllore è quello di garantire il

trasferimento dati tra il computer e la periferica, risolvendo alcuni

problemi tra cui l'adattamento di segnali elettrici, l'adattamento di

impedenza, il collegamento fisico tra il bus del computer e quello

relativo alla periferica, ecc.. Dunque il suo ruolo è essenziale al fine

di massimizzare il trasferimento dati.

cavo

Controller IDE e SCSI

Circuiti digitali

ed analogici

Prof.Ing.S.Cavalieri

Periferica

Parte elettromeccanica

71

Schede Video Acceleratrici

Le schede video permettono oggi di ottenere risoluzioni molto elevate ed

effetti grafici sofisticati.

Questi miglioramenti di grafica sono apprezzati dai giocatori di videogame e

da importanti professionisti web-designer e no.

Hanno memoria video DDR (circa 128MBytes) e un processore di immagini

Prof.Ing.S.Cavalieri

72

Schede Audio

Una serie di circuiti montati su una scheda di espansione per

computer. Le schede audio permettono di produrre e analizzare suoni

stereo di alta qualità utilizzando appositi programmi.

Possono essere a 16 o a 24 bit a seconda delle capacità di

campionamento e di elaborazioni che i circuiti utilizzati consentono.

Effetti dolby sorround (Creative Multi-Speaker Surround™-CMSS)

tra le più diffuse vi è la famiglia di schede SoundBlaster.

Prof.Ing.S.Cavalieri

73

Schede di Acquisizione Video

Elabora i dati (analogici/digitali) che arrivano da telecamere

(analogiche/digitali) e li trasforma in files in differenti formati

selezionabili dall'utente (ad esempio AVI, MPEG).

Il processore on-board permette di realizzare effetti di montaggio

real-time.

Prof.Ing.S.Cavalieri

74

Periferiche

Stampanti

Scanner

Web Cam

Macchine Fotografiche Digitali

Prof.Ing.S.Cavalieri

75

Memorie di Massa

Floppy

Hard Disk

PenDrive

CD ROM

CD RW

DVD ROM

DVD RW

Prof.Ing.S.Cavalieri

76

….per diventare esperti dei PC !!

Metodi di I/O: Interrupt e DMA

La Scheda Madre

Il ChipSet

Il BIOS

Prof.Ing.S.Cavalieri

77

Metodi di I/O: Interrupt

L'attività che svolge la CPU non è mai continua ma viene sempre interrotta

da particolari segnali provenienti principalmente da dispositivi esterni alla

CPU stessa.

Tali interruzioni hanno lo scopo di comunicare alla CPU la necessità che essa

esegua particolari programmi.

Ad esempio uno dei più comuni interrupt è relativo all'aggiornamento

dell'ora e della data interna al computer.

La CPU riceve circa 18 volte al secondo un segnale di interruzione che

la obbliga ad eseguire il programma associato di aggiornamento dell'ora

e della data.

In termini tecnici queste interruzioni prendono il nome di INTERRUPT.

Ogni interrupt è caratterizzato da una sua priorità al fine di poter gestire la

contesa nel caso in cui più interrupt arrivino contemporaneamente alla CPU.

Ad ogni interrupt è poi associato sempre il programma che deve essere

eseguito.

Prof.Ing.S.Cavalieri

78

Metodi di I/O: Interrupt

All'arrivo di un interrupt, la CPU deve eseguire le seguenti funzioni:

1. deve salvare nello stack lo stato corrente del programma che

stava eseguendo fino a quel momento (lo stato è dunque

rappresentato dal contenuto di alcuni registri quali il Program

Counter)

2. deve identificare l'interrupt ed eseguire il programma di interrupt

ad esso associato

3. alla fine dell'esecuzione del programma di interrupt, deve

prelevare lo stato dallo stack e ripristinare lo stato corrente prima

che venisse l'interrupt

4. continuare l'esecuzione dallo stato appena ripristinato

Prof.Ing.S.Cavalieri

79

Metodi di I/O:

Direct Memory Access (DMA)

Il DMA è una tecnica di gestione del bus che conduce i dati nella

memoria RAM, in base alla quale non è necessario l'intervento della

CPU per tale trasferimento, ma è un particolare dispositivo DMA che

si occupa di effettuare tale trasferimento, alleggerendo la CPU.

Il DMA viene utilizzato quando si hanno periferiche veloci che

devono accedere alla memoria. In tal caso l'accesso potrebbe essere

rallentato dalla CPU, nel caso in cui essa non sia particolarmente

veloce o sia occupata in altri lavori.

CPU

RAM

DMA

I/O

bus

Prof.Ing.S.Cavalieri

80

La Scheda Madre

Prof.Ing.S.Cavalieri

81

Il Chip Set

Viene detto "chipset" un gruppo di circuiti integrati (in gergo

elettronico, chip) che sono direttamente saldati sulla scheda madre e

si incaricano di tutte le operazioni di normale gestione, quali:

attività sul bus: controllo e gestione del flusso di dati tra i vari

componenti

il risparmio energetico

Dato che il chipset fa da intermediario tra la CPU e tutti (o quasi) i

sottosistemi, la sua architettura influenza molto le prestazioni del

sistema.

Prof.Ing.S.Cavalieri

82

Il Chip Set

Il chipset fa parte integrante della scheda madre, e non può essere

aggiornato.

In generale, un chipset è progettato per una famiglia di processori e

per una tecnologia di RAM,

quindi supporta le frequenze di CPU, le velocità di frontside bus

(FSB) e le velocità del bus di memoria corrispondenti ai

processori e ai moduli di memoria che entrano in commercio

durante il periodo di vita del chipset.

Prof.Ing.S.Cavalieri

83

Il Chip Set

CPU

Sono due i chip:

Northbridge: scambio

dati tra CPU, RAM,

Comparto Grafico

AGP BUS

NORTH

BRIDGE

AGP

Memory Bus

SRAM

PCI Bus

SouthBridge: I/O, slot

PCI, porte

SOUTH

BRIDGE

LAN

SCSI

ISA

USB

Prof.Ing.S.Cavalieri

BIOS

84

BIOS

Il nome BIOS significa Basic Input Output System, ossia sistema di base

per ingressi e uscite.

Il BIOS è essenzialmente un "software", ossia un programma. Esso é

contenuto in un chip di memoria non volatile

EEPROM o le Flash Memory

Le funzioni svolte dal BIOS sono essenzialmente:

1. Funzione di Avvio del Computer, Boot

Funzione di POST (Power-On Self Test)

Beep che codificano eventuali errori o anomalie

Caricamento drivers (es.scheda video)

Check memoria

Caricamento S.O. (da disco di boot)

2. Funzione di Memorizzazione di Configurazione Hardware e di

Parametri del ChipSet.

Prof.Ing.S.Cavalieri

85

BIOS

Avvio del Computer

Quando si accende il PC, si inizializza l'alimentatore interno. Non

appena la tensione si stabilizza il chipset invia un comando di reset del

processore.

Il comando reset richiede alla CPU di eseguire l'istruzione posta sempre

in una locazione fissa prestabilita nella ROM del BIOS e denominata

indirizzo di jump.

La CPU esegue l'istruzione, che copia in memoria i programmi del

BIOS e inizia l'esecuzione del BIOS.

Prof.Ing.S.Cavalieri

86

BIOS

Avvio del Computer

La prima azione eseguita dal programma di BIOS è il POST (Power-On

Self-Test):

Il processo POST verifica e controlla la configurazione hardware

memorizzata nelle informazioni di configurazione del BIOS.

Nel caso in cui dovesse rilevare un problema invia indicazioni

acustiche per mezzo di uno o più beep o beep code, attraverso

l'altoparlante del sistema, per indicare la natura del problema o

visualizzare un messaggio d'errore e il processo di boot si arresta.

Se il POST non incontra problemi, il processo di boot continua.

Il BIOS cerca il BIOS dell'adattatore video e lo attiva. Quasi tutti i

dispositivi periferici di un PC dispongono di un proprio BIOS. Le

informazioni sulla scheda video sono visualizzate sullo schermo del

monitor.

informazioni della scheda video, BIOS della scheda video,

produttore e versione.

Prof.Ing.S.Cavalieri

87

BIOS

Avvio del Computer

Vengono inizializzate la routine del BIOS delle periferiche presenti,

oltre la scheda video.

Il BIOS effettua poi una serie di test nel sistema, inclusa la dimensione

della memoria rilevata.

Un contatore progressivo visualizza nello schermo la memoria

rilevata e verificata.

Il BIOS verifica che i dispositivi elencati nei dati di configurazione

siano presenti e funzionanti.

viene visualizzato un messaggio che comunica che il dispositivo è

stato trovato, configurato e verificato.

Se il BIOS supporta la tecnologia PnP (Plug and Play), qualsiasi

dispositivo PnP rilevato sarà configurato.

vengono visualizzate sullo schermo tutte le informazioni dei

dispositivi, tuttavia scorrono in modo troppo veloce per poter

essere lette.

Prof.Ing.S.Cavalieri

88

BIOS

Avvio del Computer

Alla fine della sequenza di test e configurazione, il BIOS visualizzerà

una schermata che riassume i dettagli del PC verificati dal BIOS, per

indicare che il sistema è pronto per l'uso.

Il BIOS dovrà trovare il sistema operativo ed essere in grado di

accedervi, per poterlo attivare.

I dati di configurazione memorizzati nel BIOS contengono un

parametro che indica le unità disco (floppy, hard disk o CD-ROM)

e l'ordine di accesso per il caricamento del sistema operativo.

Se il programma di boot non viene trovato nel primo dispositivo

elencato, verrà ricercato nel dispositivo successivo e così via;

se non si trova alcun dispositivo di boot la relativa sequenza si

arresta e viene visualizzato un messaggio di errore: "Non è

disponibile alcun dispositivo di boot".

Prof.Ing.S.Cavalieri

89

BIOS

Memorizzazione Configurazione

Il BIOS memorizza la configurazione hardware del computer (periferiche

non plug&play) e i parametri del chipset e ne permette all’utente la modifica.

Programma di Configurazione: tasto DEL all'avvio

In genere ogni versione di BIOS permette di intervenire su taluni parametri

del chipset ma non su altri.

Esempio: alla voce Chipset Features Setup (o Advanced Chipset Setup)

e possibile intervenire sui tempi di accesso alla memoria e su altri

parametri del chipset, così da migliorare anche sensibilmente le

prestazioni del computer;

C'è il rischio di impostare alcuni parametri troppo performanti per l'hardware

installato e il sistema si bloccherà durante il funzionamento:

basterà rientrare nel Setup del BIOS (premendo, in genere, il tasto DEL

all'avvio) e reimpostare i valori precedentemente usati.

Prof.Ing.S.Cavalieri

90

BIOS

Interfaccia Sistema Operativo

L'hardware, cioè la parte elettronica del PC, può presentare notevoli

differenza da costruttore a costruttore o da modello a modello.

Se il S.O. deve ad esempio recuperare un file dal disco rigido, esegue

tale lettura "chiedendo" al BIOS di leggere il file, senza occuparsene

direttamente.

Il BIOS contiene programmi usati dal sistema operativo e software

applicativo per interagire con l'hardware.

Visto che il BIOS è strettamente legato all’hardware, è facile

comprendere è che ogni diverso computer possiede un diverso BIOS.

Non è possibile cioè utilizzare il BIOS del computer modello xyz nel

computer modello hkw.

Prof.Ing.S.Cavalieri

91

Produttori di BIOS

Award, AMI (America Megatrends, Inc.) e Phoenix producono i BIOS più

noti.

Come la maggior parte dei produttori, forniscono le ROM del BIOS in

licenza d'uso alle case costruttrici di schede madri, mentre il servizio di

supporto del BIOS compete generalmente a produttori delle schede.

In passato AMI era l'unico BIOS per Intel, il principale produttore di

processori e schede madri.

Attualmente, oltre l'60% delle schede madri sono Intel e adottano il BIOS

Phoenix.

Nel 1998 Phoenix ha acquistato Award e, pertanto, il BIOS Award viene

distribuito con marchio Phoenix.

Prof.Ing.S.Cavalieri

92