Sistemi Elettronici

Programmabili

La memoria principale

Sistemi Elettronici Programmabili: La Memoria Principale

6-1

Memoria

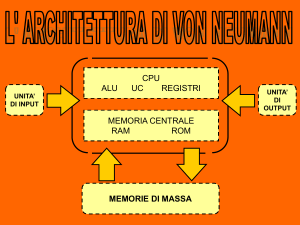

• Memoria interna o principale

– ROM, PROM

– RAM (SRAM, DRAM)

• Memoria esterna o ausiliaria

– Dischi rigidi (magnetici, ottici, magneto-ottici)

– Floppy

– Nastri

– Cassette

Sistemi Elettronici Programmabili: La Memoria Principale

6-2

Le Memorie RAM

Random Access Memory

Tempo di accesso indipendente dalla posizione del dato

letto/scritto

Caratteristiche

• Dimensione = numero di bit o byte. Alcune volte fornita

l’organizzazione (16Kx8 indica 16384 locazioni da 8 bit)

• Velocità = tempo di accesso. Tempo che trascorre dalla

richiesta del dato al momento in cui il dato è disponibile.

• Potenza = assorbimento medio di potenza. Utile anche

consumo di potenza in stand-by per memorie con batteria.

• Costo (maggiore densità = minor costo per bit)

• Integrazione = densità di memoria per chip. Maggiore

integrazione = maggiore affidabilità e minor costo.

Sistemi Elettronici Programmabili: La Memoria Principale

6-3

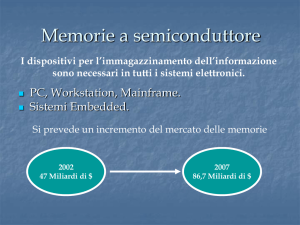

Tipologie di Memorie allo stato

solido

RAM (Random Access Memory)

Volatili

Non Volatili

SRAM (Static RAM)

Flip-Flop

Statiche

Velocissime

Cella Grande

Costo per Bit

Taglio ~ 100 Kbit

Programmate in fonderia

Costo per Bit

DRAM (Dynamic RAM)

Capacità

Dinamiche (Refresh)

Veloci

Cella piccola

Costo per Bit

Taglio ~ 100 Mbit

SDRAM (Synchronous DRAM)

Capacità

Accesso a burst

Self Refresh

ROM (Read Only Memory)

Masked ROM

OTP (One Time Programmable)

Fuse - Antifuse

EPROM (Electrically Programmable ROM)

MOS Floating Gate

Cancellabili mediante UV

EEPROM (Electrically Erasable Programmable ROM)

MOS Floating Gate

E-P Random Access

R Lenta, E-P molto lenti

Costo per Bit

Flash

MOS Floating Gate

P Random Access

E a banchi

R Lenta, P molto lenti, E lentissimo

Costo per Bit

Taglio ~ 100 Mbit

Sistemi Elettronici Programmabili: La Memoria Principale

6-4

Memorie Statiche (SRAM)

• La cella di base (memorizzazione di 1 bit)

è costituita da 6 o 4 transistor

• Tempi di accesso bassi (10 ns)

• Interfaccia semplice

• Occupazione notevole

• Consumo di potenza non trascurabile

• Utilizzata per i registri interni e per piccole

memorie

Sistemi Elettronici Programmabili: La Memoria Principale

6-5

Static RAM (SRAM)

8

Address BUS

Data In BUS

Data_IN BUS

Word 0

Word 1

1010111

10

8

Address

BUS (5..0) 6

CS

RAM

CS

R/W

RAM 0

RAM 1

CS

Word 1023

8

R/W

RAM 2

Data Out BUS

Select

CS

RAM 3

CS

ENB

S

IN

2x4

Decoder

Q

FF

R

Address

2 BUS (7..6)

Q’

CPU

Sistemi Elettronici Programmabili: La Memoria Principale

Data_OUT

BUS

8

6-6

SRAM bus dati doppio

Data IN BUS (2..0)

MC

MC

MC

MC

MC

MC

MC

MC

MC

MC

MC

MC

CS

ADDR_1

ADDR_0

2x4

Decoder

R/W

Data OUT BUS (2..0)

Sistemi Elettronici Programmabili: La Memoria Principale

6-7

SRAM bus dati singolo

MC

MC

MC

MC

MC

MC

MC

MC

MC

MC

MC

MC

CS

ENB

R/W

ENB

ADDR_0

2x4

Decoder

ENB

ADDR_1

Data BUS (2..0)

Sistemi Elettronici Programmabili: La Memoria Principale

6-8

Indirizzamento Bi-dimensionale

Address

BUS

Indirizzo

della Riga

Decoder

di Riga

Indirizzo della

Colonna

Decoder

di Colonna

Parola

Indirizzata

Sistemi Elettronici Programmabili: La Memoria Principale

6-9

SRAM 512K x 8

Sistemi Elettronici Programmabili: La Memoria Principale

6-10

Comandi di Lettura/Scrittura

Sistemi Elettronici Programmabili: La Memoria Principale

6-11

Ciclo di Lettura SRAM

• Si fornisce l’indirizzo

• Si abilita il chip (CE)

• Si abilita l’uscita (OE)

Il tempo d’accesso tACC è il tempo

necessario per avere stabile

l’uscita una volta stabilizzati i

segnali di controllo d’ingresso

Il tempo minimo richiesto per

l’operazione di lettura è indicato

con tRC (tempo di ciclo di lettura)

Nelle SRAM tipicamente tACC=tRC

Sistemi Elettronici Programmabili: La Memoria Principale

6-12

Ciclo di Scrittura SRAM

La scrittura può essere svolta in 2 modi

•

•

1.

2.

3.

4.

5.

Controllata da WE (il comando di scrittura è un

impulso su WE)

Controllata da CE (il comando di scrittura è un impulso

su CE)

Viene fornito l’indirizzo

Viene abilitato il chip

Vengono forniti i dati

Viene dato il comando di scrittura (che deve essere

mantenuto per un tempo minimo indicato con tWP

La durata minima del ciclo di scrittura si indica con tWC

(=tWP per le SRAM)

Sistemi Elettronici Programmabili: La Memoria Principale

6-13

Memorie Dinamiche (DRAM)

• L’informazione è rappresentata dalla

carica (50pC circa) immagazzinata in

un condensatore integrato

• 1 singolo transistor viene utilizzato per

le operazioni di

lettura/scrittura/mantenimento

• Grande capacità a costi contenuti

• Resistenze di perdita => il

condensatore si scarica entro pochi

ms.

• Serve ciclo di rinfresco

dell’informazione (refresh) con circuito

dedicato interno => memorie più lente

• Grandi dimensioni = tanti indirizzi =>

indirizzo riga e colonna separati

La linea Plate Line

è collegata a massa

La linea Word Line

è collegata al gate

La linea Bit Line è

collegata al drain

Sistemi Elettronici Programmabili: La Memoria Principale

6-14

Memorie Dinamiche (DRAM)

Sistemi Elettronici Programmabili: La Memoria Principale

6-15

Ciclo di Lettura per le DRAM

• tRC>tACC

• Necessità di refresh

Sistemi Elettronici Programmabili: La Memoria Principale

6-16

Lettura/Scrittura DRAM

1.

2.

3.

4.

5.

6.

7.

Si immette sul bus indirizzi il Row Address

Si attiva il segnale RAS (Row Address Strobe) che agendo su un

apposito Latch memorizza il Row Address ad uso interno

Il valore memorizzato nel Latch viene decodificato ed identifica

una specifica riga (Row) nella matrice di memoria.

I segnali ed il bus vendono disasseriti, è finita la prima fase

dell'accesso

Si immette sul bus indirizzi il Column Address

Si attiva il segnale CAS (Column Address Strobe) che agendo su

un apposito Latch memorizza il Column Address

Il valore immagazzinato permette di individuare la colonna dove si

trova il dato. L'incrocio tra colonna e riga individua univocamente

la cella di memoria ed il suo contenuto viene inviato sul bus dati in

caso di lettura, altrimenti il contenuto del bus dati viene scritto

nella cella in caso di scrittura.

USO DI UN CONTROLLORE ESTERNO DEDICATO ALLE DRAM

(BRIDGE di BUS nei PC)

Sistemi Elettronici Programmabili: La Memoria Principale

6-17

Memoria Dinamica Sincrona (SDRAM)

• Utilizzo di clock esterno per la sincronizzazione delle

operazioni di I/O.

• Incremento delle prestazioni

• Maggiore efficienza

• Complessi modi operativi, pipeline interne e trasferimenti

burst.

• I chip di SDRAM in commercio hanno frequenze di

funzionamento dai 66MHz fino ai 200MHz.

• I moduli di memoria che utilizzano la SDRAM hanno il

formato DIMM, la banda massima teorica delle memorie

DIMM PC100 è di 800MB/s e 1064MB/s per le PC133

Sistemi Elettronici Programmabili: La Memoria Principale

6-18

Località

•

•

1.

2.

Il divario di prestazioni tra CPU e DRAM è cresciuto (vel.

DRAM +22% anno, vel. CPU +50,100% anno)

L’analisi sull’esecuzione dei programmi mostra che i

riferimenti alla memoria godono di 2 proprietà:

Località spaziale: è altamente probabile che l’istruzione

successiva sia contigua a quella che si sta eseguendo

Località temporale: poiché tutti i programmi hanno dei

cicli in cui si fa riferimento a dati è probabile che

altamente probabile che nel prossimo futuro venga di

nuovo eseguita la stessa istruzione o si faccia riferimento

allo stesso dato

La località suggerisce di utilizzare una memoria interna

veloce ma costosa (cache con SRAM) per le parti alle

quali probabilmente si farà riferimento nel prossimo futuro

(strategie di caching), interposta tra la CPU e la memoria

principale

Sistemi Elettronici Programmabili: La Memoria Principale

6-19

Gerarchia

• La località suggerisce l’introduzione di una

gerarchia nella memoria

• Al livello più alto ci sono i registri della CPU

• Al livello più basso le memorie di massa

Sistemi Elettronici Programmabili: La Memoria Principale

6-20

Gerarchia

• Il processore genera un indirizzo

• Si controlla la memoria di livello più alto (cache)

• Se il dato è contenuto nella cache si ha un hit ed

il dato viene trasmesso alla CPU

• In caso contrario si ha un miss e si passa alla

memoria di livello inferiore

• h = tasso di hit, il rapporto tra il numero di hit ed i

riferimenti totali alla memoria

• m = tasso di miss, il rapporto tra il numero di

miss ed i riferimenti totali alla memoria (m=1-h)

Sistemi Elettronici Programmabili: La Memoria Principale

6-21

Gerarchia

• I trasferimenti avvengono in blocco tra

livelli adiacenti: quando un dato viene

trovato a livello inferiore viene trasferito un

blocco che lo contiene in quello superiore

• Nel caso di miss multipli vengono trasferiti i

blocchi tra livelli contigui di dimensioni

sempre minori mano a mano che si sale di

gerarchia

Tempo di hit: tempo necessario per accesso livello più alto th

Penalizzazione di miss: tempo necessario al trasferimento del

blocco e per la trasmissione del dato alla CPU tp

Tempo medio di accesso alla memoria: t = h*th + mtp

Sistemi Elettronici Programmabili: La Memoria Principale

6-22