Diopsis: un "System on Chip" multiprocessore per intelligenza

ambientale con architettura "mAgic VLIW floating-point DSP"

Pier S. Paolucci

INFN Roma, Dip. Fisica Univ. Roma “La Sapienza”, P.le Aldo Moro 5, 00185 Roma

ed ATMEL ROMA, Via Vito Giuseppe Galati 91, 00155 Roma, Italy

Ben Altieri, Federico Aglietti, Stefano V. Basile, Piergiovanni Bazzana, Sergio

Bruzzone, Alessandro Catasta, Antonio Cerruto, Maurizio Cosimi, Andrea Michelotti,

Elena Pastorelli, Silvia Piria, Enrico Remondini, Andrea Ricciardi, Fabrizio Rosciarelli

ATMEL ROMA, Via Vito Giuseppe Galati 91, 00155 Roma, Italy

Yves Fusella

ATMEL, Zone Industrielle 13106 Rousset cedex, France

Philippe Kajfasz

THALES Communications 66, rue du Fossé Blanc – BP 156 - 92231 Gennevilliers

Cedex, France

Premessa

I sistemi su silicio multiprocessore sono stati classificati come la prossima frontiera della

progettazione, sia perché permettono di creare applicazioni complete con funzionalità

completamente nuove, che per la complessità di progetto.

Presentiamo un caso reale, lo sviluppo e l'integrazione del nostro core "mAgic VLIW DSP"

(un processore specializzato nel calcolo numerico in virgola mobile nel dominio complesso

con capacità di elborazione di un miliardo di operazioni al secondo in virgola mobile) e la sua

integrazione nel System on Chip DIOPSIS 740 (nickname durante lo sviluppo: JANUS [1]).

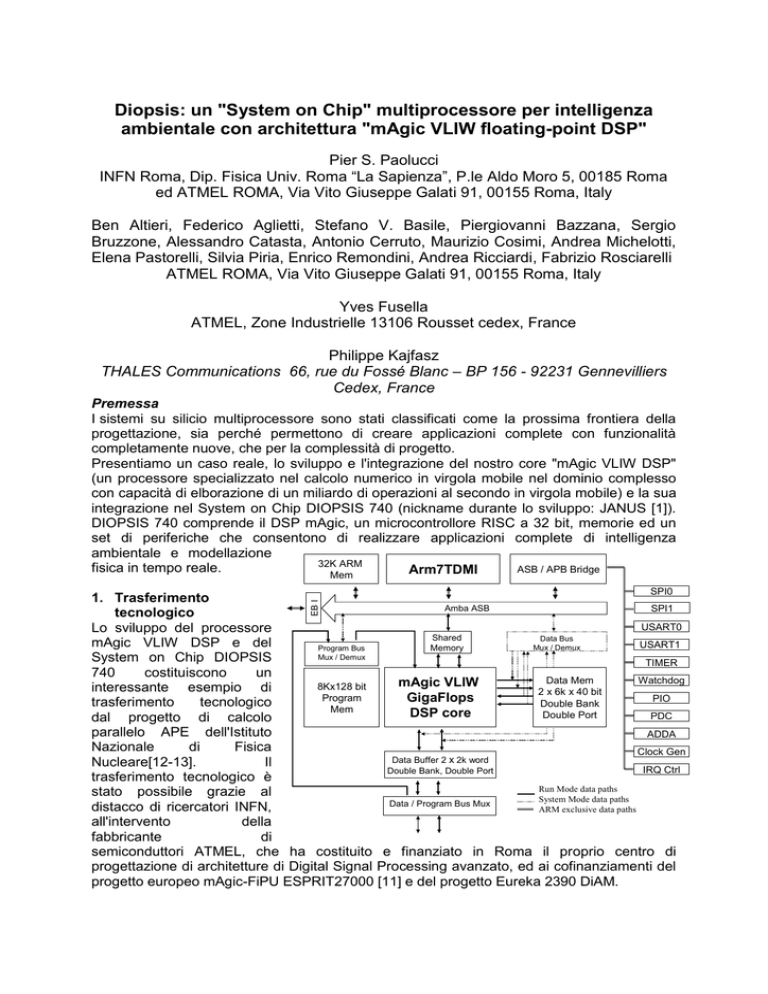

DIOPSIS 740 comprende il DSP mAgic, un microcontrollore RISC a 32 bit, memorie ed un

set di periferiche che consentono di realizzare applicazioni complete di intelligenza

ambientale e modellazione

32K ARM

fisica in tempo reale.

ASB / APB Bridge

Arm7TDMI

Mem

SPI0

EB I

1. Trasferimento

Amba ASB

SPI1

tecnologico

USART0

Lo sviluppo del processore

Shared

Data Bus

mAgic VLIW DSP e del

USART1

Mux / Demux

Memory

Program Bus

Mux / Demux

System on Chip DIOPSIS

TIMER

740

costituiscono

un

Data

Mem

Watchdog

mAgic VLIW

8Kx128 bit

interessante esempio di

2 x 6k x 40 bit

Program

PIO

GigaFlops

trasferimento

tecnologico

Double Bank

Mem

DSP core

Double Port

PDC

dal progetto di calcolo

parallelo APE dell'Istituto

ADDA

Nazionale

di

Fisica

Clock Gen

Data Buffer 2 x 2k word

Nucleare[12-13].

Il

IRQ Ctrl

Double Bank, Double Port

trasferimento tecnologico è

Run Mode data paths

stato possibile grazie al

System Mode data paths

Data / Program Bus Mux

distacco di ricercatori INFN,

ARM exclusive data paths

all'intervento

della

fabbricante

di

semiconduttori ATMEL, che ha costituito e finanziato in Roma il proprio centro di

progettazione di architetture di Digital Signal Processing avanzato, ed ai cofinanziamenti del

progetto europeo mAgic-FiPU ESPRIT27000 [11] e del progetto Eureka 2390 DiAM.

2. Diopsis 740

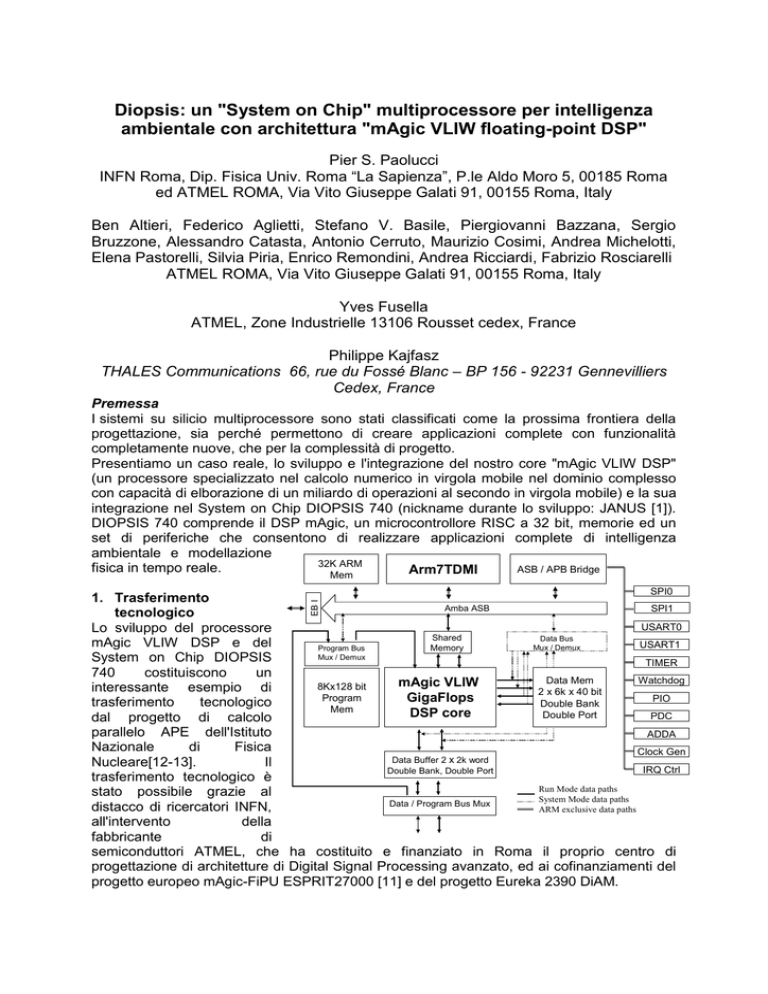

DSP Reg Files:

mAgic VLIW floating point

Diopsis 740 è un sistema su silicio a

DSP Reg Files:

mAgic VLIW floating point

2 * 8 Ports *

DSP SW Core: 15

2

*

8

Ports

*

DSP

SW Core: 15

doppio processore che integra il DSP

256

40bit

bit

op/cycle,390

390

Kgate

256 Regs

Regs ** 40

op/cycle,

Kgate

floating-point mAgic da 1 GFLOPS,

sviluppato da ATMEL ROMA, il

RISC

RISCSRAM:

SRAM:

4 4* *11Port

controllore RISC a 32 bit ARM7TDMI™,

Port**

8K

*

8

bit

8K * 8 bit

2 Megabit di Static RAM ed un set di

RISC

RISC

periferiche. La figura accanto mostra il

PERIPHERALS:

PERIPHERALS:

piazzamento in tecnologia ATMEL 180

135Kgate

Kgate

135

nm CMOS a cinque livelli di alluminio.

ARM7TDMI32

32 BIT

BIT

ARM7TDMI

Esclusi i pad, questa implementazione di

RISCCORE

CORE

RISC

Diopsis 740 occupa 39 mm2. Pad inclusi,

l’area finale del die è di 55 mm2 con 243

IO funzionali. Il package è un 352 Ball

Grid Array. La frequenza operativa è di

DSP Data SRAM:

DSP Progr SRAM:

Data* SRAM:

Progr

100 MHz, e la capacità di elaborazione è

2DSP

* 1 Port

* SRAM: 8 DSP

* 2 Ports

2 * *164

Port

2 Ports

2K8 ** 40

bit *

8K

bit *

di 1.5 GOPS ed 1 GFLOPS grazie al

2K * 40 bit

8K * 64 bit

parallelismo

interno

Very

Long

Instruction Word, gestito in modo totalmente trasparente per l’utente dal software di gestione

dell’architettura VLIW. Diopsis 740 consuma meno di 1.2 W in condizioni “worst case”.

3. mAgic VLIW Floating-point DSP

Il dominio applicativo ideale per l’architettura mAgic VLIW DSP è l’elaborazione numerica al

alta prestazione di segnali. Le componenti di controllo della interfaccia utente e di sistema

sono affidate, nelle applicazioni di DIOPSIS 740, principalmente al processore RISC. Questa

prima realizzazione è dedicata alle applicazioni in virgola mobile, e specialmente ai calcoli

che richiedono aritmetica nel dominio dei numeri complessi, con elevato range dinamico e

massima precisione numerica. Un esempio: algoritmi a shift di fase nel dominio della

frequenza. Una caratteristica importante della architettura mAgic è la gestione indolore del

parallelismo Very Long Instruction Word. Un sistema di traduzione automatico garantisce la

conversione

di

un

assembler lineare “RISC

like”

in

un

codice

eseguibile che sfrutta

pienamente

il

parallelismo a livello di

istruzione. I programmi

scritti

nell’assembler

RISC like di mAgic,

composto da operazioni

di

calcolo

registroregistro e operazioni di

trasferimento

tra

memorie e registri non

richiedono

nessuna

annotazione temporale a

carico

del

programmatore. In altri

termini, il programmatore non specifica le istruzioni da eseguire in parallelo: il motore di

ottimizzazione software esegue autonomamente la parallelizzazione.

mAgic opera su dati in formato IEEE 754 esteso a 40 bit, e su dati interi a 32 bit. Sul chip

sono montate memorie dati doppia porta, doppio banco (17K locazioni a 40 bit) ed una

L Memory

4. Piattaforma di sviluppo per Intelligenza ambientale e modellazione fisica

Per intelligenza ambientale si intende la integrazione di sistemi con elevata capacita' di

elaborazione nell'ambiente che ci circonda, spesso basate sull’uso di un array di sensori o

trasmettitori. Un sotto-insieme di tali applicazioni particolarmente rilevante dal punto di vista

applicativo prende il nome di beam-forming, ed è stato fino ad ora utilizzato in applicazioni

come la prospezione sismica, l’ecografia medica, e radar avanzati. DIOPSIS 740 consente di

estendere ad applicazioni “consumer” le tecniche di beam-forming adattivo. Le applicazioni

“consumer” della intelligenza dámbiente hanno l’obiettivo di semplificare la nostra interazione

con l'ambiente stesso (esempi: sistemi vivavoce e comando vocale di altissima qualita' per

ufficio, casa od automobile, che utilizzino una molteplicità di microfoni) di effettuare

R Memory

memoria programma di 8K locazioni a 128 bit. Un uso efficiente della memoria programma è

ottenuto per mezzo di un sistema di compressione software/decompressione hardware

brevettato. Il sistema DyProDe (Dynamic Program Decompression Device) è inserito come

singolo stadio di pipeline immediatamente dopo lo stadio di fetch della istruzione. Il sistema

DyProDe è estremamente economico (meno di 30K gate). Otteniamo una densità di codice

equivalente a 4 bit per operazione su tipiche routine di DSP come trasformate veloci di

Fourier (FFT) e filtri FIR.

Questa istanza di mAgic ha un totale di 18 unità funzionali indipendenti. Un massimo di 15

operazioni per ciclo può essere eseguita simultaneamente. Il register file dati permette di

leggere e scrivere 16 dati per ciclo da un set di 512 registri dati a 40 bit, alimentando un

blocco operatori capace di eseguire 10 operazioni aritmetiche in virgola mobile per ciclo.

Durante lo stesso ciclo un

secondo bando di register

L Memory

R Memory

file multiporte consente ad

4 5 6 7

4 5 6 7

I

Q

una unità di generazione

0 1 2 3

0 1 2 3

multipla di indirizzi di

generare

gli

indirizzi

necessari a trasferire 4 dati

Mul4 Conv2

FP/I Mul2

FP/I

FP/I Mul3

Conv1 FP/I Mul1

per ciclo tra le memorie ed il

Div1

Div2

Sh/Log1

register file dati. L’accesso

*

*

* Sh/Log2

*

alla memoria esterna è

gestito in totale parallelismo

FP/I Cadd1

FP/I Cadd2

alle

attività

del

core

+

aritmetico, con una banda

bassante di 1 GByte/s.

Il supporto nativo per

l’aritmetica complessa e la

Min

Min

Max1 FP/I

Add1

Add2 Max2

FP/I

capacità di eseguire una

+ - +

butterfly

ogni

ciclo

producono

ottimi

benchmarks su algoritmi

classici come una FFT da 1024 punti (5900 cicli verso 14400 su un C67 della Texas

Instrument).

La minimizzazione dei problemi dovuti ai ritardi dovuti alle interconnessioni su silicio è un

aspetto chiave per le architetture sviluppate su tecnologia DSP (Deep Submicron

Technology). Abbiamo sviluppato una semplice analisi dimensionale (descritta in [1]) che ha

facilitato la definizione della archiettura mAgic VLIW. Questa analisi dimensionale si focalizza

sulla selezione di un appropriato bilanciamento tra il parallelismo a livello di istruzione, la

frequenza di clock e la taglia delle memorie. Il bilanciamento assicura il controllo sui ritardi di

interconnessioni che sono confinate all’interno di ciascuna “tile” o che connettono a tile prime

vicine. Le connessioni globali residue sono mantenute in numero limitato, e filate su

dimensioni maggiori o maneggiate per mezzo della inserzione di stazioni di ripetizione.

operazioni di monitoraggio, diagnosi e controllo automatico (esempi: diagnosi acustica di

motori o caldaie, controllo di crociera di autoveicoli) oppure di mitigare gli effetti della

interazione con ambienti difficili (esempio: radio digitale in banda AM con modulazione

COFDM). Secondo la nostra visione, nelle predette applicazioni saranno anche combinate

tecniche di modellazione in tempo reale di fenomeni fisici (ad esempio modellazione fisica

della voce umana o degli strumenti musicali). DIOPSIS 740 e' una piattaforma di sviluppo

ideale per applicazioni di "intelligenza ambientale", in particolare per quanto riguarda la

componente audio e le applicazioni di beam-forming adattivo. La potenza di calcolo messa a

disposizione dal DSP (1 miliardo di operazioni floating-point al secondo), la precisione

numerica (40 bit floating point) e la integrazione con un controllore RISC ed un set di

periferiche dedicate alla gestione di un array di convertitori analogico-digitali consentono di

sviluppare applicazioni complete di intelligenza ambientale e modellazione fisica in tempo

reale di sistemi complessi. Al chip DIOPSIS è necessario aggiungere esternamente i soli

convertitori analogico digitali e, quando l’applicazione lo richieda, memorie esterne

aggiuntive. L’architettura è ottimizzata per applicazioni nel dominio della frequenza.

5. Conclusioni

mAgic VLIW DSP e DIOPSIS 740, unico sistema su silicio attualmente esistente a livello

mondiale che combini un DSP floating-point da 1 GFLOPS ed un controllore RISC a 32 bit

consentono la creazione di applicazioni consumer di intelligenza ambientale e modellazione

fisica. mAgic e DIOPSIS sono stati progettati in Italia grazie ad una interessante

combinazione di trasferimento tecnologico dai progetti INFN, alla creazione in Roma del

centro di progettazione di processori DSP del fabbricante di semiconduttori ATMEL, ed ai cofinanziamenti italiani ed europei.

Bibliografia

[1] P.S. Paolucci et al. “Janus: A gigaflop VLIW+RISC Soc Tile”, Hot Chips 15 IEEE Stanford

Conference (2003). http://www.hotchips.org

[2] R. Ho, K. Mai and M. Horowitz, “The Future of Wires”, Proc. IEEE, 89-4 (2001)490-504.

[3] D. Sylvester and K. Keutzer, “Impact of Small Process Geometries on Microarchitectures

in Systems on a Chip”, Proc. IEEE, 89-4(2001)467-489.

[4] L.P. Carloni, A.L. Sangiovanni-Vincentelli, "Coping with latency in SOC Design", IEEE

Micro 22-5 (2002) 24-35.

[5] A. Allan et al., “2001 Technology Roadmap for Semiconductors”, IEEE Computer 351(2002)42-53.

[6] W.J. Dally and S. Lacy, “VLSI Architectures: Past, Present and Future”, Proc. Advanced

Research in VLSI Conf., IEEE Press (1999)232-241.

[7] M.B. Taylor et al., “The Raw Microprocessor: A Computational Fabric for Software

Circuits and General-Purpose Programs”, IEEE Micro 22-2(2002)25-35.

[8] J. Ying Fai Tong et al. “Reducing Power by Optimizing the Necessary Precision Range of

Floating Point Arithmetic”, IEEE Trans. On VLSI Systems, 8-3 (2000)273-286.

[9] P. Faraboschi, G. Desoli, J.A. Fisher, “The Latest Word in Digital and Media Processing”,

IEEE Signal Processing Mag. 15-2(1998)59-85.

[10]

R.P. Clowell, J. O’Donnell, D.P. Papworth, P.K. Rodman, “Instruction Storage Method

with a Compressed Format Using a Mask Word”, U.S. Patent 5057837, (Oct 1991).

[11]

P.S. Paolucci, P. Kajfasz et al., “mAgic-FPU and MADE: A customizable VLIW core

and the modular VLIW processor architecture description environment”, Computer

Physics Communication 139(2001)132-143.

[12]

A. Bartoloni, P.S. Paolucci et al., “A Hardware Implementation of the APE100

Architecture”, Int. Journ. Mod. Phys. C 4(1993)969.

[13]

N. Cabibbo and P.S. Paolucci, “SIMD algorithm for Matrix Transposition”, Int. Journ.

Mod. Phys. C 6(1995)183.